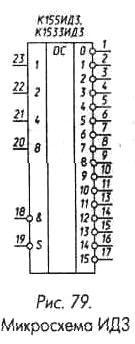

Микросхема ИДЗ (рис. 79) имеет четыре адресных входа 1, 2,4, 8, два инверсных входа стробирования S, объединенных по И, и 16 выходов 0-15. Если на обоих входах стробирования лог. 0, на том из выходов, номер которого соответствует десятичному эквиваленту входного кода (вход 1 - младший разряд, вход 8 -старший), будет лог. 0, на остальных выходах - лог. 1. Если хотя бы на одном из входов стробирования S лог. 1, то независимо от состояний входов на всех выходах микросхемы формируется лог. 1.

Микросхема ИДЗ (рис. 79) имеет четыре адресных входа 1, 2,4, 8, два инверсных входа стробирования S, объединенных по И, и 16 выходов 0-15. Если на обоих входах стробирования лог. 0, на том из выходов, номер которого соответствует десятичному эквиваленту входного кода (вход 1 - младший разряд, вход 8 -старший), будет лог. 0, на остальных выходах - лог. 1. Если хотя бы на одном из входов стробирования S лог. 1, то независимо от состояний входов на всех выходах микросхемы формируется лог. 1.

Наличие двух входов стробирования существенно расширяет возможности использования микросхем. Из двух микросхем ИДЗ, дополненных одним инвертором, можно собрать дешифратор на 32 выхода (рис. 80),

Функцию, обратную функции дешифраторов, выполняют шифраторы.

Функцию, обратную функции дешифраторов, выполняют шифраторы.

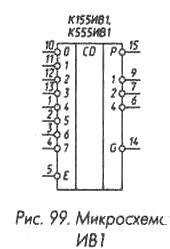

Микросхема ИВ1 - приоритетный шифратор (рис. 99). Она имеет восемь информационных входов 0-7 и вход разрешения Е. Выходов у микросхемы пять - три инверсных выходного кода 1,2,4; G -признака подачи входного сигнала и Р - переноса.

Если на всех информационных входах микросхемы лог. 1, на выходах 1,2,4, G - лог. 1, на выходе Р - лог. 0. При подаче лог. 0 на любой из информационных входов 0-7 на выходах 1,2, 4 появится инверсный код, соответствующий номеру входа, на который подан лог. 0, на выходе G'- лог. 0, что является признаком подачи входного сигнала, на выходе Р - лог. 1, которая запрещает работу других микросхем ИВ1 при их каскадном соединении. Если лог. 0 будет подан на несколько информационных входов микросхемы, выходной код будет соответствовать входу с большим номером.

2015-04-20

2015-04-20 427

427