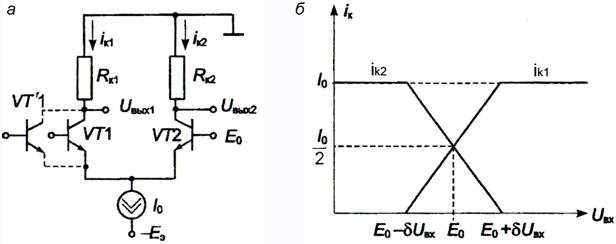

Основу схемы эмиттерно-связанная логика (ЭСЛ) составляет переключатель тока (рис. 3.14, а). В этой схеме транзисторы VT1 и VT2 образуют дифференциальный каскад, работающий в режиме переключения токов. Путем выбора величин резисторов RК1, RК2, тока I0 и уровня  в схеме обеспечиваются такие условия, что транзисторы работают в активном режиме. Тем самым обеспечивается повышенная скорость переключения из-за уменьшения избыточных зарядов, накапливаемых в базах транзисторов. На базу транзистора VT2 подается опорное напряжение Ео, которое имеет величину

в схеме обеспечиваются такие условия, что транзисторы работают в активном режиме. Тем самым обеспечивается повышенная скорость переключения из-за уменьшения избыточных зарядов, накапливаемых в базах транзисторов. На базу транзистора VT2 подается опорное напряжение Ео, которое имеет величину  Если

Если  , то оба транзистора открыты, и через каждый протекает ток iК=iК1=iК2=i0/2. Напряжение на эмиттерах

, то оба транзистора открыты, и через каждый протекает ток iК=iК1=iК2=i0/2. Напряжение на эмиттерах  . Известно, что в активном режиме ток коллектора очень сильно зависит от напряжения Uбэ:

. Известно, что в активном режиме ток коллектора очень сильно зависит от напряжения Uбэ:

. (3.5)

. (3.5)

Согласно этой формуле изменение Uбэ на величину dU = 2,3 jт (60 мВ при Т = 25 °С) приводит к изменению коллекторного тока на порядок. Поэтому, если напряжение на входе станет меньше Е0 на величину dU ≥ 0,06 В, то напряжение Uбэ1 = Uвх – UЭ тоже уменьшится, что приведет к резкому уменьшению тока iК1 (рис. 3.14, б), а так как суммарный ток транзисторов задан генератором тока I0 (iк1+ iк2 = I0), то ток iК2 возрастет, т. е. произойдет переключение тока в правое плечо схемы iк2 ≈ I0, iк1 ≈ 0). Транзистор VT1 будет закрыт и на первом выходе установится напряжение высокого уровня  , транзистор VT2 будет открыт, на втором выходе установится напряжение низкого уровня

, транзистор VT2 будет открыт, на втором выходе установится напряжение низкого уровня  . Если напряжение на входе увеличить относительно величины Е0 на dU, то произойдет переключение тока в левое плечо схемы (iк1 ≈ I0, iк2 ≈ 0,

. Если напряжение на входе увеличить относительно величины Е0 на dU, то произойдет переключение тока в левое плечо схемы (iк1 ≈ I0, iк2 ≈ 0,  ,

,  ). Таким образом, для переключения тока I0 из одного плеча в другое достаточно изменить входное напряжение на величину 2dU ≥ 0,12 В относительно уровня Е0.

). Таким образом, для переключения тока I0 из одного плеча в другое достаточно изменить входное напряжение на величину 2dU ≥ 0,12 В относительно уровня Е0.

Схема базового элемента ЭСЛ отличается от рассмотренной схемы переключателя тока тем, что она содержит в левом плече не один, а несколько транзисторов (VT1,VТ'1,... и т. д.), включенных параллельно, т. е. имеет не один, а несколько входов. При подаче на любой из входов сигнала  происходит переключение тока в левое плечо, а при наличии на всех входах сигналов

происходит переключение тока в левое плечо, а при наличии на всех входах сигналов  ток переключается в правое плечо. Следовательно, при снятии выходного напряжения с левого плеча схема выполняет операцию ИЛИ–НЕ, а при снятии сигнала с правого плеча операцию ИЛИ.

ток переключается в правое плечо. Следовательно, при снятии выходного напряжения с левого плеча схема выполняет операцию ИЛИ–НЕ, а при снятии сигнала с правого плеча операцию ИЛИ.

Рис. 3.14

При цепочечном включении логических элементов выходное напряжение предыдущего элемента является входным для последующего. При этом последующий элемент не должен переходить в режим насыщения при подаче на его вход логической единицы. С этой целью к выходам подключают эмиттерные повторители, благодаря которым выходные потенциалы схемы ЭСЛ снижаются на 0,7 В относительно потенциалов коллекторов VT1 и VT2. Поскольку эмиттерные повторители обладают низким выходным сопротивлением, то подключение к выходу схемы внешних нагрузок слабо влияет на работу схемы. Поэтому коэффициент разветвления для элемента ЭСЛ достигает 25.

Принципиальной особенностью микросхем ЭСЛ является питание от источника с заземленным плюсом. Такое включение позволило повысить помехоустойчивость схемы, так как в этом случае коллекторные шины питания делаются большого сечения, и уменьшается их сопротивление. В этом случае на коллекторной шине питания броски тока не создают значительного паразитного падения напряжения, которое воспринимается последующим логическим элементом как помеха. Повышению помехоустойчивости способствует также наличие двух заземляемых выводов: одного непосредственно от логического элемента, другого – от коллекторной шины эмиттерных повторителей.

Основным достоинством схем ЭСЛ является их высокое быстродействие, обусловленное прежде всего работой транзисторов в активном режиме и уменьшением времени перезаряда емкостных составляющих схемы за счет малого логического перепада. В настоящее время разработаны сверхбыстродействующие ЭСЛ-схемы с частотой переключения до 3 ГГц.

2015-05-13

2015-05-13 1776

1776