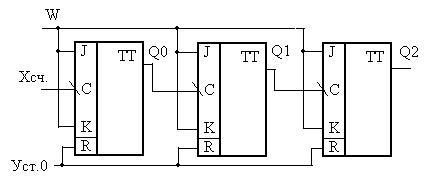

Рассмотрим пример трехразрядного счетчика:

Рис.27

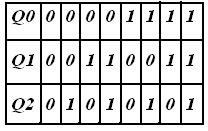

В этой логической схеме выход предыдущего триггера соединен с входом синхронизации следующего. При подаче сигнала W=1 каждый триггер представляет собой асинхронный Т-триггер, а вся схема - асинхронный суммирующий счетчик с последовательным переносом. Таблица истинности счетчика имеет вид.

Начальное состояние счетчика Q2 Q1 Q0 = 0 0 0,старший разряд кода Q2. Коэффициент пересчета кп =8. Если счетчик достигает состояния

Q2 Q1 Q0 = 1 1 1, то при подаче следующего сигнала на вход счетчика, он переходит в состояние Q2 Q1 Q0 = 0 0 0. Каждый триггер в счетчике переходит в состояние противоположное предыдущему по спаду сигнала на выходе предыдущего триггера.

К недостаткам счетчика с последовательным переносом относится зависимость времени задержки счетчика от его разрядности, что снижает его быстродействие.

2015-07-21

2015-07-21 1487

1487