Сигнали, які мікропроцесор видає на шину адреси або на шину даних, можуть призначатися великій кількості пристроїв, що своїми входами приєднані до цих шин. Але виходи МП - 80 витримують лише невелике навантаження струму - не більше 0,1 мА при сигналі високого рівня і 1,6 мА при сигналі низького рівня. Така навантажувальна здатність дозволяє підключати до виходів мікропроцесора не більше одного входу пристроїв ТТЛ. Тому на виходах ПІ А та ПІД мікропроцесора звичайно ставлять буферні підсилювачі, або, як їх називають, шинні формувачі.

У найпростішому випадку, коли треба пропускати сиг. Іпи тільки в одному напрямку (як це має місце для ША), замість спеціальних шинних формувачів можна використати звичайні інвертори (наприклад, ДНІ або ЛАЗ). Якщо інвертувати сигнал не треба, можна скористатися логічним елементом типу ЛП або поставити послідовно два інвертори.

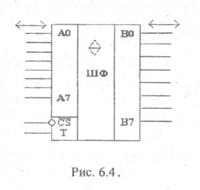

Якщо ж по шині даних сигнали повинні проходити в обох напрямках, то шинні формувачі мають бути двоспрямованими. Прикладом такого двоспрямованого шинного формувача може бути ІМС типуКР580ВА86 (рис. 6.4).

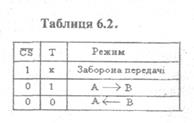

При CS = 1 виводи А і В знаходяться в третьому стані й ніякого проходження сигналу через схему немає. При CS=0 IMC активізується; сигнал Т визначає напрямок руху даних (табл. 6.2).

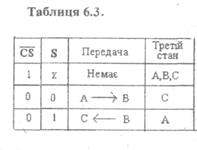

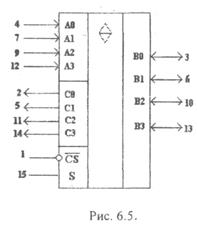

Дещо складніше працює шинний формувач типу К589АП16. Н відміну від попередньої ця ІМС керує ще й напрямком передачі. Бон є начебто перемикачем шини (рис. 6.5 та табл. 6.3), в якому сигнал S

визначає шлях передачі даних. ІМС К589АП16 використовується для обслуговування ОЗП, які мають розділені входи і виходи для Даних (наприклад типу КР 565). У цьому разі до загальної шини даних підключаються виводи групи В.

Виводи групи С підключаються до інформаційних входів ОЗП, а групи А - до виходів ОЗП. Запис до ОЗП відбувається при комбінації CS = 0; S —1, а читання з ОЗП при CS - 0; S =0. Для розширення розрядності по ПІД використовують по кілька подібних ГМС,-увімкнених паралельно. Варіантами описаних ІМС є КР580ВА87 та К589АШ6, які інвертують сигнали при їх передачі.

Дешифратори

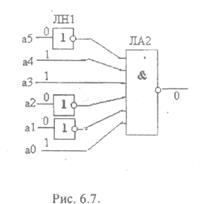

Найпростіший дешифратор, який відповідав би лише на одну задану адресну комбінацію, можна скласти з логічних ІМС (рис. 6.7). Такий дешифратор буде видавати на своєму виході сигнал низького рівня при певній адресній комбінації, наприклад, при аО - а5, що дорівнює 01100 Ь

Складніше працюють дешифратори з кількома виходами. Так, наприклад, дешифратор типу К155ИД4 може працювати в режимі,

коли за трьома розрядами адреси він видаватиме активний (низький)

рівень вихідної напруги на один із восьми своїх виходів (дешифратор "1 із 8"). Дешифратор типу К155ИДЗ виконує дешифрування за чотирма розрядами адреси на 16 виходів ("1 із 16").

Розширення пам'яті

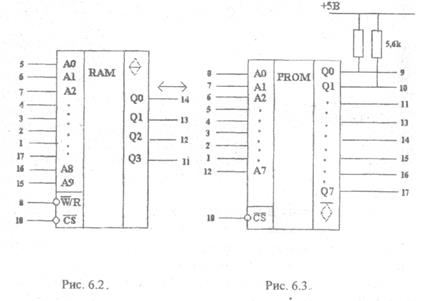

Часто об'єм пам'яті однієї МС ОЗП або ПЗП виявляється недостатнім як за розрядністю по

ПІД так і за розрядністю по ША. Тому подібні ІМС об'єднуються в групи, Ця операція має назву розширення пам'яті.

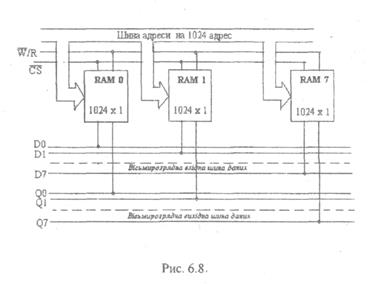

Горизонтальне розширення пам 'яті - збільшення розрядності по шині даних (на прикладі ІМС типу КР565РУ2).

Розряди ША та керуючі сигнали CS і W/R подаються на всі ІМС паралельно (рис. 6.8). Інформаційні входи dj підключаються до провідників вхідної ПІД - кожний вхід до свого і-того провідника. Так

само підключається вихідна ПІД. Кількість розрядів ШД може бути довільною і відповідає кількості корпусів ІМС.

Вертикальне розширення пам 'яті - збільшення розрядності

по шині адреси

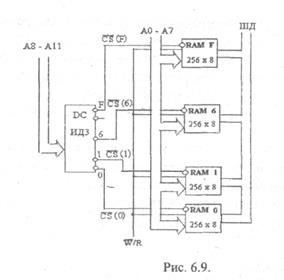

У розглянутих вище ОЗП та ПЗГТ розрядність адреси складає 9 - 10 розрядів, тоді як у МП-80 ША має лише 16. Недостатні розряди можна додагга шляхом вертикального розширення. Розглянемо принцип вертикального розширення на прикладі ОЗП, які мають по 8 розрядів адреси та 8 розрядів даних (256 х 8). Розширимо адреси до 12 розрядів (рис. 6.9). Кількість адрес збільшиться до 4096. Для цього будуть потрібні 16 корпусів подібних ІМС. Кожний з ОЗП має 256 молодших розрядів адреси від 00 до FF, але може бути зздіяний лише при CS =0.

Дешифратор "1 із 16" (наприклад, типу ИДЗ) виробляє CS(F) та активізує цим сигналом ОЗП RAM F тільки при значення старших бітів адреси А8 - All = 11112 = F. Корпус RAM 6 буде задіяний адресною комбінацією А8 - А11 = 01102 = 6 тощо.

Кількість ОЗП може бути й меншою від 16. Якщо, наприклад, RAM 8 -RAM F відсутні, то адреси, що починаються з 8 до F, будуть "мертвими"-вони не відповідатимуть реально існуючим коміркам пам'яті. Якщо ж ША 16-розрядна, то найстарші біти адреси А12 - А15 залишаться

незадіяними і можуть бути довільними. Наприклад, комірка пам'яті з адресою 1АС буде "відгукуватися" на адресу 01АС і на адресу В1 АС.

Організація звернення до пам 'яті або до зовнішніх пристроїв

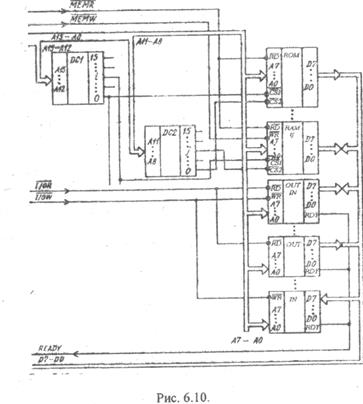

На рис. 6.10 зображено систему, що складається з одного модуля ПЗП на 256 комірок пам'яті та 255 модулів ОЗП, кожний з 8 розрядами адреси і 8 розрядами даних (256x8), а тако із можливістю звернення до 256 зовнішніх пристроїв. Усе поле пам яті при 16-розрядній ША складає 64 кбайт (65536 адрес по 8 бітів даних). З них 256 наймолодших адрес призначено для ПЗП (0000 -OOFF), а решта - 65280 - для ОЗП (0100 - FFFF).

Вибір комірки пам'яті усередині кожного модуля здійснюється за 8 молодшими розрядами ША (АО - А7). Ці коди молодших адрес подаються на всі модулі одночасно.

Вибір потрібного модуля пам'яті відбувається за старшими (А8 - А15) розрядами адреси шляхом одночасної подачі сигналів низького рівня на входи С81таС82,якієу кожному модулі ОЗП та ПЗП. Тільки при одночасній подачі сигналів низького рівня на ці входи відповідний модуль буде задіяний. Ці керуючі сигнали формуються двома 4-розрядними дешифраторами DC1 та DC2. При подачі 4-розрядного двійкового коду на адресні входи дешифратора на одному з 16 його виходів з'явиться сигнал низького рівня ("1 із 16"). "Старший"

дешифратор DC1 по розрядах А15 - А12 обирає одну групу, що складається з 16 модулів (і-ту групу), подаючи на її входи CS1 сигнал дозволу низького рівня. Другий ("молодший") дешифратор DC2 здійснює вибір модуля всередині групи. За розрядами All - А8 він активізує всі j-ті модулі кожної групи. У результаті активізованим буде j-тий модуль і-тої групи. Усього можливо 16 х 16 таких комбінацій, а отже, вибір одного з 256 модулів пам'яті.

Вибір між читанням та записом здійснюється за сигналами MEMR і MEMW. Якщо обидва ці сигнали мають високий логічний рівень, то ані читання, ані запису не відбувається і всі модулі пам'яті відключені від шини даних (знаходяться в третьому стані). Модуль ГОП робить тільки на читання і тому сигнал MEM W до нього не підведено.

Зовнішні пристрої введення/виведення керуються сигналами Г/ OR та І / OW і можуть бути задіяні лише тоді, коли один із цих сигналів має низький рівень. Звернення до пристроїв уведення відбувається за сигналом І / OR = 0, а до пристроїв виведення сигналом I/OW = 0. Усього можливе підключення 256 пристроїв введення/виведення (портів). При роботі із зовнішніми пристроями пам'ять буде відключеною, бо активним може бути лише один Із сигналів MEMR, MEMW, F/OR або F/QW.

Якщо одні порти працюють тільки на введення, а інші тільки на виведення, то можна підключати по 256 таких портів кожного типу. Вибір конкретного порту здійснюється за однобайтовою адресою АО - А7.

Для спряжіння мікропроцесора з повільно діючими зовнішніми пристроями використовується сигнал готовності READY, що виробляється цими пристроями як ознака їх готовності до роботи. Відсутність сигналу готовності переводить мікропроцесор у стан очікування, в якому він перебуває, доки на лінії READY не встановиться сигнал високого рівня.

2015-10-16

2015-10-16 2555

2555