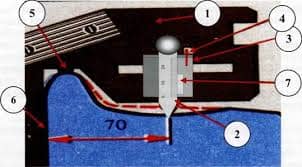

На рисунке показана внутренняя структура ЦСП С6x. ЦСП можно условно разделить на несколько частей:

· Ядро процессора.

· Области памяти данных и памяти команд.

· Размещенная на кристалле периферия. Все эти части связаны между собой двумя контроллерами – памяти команд или кэш-памяти и памяти данных. Эти блоки связывают ядро ЦСП и банки памяти (с их специфической конфигурацией и доступом) с традиционными шинами, к которым подключаются периферийные модули и внешние устройства.

Рассмотрим подробнее периферийные устройства ЦСП TMS320С6000.

Контроллер ПДП. Устройство предназначено для передачи данных из памяти в память без участия центрального процессора. Контроллер ПДП имеет четыре основных программируемых и пять дополнительных каналов. Кроме того, контроллер ПДП используется при начальной загрузке программы в память ЦСП при старте (bootloader).

Хост «Порт-интерфейс» (ХПИ). ХПИ используется как для обмена данными с управляющим контроллером, так и для асинхронного обмена. ХПИ – это 16-разрядный параллельный порт, который обеспечивает прямой доступ к памяти ЦСП. При этом ЦСП является управляющим устройством для данного интерфейса, что существенно упрощает процедуру доступа. ЦСП может обмениваться информацией, как через внутреннюю, так и через внешнюю память. Кроме того, ЦСП может иметь прямой доступ к большинству устройств размещенной на кристалле периферии.

Шина расширения (ШР). ШР является расширением как ХПИ, так и ИВП (см. ниже). С использованием ШР можно реализовать 32-разрядный ХПИ, который будет работать аналогично штатному 16-разрядному. ШР также может реализовать синхронный протокол обмена между хост ЦСП и ЦП, что дает возможность прямого подключения к большому набору стандартных шин хост ЦСП. Также к шине расширения могут быть подключено синхронное FIFO и асинхронные периферийные устройства.

Интерфейс внешней памяти (ИВП). ИВП это специальный блок, предназначенный для обмена данными с внешней памятью и быстродействующими внешними устройствами. ИВП может принимать запросы на обмен с внешней памятью от трех: контроллеров памяти данных, программной памяти-КЭШ и ПДП. Поскольку сам ЦСП – очень скоростное устройство, то ИВП не только выводит наружу классическую шину, но и имеет специальные сигналы для непосредственного подключения быстродействующего синхронного внешнего ОЗУ как динамического (SDRAM), так и статического (SBSRAM). Кроме того, к ИВП можно подключить и обычное статическое ОЗУ, ПЗУ, FIFO и другие устройства.

Начальный загрузчик. ЦСП TMS320C62x и TMS320C67x могут иметь множество режимов начальной загрузки, которые определяют, что именно будет делать ЦСП после сброса при подготовке к инициализации. Они могут включать загрузку программы с внешнего ПЗУ через ИВП или загрузку программы через ХПИ/ШР из внешнего устройства.

Многоканальный буферизованный последовательный порт МКБПП. Это последовательный скоростной порт, базирующийся на стандартном последовательном порте, как и в ЦСП других серий. Он имеет возможность читать и записывать данные в память без участия центрального процессора через контроллер ПДП. Кроме того, у него существуют многоканальные расширения, совместимые со стандартами El, Tl, SCSA и MVIP.

Отметим следующие функциональные возможности последовательного порта:

· полнодуплексная работа;

· двойная буферизация данных (позволяет поддерживать непрерывность потока);

· независимые тактовые частоты и схемы синхронизации для приема и передачи данных;,

· прямое подключение микросхем аналоговых интерфейсов, микросхем

· ЦАП и АЦП с последовательным интерфейсом.

МКБПП, по сравнению со стандартным последовательным портом, имеет дополнительные возможности:

· прямое подключение к шинам;

· многоканальный обмен при количестве каналов до 128;

· переменный размер данных 8, 12, 16, 20, 24 и 32 бита;

· встроенное u-Law и А-Law компандирование;

· возможность передачи первым старшего или младшего разряда данных;

· программируемая полярность сигналов синхронизации и тактовых сигналов данных;

· гибкое программирование внутренних тактовых импульсов и синхронизации.

Таймер. ЦСП серии TMS320C6000 имеют два 32-разрядных таймера, которые могут быть использованы для:

· задания временных событий;

· реализации счетчиков;

· генерации импульсов

· прерывания ЦСП;

· посылки синхроимпульсов в контроллер ПДП.

Селектор прерываний. Периферия ЦСП TMS320C6000 может иметь до 32-х источников прерываний. ЦП имеет возможность обрабатывать 12 прерываний. Селектор прерываний дает возможность выбора тех 12 прерываний, которые будут использоваться, и также дает возможность смены полярности внешних входов прерываний.

«Спящие» режимы. Логика снижения потребляемой мощности позволяет снимать тактовые сигналы с элементов ЦСП для снижения энергопотребления. Несмотря на свое предназначение для базовых станций, ЦСП TMS320C6000 также имеют режимы снижения энергопотребления. КМОП схемы в основном потребляют энергию в момент переключения, и чем выше частота работы, тем больше это потребление. При включении «спящих» режимов у ЦСП снимается тактовая частота сначала с ядра ЦСП, затем с периферии, размещенной на кристалле, и последний «третий» режим снимает тактовую частоту практически со всего кристалла, в том числе и с блока умножения частоты. ЦСП имеет встроенный умножитель частоты с возможностью умножения внешней тактовой частоты на 2 и на 4, что делает возможным работу с низкой входной частотой и упрощает проектирование.

2014-02-09

2014-02-09 857

857