Структурный синтез дискретных устройств с памятью принципиально ничем не отличается от структурного синтеза дискретных устройств без памяти.

На этапе абстрактного синтеза получены условия функционирования схем управления памятью и формирования выходных сигналов для бесконтактных ДУ.

Построение по этим условиям схем блока формирования выходных сигналов и блока управления памятью (блока промежуточных элементов) является решением задачи структурного синтеза дискретных устройств без памяти. Методы решения задачи синтеза ДУ без памяти были рассмотрены ранее, здесь дадим лишь некоторые замечания и приведем примеры.

Результатом выполнения этапа структурного синтеза ДУ должно явиться построение функциональной схемы для бесконтактных дискретных устройств.

Одним из важнейших требований, которое должно выполняться на этапе структурного синтеза, является получение наиболее простой (минимальной) структуры дискретного устройства. Сложность структуры ДУ в целом зависит от трудности технической реализации каждой из логических функций, полученных на этапе абстрактного синтеза и отражающих условия функционирования ДУ. Поэтому логические функции, отражающие условия функционирования выходных сигналов и элементов памяти должны быть минимизированы, а также приведены к виду, наиболее удобному для их реализации на выбранной серии логических элементов.

Методы минимизации логических функций и приведения их к виду, удобному для реализации, были рассмотрены ранее.

Отметим, что наиболее предпочтительными методами минимизации логических функций в инженерной практике являются метод с использованием решетки соседних чисел и обобщенных кодов, применяемый для функций до четырех переменных, и метод поразрядного сравнения рабочих и запрещенных наборов с использованием восьмеричной системы счисления – для функций более четырех переменных.

Схемы функционирования каждого выхода и элемента памяти синтезируют отдельно, считая, что все необходимые сигналы, как внешние, так и обратной связи, и их инверсии имеются. При этом схемы блока управления памятью и блока формирования выходных сигналов должны рассматриваться как схема единого многовыходного дискретного устройства с памятью, что дает дополнительные возможности по оптимизации структуры синтезируемого ДУ за счет объединения отдельных функциональных частей схемы.

Рассмотрим примеры.

По условиям функционирования, полученным в примере 3.1, произведем структурный синтез ДУ.

Условия их функционирования, полученные в подразделе 3.5:

u = y (yaв) = 2, 4, 6, [0, 1, 5];

z (yaв) = 4, [0, 1, 2, 5, 6].

Так как число переменных 3, то для минимизации логических функций воспользуемся 3-разрядной решеткой соседних чисел:

u = y (yab) = (4 v 6) v (2 v 6 v 3 v 7) = (1-0) v (-1-);

z (yab) = 4 = 100

Реализуем данное ДУ на бесконтактных элементах, например на интегральных элементах К155 серии, используя в качестве элементов памяти задержки на логических элементах.

Используя предыдущие результаты, запишем тупиковые ДНФ функций возбуждения и выходов в принятом обычно для БДУ виде:

;

;  .

.

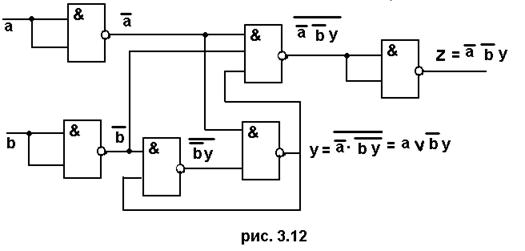

Так как в серии К155 основной логической схемой является схема И-НЕ, то полученные выражения преобразуем к виду, удобному для реализации на элементах И-НЕ, пользуясь правилом двойной инверсии:

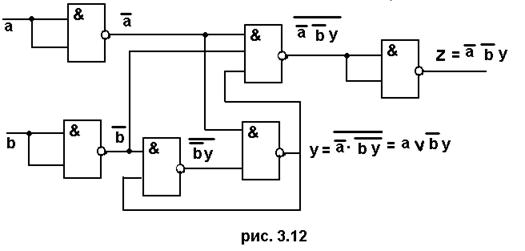

Функциональная схема ДУ, построенная по этим выражениям, представлена на рисунке 3.12.

Функциональная схема ДУ, построенная по этим выражениям, представлена на рисунке 3.12.

Итак, решением примера 3.1 на бесконтактных элементах И-НЕ является

функциональная схема, изображенная на рисунке 3.12.

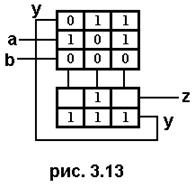

Реализуем данное ДУ на ПЛМ. В результате абстрактного синтеза получили:

у (у,a,в) = 2, 4, 6, [0, 1, 5];

z (у,a,в) = 4, [0, 1, 2, 5, 6].

Для реализации функции на ПЛМ минимизацию проводить не обязательно.

Перейдем к СДНФ:

.

.

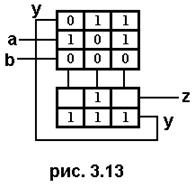

Реализация этих функций на ПЛМ представлена на рисунке 3.13.

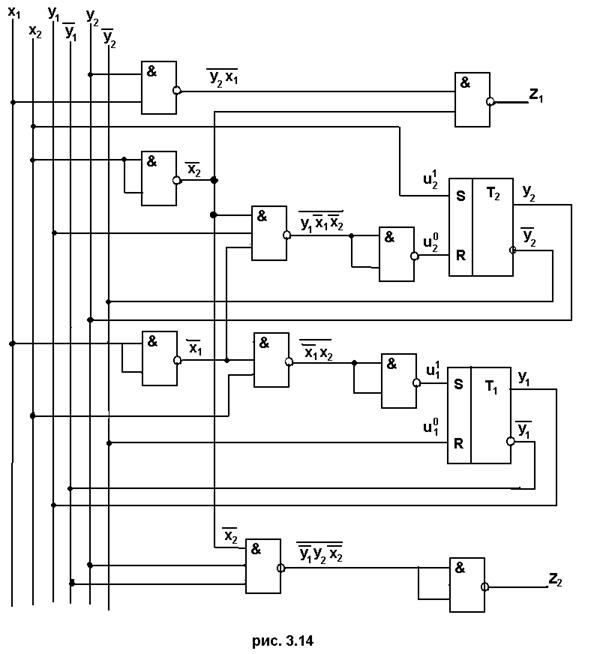

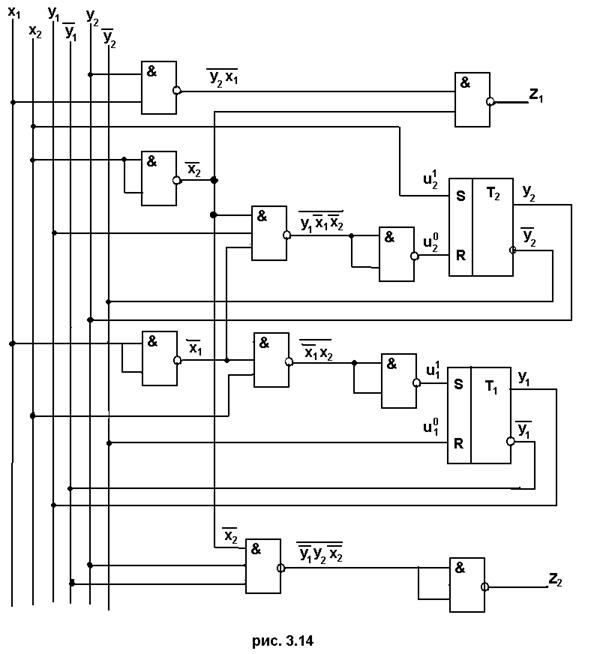

Произведем структурный синтез ДУ по условиям функционирования, полученным в примере 3.2, имея в виду, что в качестве элементов памяти используются триггеры с раздельными входами.

Определенные в предыдущем параграфе логические функции

z 1, z 2, u 11, u 10, u 21, u 20 содержат не более четырех переменных.

Проведя минимизацию логических функций с использованием решетки соседних чисел, получим тупиковые ДНФ функций выходов и функций возбуждения входов элементов памяти:

Полученные выражения преобразуем к виду, удобному для реализации на элементах И-НЕ:

Функциональная схема, построенная по этим выражениям (Рисунке 3.14) и есть решение примера 3.2.

Построением функциональной схемы оканчивается этап структурного синтеза дискретных устройств с памятью.

Далее следует этап физического синтеза.

;

;  .

.

Функциональная схема ДУ, построенная по этим выражениям, представлена на рисунке 3.12.

Функциональная схема ДУ, построенная по этим выражениям, представлена на рисунке 3.12.

.

. Произведем структурный синтез ДУ по условиям функционирования, полученным в примере 3.2, имея в виду, что в качестве элементов памяти используются триггеры с раздельными входами.

Произведем структурный синтез ДУ по условиям функционирования, полученным в примере 3.2, имея в виду, что в качестве элементов памяти используются триггеры с раздельными входами.

2014-02-13

2014-02-13 1166

1166