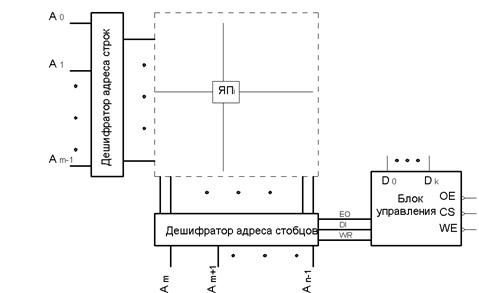

Типичный вариант структурного построения микросхемы статического ОЗУ приведен на рис. 5.1.

Рис.5.1. Структурная схема статического ЗУ 3D.

На рис. 5.1 приняты следующие обозначения:

-  - n адресных входов,

- n адресных входов,

-  - вход разрешения считывания данных,

- вход разрешения считывания данных,

-  - вход выбора микросхемы,

- вход выбора микросхемы,

-  - вход разрешения записи,

- вход разрешения записи,

-  - вход/выход данных.

- вход/выход данных.

EO, DI, WR – внутренние сигналы, вырабатываемые блоком управления.

Доступ к ЯП матрицы накопителя осуществляется с помощью двух дешифратор адреса столбцов и строк.

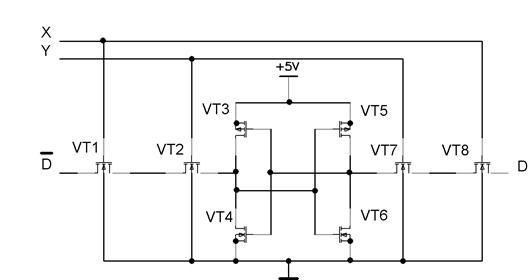

Упрощенная структурная схема элемента ЯП представлена на рис. 5.2.

Комплементарные транзисторы VT3…VT6 образуют триггер. Последовательно включенные транзисторы VT1, VT2 и VT7, VT8 образуют элементы И. В случае, если данная ячейка не выбрана (на обеих шинах X и Y или на одной из них установлен низкий уровень), ЯП находится в режиме хранения информации. При одновременном

появлении высокого уровня на обеих шинах X и Y данная ячейка оказывается выбранной и в зависимости от состояния входов  ,

,  ,

,  производится запись

производится запись

Рис. 5.2. Упрощенная структурная схема элемента ЯП статического ОЗУ

или считывание лог. состояния ячейки. В частности, если сигналы  (chip select) – выбор микросхемы низкого уровня,

(chip select) – выбор микросхемы низкого уровня,  (output enabled) или RD (read data) – переключения вход\выход - высокого уровня,

(output enabled) или RD (read data) – переключения вход\выход - высокого уровня,  (written enabled) или WR (written read)– разрешения записи низкого уровня, логический уровень, установленный на информационном входе D микросхемы через специальные внутренние буферные усилители записи блока управления поступает на входы\выходы

(written enabled) или WR (written read)– разрешения записи низкого уровня, логический уровень, установленный на информационном входе D микросхемы через специальные внутренние буферные усилители записи блока управления поступает на входы\выходы  элемента ЯП. При этом, если состояние триггера элемента ЯП не соответствует приходящим сигналам, на его плечах на короткое время устанавливается напряжение равное примерно половине напряжения питания, что не достаточно для поддержания нижнего транзистора одного из плеч в открытом состоянии, этот транзистор закрывается и триггер устанавливается в состояние соответствующее приходящим сигналам.

элемента ЯП. При этом, если состояние триггера элемента ЯП не соответствует приходящим сигналам, на его плечах на короткое время устанавливается напряжение равное примерно половине напряжения питания, что не достаточно для поддержания нижнего транзистора одного из плеч в открытом состоянии, этот транзистор закрывается и триггер устанавливается в состояние соответствующее приходящим сигналам.

В случае необходимости считывания информации сигнал  устанавливается низкого уровня, а сигнал

устанавливается низкого уровня, а сигнал  - высокого уровня. При этом внутренние буферные усилители выходных сигналов внутри блока из третьего состояния переходят в активное состояние, а к входам\выходам

- высокого уровня. При этом внутренние буферные усилители выходных сигналов внутри блока из третьего состояния переходят в активное состояние, а к входам\выходам  элемента ЯП подключаются входы этих усилителей. Выходы внутренних буферных усилителей записи находятся при этом в третьем состоянии. И состояние триггера элемента ЯП передается на соответствующий вывод D микросхемы. В одной ЯП содержится k таких элементов.

элемента ЯП подключаются входы этих усилителей. Выходы внутренних буферных усилителей записи находятся при этом в третьем состоянии. И состояние триггера элемента ЯП передается на соответствующий вывод D микросхемы. В одной ЯП содержится k таких элементов.

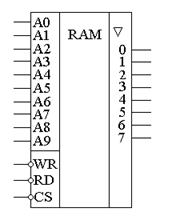

Пример условного обозначения ОЗУ на схемах электрических принципиальных приведен на рис. 5.3.

Рис. 5.3. Пример условного обозначения ОЗУ статического типа

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того, они применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

2014-02-13

2014-02-13 1258

1258