Страничное управление памятью (Paging), как уже было показано в разделе 1.1, является средством организации виртуальной памяти с возможностью подкачки страниц по запросу (Demand-Paged Virtual Memory). В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация работает со страницами одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может в ней и отсутствовать (она может быть выгружена на внешнюю, например, дисковую, память). При обращении к отсутствующей в физической оперативной памяти странице процессор генерирует исключение #PF (Page Fault – отказ страницы), а программный обработчик этого исключения (обычно являющийся частью операционной системы) должен получить необходимую информацию для загрузки – «подкачки» страницы с внешнего носителя (обычно диска). Страницы не связаны напрямую с логической структурой данных или программ. В отличие от сегментов, которые являются модулями кодов и данных, а соответствующие селекторы этих сегментов – логическими идентификаторами этих модулей, страницы представляют одинаковые по размеру фрагменты этих модулей. Так как программам и данным присуще свойство локальности – каждая последующая ссылка на коды или данные статистически расположена вблизи к уже выбранным кодам и данным – в физической оперативной памяти одновременно обычно хранят небольшие фрагменты соответствующих сегментов, необходимые активным процессам и задачам. Страничная организация памяти и позволяет реализовать эту возможность. В процессоре i386, в котором впервые появилась возможность страничной организации памяти, могли использоваться страницы размером лишь в 4 Кбайта. Начиная с Pentium’а, появилась возможность использования страниц размером 4 Мбайта, а, начиная с Pentium Pro, адресная шина процессора увеличилась до 36 разрядов (адресуемое пространство до 64 Гбайт), и появилась возможность использования страниц размеров в 2 Мбайта.

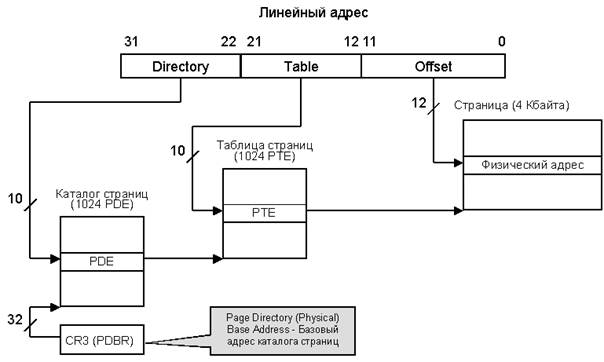

Базовый механизм страничного управления памятью использует двухуровневую табличную трансляцию линейного адреса в физический (рисунок 1.9).

Рисунок 1.9 – Базовый механизм страничного преобразования

Механизм преобразования включает в себя три этапа: каталог страниц (Page Directory), таблицы страниц (Page Table) и собственно страницы (Page Frame). Механизм страничного преобразования включается установкой бита PG = 1 в регистре CR0. В регистре CR2 хранится линейный адрес отказа (Page Fault Linear Address) – адрес в памяти, по которому был обнаружен последний отказ страницы. В регистре CR3 хранится физический адрес каталога страниц (Page Directory Physical Base Address). Младшие 12 бит этого регистра всегда нулевые, так как каталог всегда выравнивается по границе страницы.

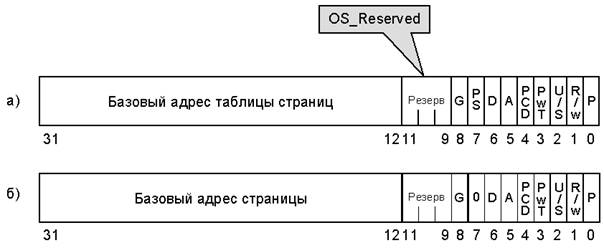

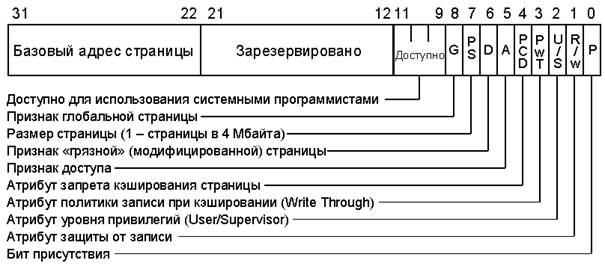

Каталог страниц размером 4 Кбайта содержит 1024 32-битных записи PDE (Page Directory Entry). Структура записи PDE показана на рисунке 1.10а.

Рисунок 1.10 – Структура элементов страничного преобразования

а – строка каталога, б – строка таблицы страниц

Из рисунка видно, что в каждой строке содержится 20 старших разрядов адреса таблицы страниц (младшие биты адреса всегда равны нулю, так как адрес таблицы всегда выровнен по границе страницы) и набор атрибутов таблицы страниц. Значения атрибутов показаны в таблице 1.5. Индексом поиска в каталоге страниц являются 10 старших разрядов линейного адреса (22 – 31).

Таблица страниц также состоит из 1024 строк PTE (Page Table Entry). Формат записей в строках PTE (рисунок 1.10б) аналогичен предыдущему, но вместо базового адреса таблицы страниц он содержит базовый физический адрес страницы (Page Frame Address). Наборы атрибутов в записях практически совпадают (исключение – бит 7). Индексом поиска в таблице страниц являются следующие 10 разрядов линейного адреса (12 – 21). Физический адрес операнда получается из адреса страницы, взятого из таблицы страниц и младших 12 разрядов линейного адреса (смещения внутри страницы). 02.12.14

Таблица 1.5 – Значение атрибутов строк каталога и страниц

| Бит | Обозначение | Назначение |

| P (Present) | Бит присутствия. P = 1 означает возможность использования данной строки для трансляции адреса. Для текущего исполняемого кода бит присутствия PDE должен быть установлен. Программный код не должен изменять его «на лету». Если P = 0, то все остальные биты доступны операционной системе. В частности, они могут использоваться для указания местонахождения данной страницы. | |

| R/W (Read/Write) [W (Writable)] | Это атрибут защиты от записи. Атрибут в строке каталога страниц относится ко всем страницам, на которые ссылается данная строка через таблицу второго уровня. Атрибут в строке таблицы страниц относится к соответствующей странице памяти. Права доступа, определяемые битами 1 и 2, приведены в таблице 1.6. Если атрибуты защиты в PDE и PTE различны, то результирующее значение атрибутов доступа определяются таблицей 1.7. Защита на уровне страниц включается установкой бита WP (Write Protect) в управляющем регистре CR0. При аппаратном сбросе этот бит обнуляется. | |

| U/S (User/Supervisor) [ U (User)] | Этот атрибут определяет два уровня привилегий: пользователь (User) и супервайзер (Supervisor). Пользователю соответствует уровень привилегий 3, супервайзеру – уровни 0, 1 и 2. Подробности приведена в таблицах 1.6 и 1.7. | |

| PWT (Page Write Through) | Этот атрибут определяет политику записи при кэшировании. | |

| PCD (Page Cache Disable) *) | Этот атрибут запрещает кэширование памяти для обслуживаемых страниц или таблиц. (Атрибут действителен, начиная с процессоров i486). | |

| A (Accessed) *) | Признак доступа. Этот бит устанавливается перед любым обращением (чтением или записью) по адресу, в преобразовании которого участвует данная строка. | |

| D (Dirty)*) | Признак, которым помечается «грязная» страница (в которую была осуществлена запись). Этот бит устанавливается перед операцией записи, в преобразовании которой участвует данная строка. | |

| PS (Page Size) | Этот атрибут задает размер страницы (только в PDE). При PS = 0 страница имеет размер 4 Кбайта. Значение PS = 1 используется в расширениях PAE (Page Size Extension – расширение размере страницы) и PSE (Physical Address Extension – расширение физического адреса), которые будут описаны ниже. | |

| В строке таблицы страниц (PTE) этот атрибут не используется. |

Таблица 1.5 – Значение атрибутов строк каталога и страниц (продолжение)

| Бит | Обозначение | Назначение |

| G (Global) | Этот атрибут действителен для процессоров, начиная с Pentium Pro. Он определяет глобальность страницы – позволяет пометить страницы глобального использования (например, страницы ядра операционной системы). При установленном бите PGE в управляющем регистре CR4 строки PDE и PTE с указателями на глобальные таблицы не будут аннулироваться в буфере ассоциативной трансляции TLB (Translation Lookaside Buffers – аппаратный кэш, в котором хранятся последние использованные PDE и PTE) при загрузке CR3 или при переключении задач, что ускоряет обслуживание виртуальной памяти. | |

| 9-11 | OS_Reserved | Это поле может использоваться операционной системой по своему усмотрению. Например, там может храниться информация о «возрасте» страницы, необходимая для реализации замещения страницы по алгоритмы LRU (Least Recently Used – наиболее долго не используемая страница замещается первой). |

| *) | Биты P, A и D модифицируются процессором аппаратно в заблокированных шинных циклах. При их программной модификации в многопроцессорных системах необходимо использовать префикс LOCK, гарантирующий сохранение целостности данных. |

Таблица 1.6 – Защита на уровне страниц

| U/S (U) | R/W (W) | Разрешено при PL = 3 | Разрешено при PL = 0, 1, 2 |

| Нет | Чтение/Запись | ||

| Нет | Чтение/Запись | ||

| Только чтение | Чтение/Запись | ||

| Чтение/Запись | Чтение/Запись |

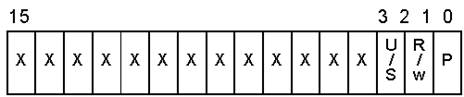

Механизм страничного управления при обращении к памяти может порождать исключение #PF. Оно возникает при обращении к отсутствующей (не представленной) странице или при нарушении прав доступа, определяемых уровнем привилегий и битами U и W. Для идентификации причины отказа в стек помещается 16-битный код ошибки, формат которого приведен на рисунке 1.11. Здесь названия битов совпадают с атрибутами строк, но их назначение другое. Бит U/S указывает, при каком уровне привилегий произошел отказ (1 – уровень пользователя, 0 – супервайзера). Бит W/R указывает, при выполнении какой операции произошел отказ (0 – при чтении, 1 – при записи). Бит Р указывает на причину отказа (Р=1 – отсутствие страницы, Р=0 – нарушение защиты). Биты, помеченные Х, не используются.

| Проверка защиты на уровне страниц выполняется после всех проверок защиты на уровне сегментов. Если при попытке доступа к памяти сработала защита сегментов, то проверка на уровне страниц уже не выполняется. |

Таблица 1.7 – Комбинация атрибутов защиты

| PDE | PTE | Результат | |||

| U | W | U | W | U | W |

Рисунок 1.11 – Формат кода ошибки при отказе страницы

Если при каждом обращении к памяти процессор обращался бы к двум таблицам, расположенным в оперативной памяти, это существенно снизило бы производительность системы. Для предотвращения такого замедления в процессоре имеется буфер ассоциативной трансляции TLB (Translation Lookaside Buffer) для хранения активно используемых строк таблиц страниц.

В процессорах i386 и i486 этот буфер представляет собой ассоциативный кэш на 32 строки таблиц трансляции. Такой размер кэша позволяет хранить информацию для трансляции 128 Кбайт памяти. Для большинства мультизадачных применений это дает 98% кэш-попаданий. В 2% случаев требуются дополнительные обращения к таблицам.

В процессорах Pentium имеются раздельные TLB для инструкций и данных. В Pentium Pro и позже эти буферы разделены и по размеру страниц (4 Кбайта и 2 Мбайта/4 Мбайта).

Работа механизма страничного преобразования выглядит следующим образом:

- если страничное управление разрешено (бит PG в регистре CR0 установлен в 1), блок страничного преобразования получает 32-битный линейный адрес от блока сегментации,

- старшие 20 разрядов полученного 32-битного адреса сравниваются со значениями, хранящимися в TLB,

- в случае кэш-попадания по начальному адресу страницы, полученному из TLB, вычисляется физический адрес и выводится на шину адреса,

- если соответствующей строки в TLB нет, выполняется чтение строки из страничного каталога,

- если строка имеет бит Р = 1 (таблица присутствует в памяти), в ней устанавливается бит доступа А и выполняется чтение указанной ею строки из таблицы второго уровня,

- если и в этой строке бит Р = 1, процессор обновляет в ней биты A и D, вычисляет физический адрес страницы и выполняет обращение по этому адресу,

- если на каком-либо из этапов встречается Р = 0, вырабатывается исключение #PF, обработчик которого должен загрузить востребованную страницу в оперативную память; так как это исключение имеет тип «отказ» (Fault), после его успешной обработки повторяется запрос доступа к той же ячейке памяти

После генерации процессором исключения #PF операционная система должна выполнить следующие действия:

- если необходимо, скопировать страницу с дискового накопителя в физическую память,

- загрузить адрес страницы в таблицу страниц или в каталог страниц,

- установить в обновленном элементе таблицы бит присутствия (Р), а также биты доступа (А) и «грязности» (D),

- аннулировать текущий PTE (элемент таблицы страниц) в буфере ассоциативной трансляции,

- вернуться из обработчика отказа страницы и возобновить работу прерванной программы или задачи.

Буферы ассоциативной трансляции TLB программно невидимы для прикладных задач (CPL > 0). С этими буферами может работать только операционная система с CPL = 0. Операционная система должна корректно сгенерировать начальные таблицы трансляции и обрабатывать исключения отказов. При изменении таблиц трансляции, а также при изменении бита присутствия Р в любых таблицах система должна аннулировать буферы ассоциативной трансляции TLB частично или полностью. Очистка всех ассоциативных буферов происходит при загрузке управляющего регистра CR3, выполняемой принудительно или при переключении задач. (Если установлен бит PGE – Page Global Enable в управляющем регистре CR4, строки в TLB, относящиеся к глобальным страницам, не аннулируются.)

Для изменения отображения одиночной страницы очистка TLB может осуществляться инструкцией INVLPG (Invalidate TLB Entry), которая, если возможно, очистит строку конкретной страницы в TLB, но может обновить и весь буфер, если такой возможности нет.

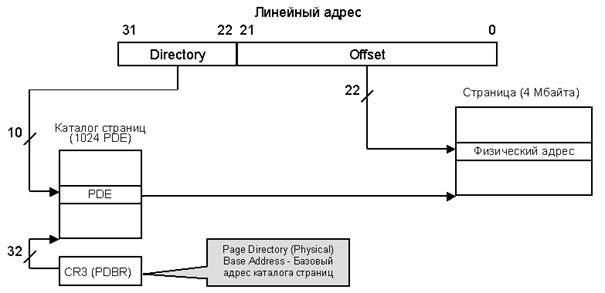

В процессорах, начиная с Pentium, кроме стандартных страниц в 4 Кбайта, могут использоваться страницы размером 4 Мбайта. Увеличение размера страницы связано с общим увеличением физического объема используемой оперативной памяти, и с увеличением накладных расходов на обслуживание маленьких страниц. Для включения расширения размера страницы (PSE – Page Size Extension) необходимо установить бит PSE в управляющем регистре CR4. При CR4.PSE = 0 работает базовый вариант страничного преобразования (рисунок 1.9). При CR4.PSE = 1 процессор анализирует бит 7 (PS, Page Size – размер страницы) строки каталога страниц PDE. Если PDE.PS = 0, эта строка ссылается на таблицу 4-килобайтных страниц, и преобразование выполняется по базовой схеме (рисунок 1.9). Если PDE.PS = 1, то разряды 22 – 31 этой строки представляют базовый физический адрес 4-мегабайтной страницы. (При 4-мегабайтных страницах этап с таблицами страниц исключен.)

Механизм страничного преобразования для 4-мегабайтных страниц приведен на рисунке 1.12, а формат строки каталога (PDE) для этого случая показан на рисунке 1.13.

Рисунок 1.12 – Страничная переадресация в режиме PSE (страницы по 4 Мбайт)

Рисунок 1.13 – Строка каталога для страницы размером 4 Мбайта

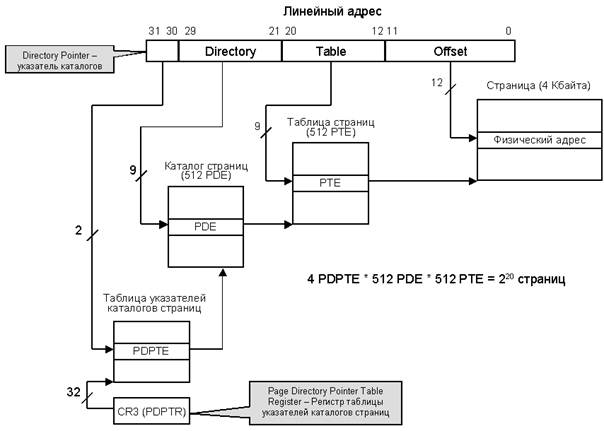

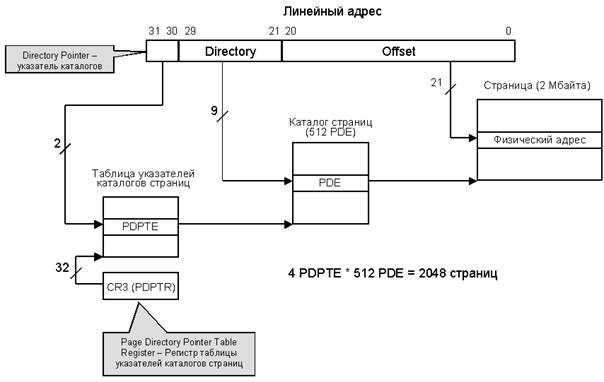

Начиная с процессоров Pentium Pro, поддерживается еще один режим страничного преобразования – PAE (Physical Address Extension) – расширение физического адреса с 32-разрядного до 36-разрядного. Это расширение включается установкой в «1» бита PAE в управляющем регистре CR4 (при этом бит PSE игнорируется, и соответствующий режим становится недоступным). У процессоров, начиная с Pentium Pro, шина адреса 36-разрядная, однако, дополнительные 4 разряда адреса доступны лишь в режиме PAE при разрешении страничного преобразования (то есть, одновременно должны быть установлены биты CR0.PG и CR4.PAE).

Если разрешен режим расширения физического адреса PAE, процессор поддерживает страницы нескольких размеров: 4 Кбайта, 2 Мбайта и 4 Мбайта. Как и при 32-разрядной адресации, страницы этих размеров могут адресоваться некоторым набором таблиц страничной трансляции (таблица каталогов может указывать на страницы размером 2 или 4 Мбайта, а таблица страниц – на 4 килобайтные страницы). Для поддержки 36-разрядной физической адресации в структуры данных страничного преобразования внесены следующие изменения:

- Разрядность элементов страничной переадресации увеличена до 64 бит, чтобы в него мог поместиться 36-разрядный базовый физический адрес. Каждый 4-килобайтный каталог страниц и таблица страниц может содержать до 512 записей (входов).

- В иерархию трансляции линейного адреса добавлена новая таблица, называемая таблицей указателей на таблицы каталогов, и расположенная в первых 4 Гбайтах памяти. Эта таблица содержит 4 64-разрядных строки, и она находится в иерархии выше таблиц каталогов. В режиме PAE процессор поддерживает до 4 таблиц каталогов страниц.

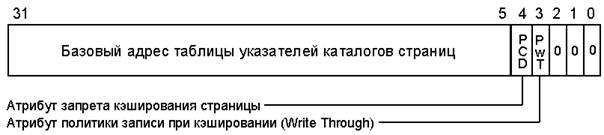

- В управляющем регистре CR3 вместо 20-разрядного поля базового адреса таблицы каталогов страниц используется 27-разрядное поле базового адреса таблицы указателя на таблицы каталогов страниц (см. рисунок 1.14). В этом случае регистр CR3 называется PDPTR (Page Directory Pointer Table Register). Это поле представляет старшие 27 разрядов физического адреса первого байта таблицы указателей каталогов страниц, который выровнен по 32-байтной границе (младшие 5 двоичных разрядов равны нулю).

- Трансляция линейного адреса изменена таким образом, чтобы позволить разместить 32-битные линейные адреса в большем физическом адресном пространстве.

Рисунок 1.14 – Формат управляющего регистра CR3 в режиме расширения физического адреса PAE

В режиме PAE процессор может работать со страницами размером 4 Кбайта и 2 Мбайта. На рисунке 1.15 показан механизм страничного преобразования в режиме расширения физического адреса PAE при размере страниц в 4 Кбайта, а на рисунке 1.16 – для страниц в 2 Мбайта. Из рисунка видно, что в 32-битном управляющем регистре CR3 хранится базовый адрес таблицы указателей каталогов страниц. Эта таблица состоит всего из четырех 64-разрядных записей. Два старших бита (30 – 31) линейного адреса выбирают из этой таблицы указатель на одну из четырех таблиц каталогов. Следующие 9 разрядов (21 – 29) линейного адреса выбирают элемент из этой таблицы, который может быть ссылкой на таблицу страниц или базовым адресом страницы памяти. Что именно определяет элемент этой таблицы, определяется значением атрибута PS записи. При PS = 0 запись определяет ссылку на таблицу страниц. Тогда разряды 12 – 20 линейного адреса определяют страницу, размером в 4 Кбайта, в таблице страниц, а разряды 0 – 11 являются смещением в этой странице. При PS = 1 запись определяет базовый адрес страницы, размером в 2 Мбайта. Тогда разряды 0 – 20 линейного адреса являются смещением внутри выбранной страницы с этим базовым адресом.

Рисунок 1.15 – Страничное преобразование в режиме расширения физического адреса PAE для страниц размером 4 Кбайта

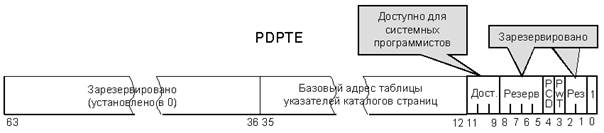

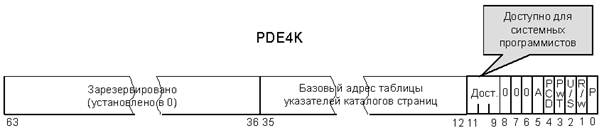

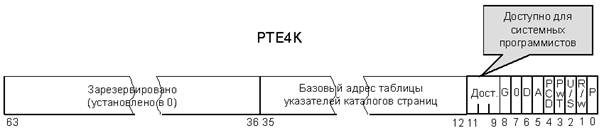

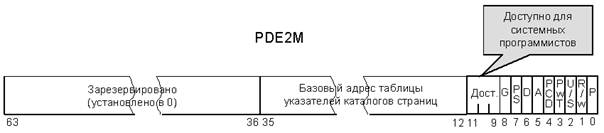

На рисунке 1.17 – 1.20 показана структура 64-битных элементов страничного преобразования для различного размере страниц. На рисунке 1.17 показана строка таблицы указателей на каталоги (напомним, что эта таблица может состоять не более, чем из четырех элементов). На рисунке 1.18 показана строка каталога страниц, а на рисунке 1.19 – строка таблицы страниц для страниц размером в 4 Кбайта. На рисунке 1.20 показана строка каталога страниц для страниц размером в 2 Мбайта.

Все показанные на рисунках атрибуты имеют те же названия и то же назначение, что и на рисунке 1.13 для строки каталога страниц для страниц размером в 4 Мбайта.

Рисунок 1.16 – Страничное преобразование в режиме расширения физического адреса PAE для страниц размером 2 Мбайта

Рисунок 1.17 – Структура 64-битного элемента таблицы указателей на каталоги для режима PAE

Рисунок 1.18 – Структура 64-битного элемента таблицы каталога страниц в режиме PAE для страниц размером в 4 Кбайта

Рисунок 1.19 – Структура 64-битного элемента таблицы страниц в режиме PAE для страниц размером в 4 Кбайта

Рисунок 1.20 – Структура 64-битного элемента таблицы каталога страниц в режиме PAE для страниц размером в 2 Мбайта

В зависимости от типа записей, изображенных на рисунках 1.17 – 1.20, указанный в них базовый физический адрес обозначает следующее:

- в элементе таблицы указателей на каталоги страниц (PDPTE) – физический адрес первого байта каталога 4 Кбайтных страниц (рисунок 1.17),

- в элементе таблицы каталога страниц (PDE) – физический адрес первого байта таблицы 4 Кбайтных страниц (рисунок 1.18) или физический адрес первого байта 2 Мбайтной страницы (рисунок 1.20),

- в элементе таблицы страниц (PTE) – физический адрес первого байта 4 Кбайтной страницы (рисунок 1.19).

Для всех рассмотренных записей (за исключением записей в таблице каталогов 2 Мбайтных страниц) биты базового адреса интерпретируются как 24 старших разряда 36-разрядного физического адреса, что требует выравнивания таблиц страниц и самих страниц по 4 Кбайтным границам. Если запись в таблице каталога страниц указывает на 2 Мбайтную страницу, то базовый адрес в этой записи интерпретируется как 15 старших разрядов 36-разрядного физического адреса, что требует выравнивания страниц по 2-мегабайтном границам.

Если разрешен режим расширения физического адреса PAE, во всех записях таблицы указателей каталогов страниц (PDPTE) должен быть установлен флаг присутствия Р (бит 0 в записи). То есть, флаг присутствия Р должен быть установлен, если взведены флаги PAE (бит 5 в управляющем регистре CR4) и PG – Paging, страничное преобразование (бит 31 в управляющем регистре CR0). Если при разрешенном режиме расширения физического адреса PAE флаг присутствия флаг присутствия не установлен во всех четырех записях таблицы указателей каталогов страниц (PDPTE), генерируется исключение общей защиты (#GP).

Флаг размера страницы (PS – бит 7 в записи таблицы каталогов страниц PDE) определяет, указывает ли данная запись на таблицу 4 Кбайтных страниц или на 2 Мбайтную страницу. Если флаг сброшен, запись указывает на таблицу 4 Кбайтных страниц, если же он установлен, запись указывает на 2 Мбайтную страницу. Этот флаг позволяет в пределах одного и того же набора таблиц преобразования использовать одновременно 4 Кбайтные и 2 Мбайтные страницы.

Флаги доступа A и «грязности» D (биты 5 и 6 в записях таблиц) используются в тех элементах таблиц, которые указывают на страницы.

Биты 9 – 11 во всех элементах таблиц в режиме расширения физического адреса PAE доступны для программного использования. (Если сброшен флаг присутствия Р, до для программного использования доступны биты с 1 по 63.)

Все биты на изображениях элементов таблиц страничного преобразования, помеченные, как «зарезервированные» или, как «0», должны быть установлены в «0», и недоступны для программного использования. Когда установлены флаги PSE и/или PAE в управляющем регистре CR4, процессор генерирует исключение «отказ страницы» (#PF), если не установлены в нуль зарезервированные биты элементов таблиц каталогов (PDE) и таблиц страниц (PTE), или исключение общей защиты (#GP), если не установлены в нуль зарезервированные биты элементов таблицы указателей каталогов страниц (PDPTE).

Для того чтобы проверить, поддерживает ли конкретный процессор расширения размеров страниц и физического адреса, достаточно попытаться выполнить команду CPUID, которая появилась в наборе команд процессора одновременно с указанными расширениями. Если процессор не поддерживает команду CPUID, то он не поддерживает и указанные расширения.

2015-01-07

2015-01-07 1290

1290