Функциональную сложность ИС характеризуют степенью интеграции, т. е. количест-вом элементов (чаще всего транзисторов) на кристалле. Для ее количественной оценки ис-пользуют условный коэффициент k = lgN, где N – количество элементов. В зависимости от значения k ИС подразделяются:

k ≤ 2 (N ≤ 100) – интегральная схема (ИС) – Integrated Circuit (IC);

2 ≤ k ≤ 3 (N ≤ 1000) – интегральная схема средней степени интеграции (СИС) – Medium Scale Integration (MSI);

3 ≤ k ≤ 5 (N ≤ 105) – большая интегральная схема (БИС) – Large Scale Integration (LSI);

k > 5 (N > 105) – сверхбольшая интегральная схема (СБИС) – Very Large Scale Inte-gration (VLSI).

В последнее время появляются ИС, содержащие на одном кристалле свыше нескольких миллионов элементов, такие ИС называются ультрабольшими интегральными схемами (УБИС) [3].

Кроме степени интеграции, используют показатель плотность упаковки элементов на кристалле – число элементов, приходящихся на единицу его площади.

Уровень технологии характеризуется минимальным технологическим размером Δ, т. е. наименьшими достижимыми размерами легированной области в полупроводниковом слое или пленочном слое на поверхности, например минимальной шириной эмиттера, шириной проводников, расстояниями между ними.

По функциональному назначению ИС подразделяются на аналоговые и цифровые. Ана-логовые ИС предназначены для преобразования и обработки сигналов, изменяющихся по за-кону непрерывной функции. В их основе лежат простейшие усилительные каскады. Самой распространенной аналоговой ИС является операционный усилитель (ОУ). Цифровые ИС предназначены для преобразования и обработки сигналов, изменяющихся по закону дискрет-ной функции. В их основе лежат транзисторные ключи, способные находиться в двух устой-чивых состояниях: открытом и закрытом. Использование транзисторных ключей дает воз-можность создавать различные логические, триггерные и другие ИС [5].

По конструктивно-технологическому признаку различают полупроводниковые и гибри-дные интегральные схемы. В полупроводниковых ИС все элементы и межэлементные соеди-нения изготовлены в объеме и на поверхности полупроводника. В гибридных ИС на диэлект-рической подложке изготавливаются пленочные пассивные элементы (резисторы, конденса-торы) и устанавливаются навесные активные и пассивные компоненты. Промежуточным ти-пом ИС являются совмещенные интегральные схемы, в которых транзисторы изготавливают-ся в активном слое кремния, а пленочные резисторы и диоды – как и проводники на изолиру-ющем слое двуокиси кремния.

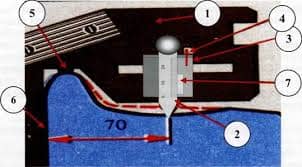

Для изготовления интегральных схем используется групповой метод производства и планарная технология.

Групповой метод производства заключается в том, что, во-первых, на одной пластине полупроводникового материала одновременно изготавливается большое количество интег-ральных схем; во-вторых, если позволяет технологический процесс, то одновременно обра-батываются десятки таких пластин. После завершения цикла изготовления ИС пластина раз-резается в двух взаимно-перпендикулярных направлениях на отдельные кристаллы (chip – англ.), каждый из которых представляет собой ИС.

Планарная технология – такая организация технологического процесса, когда все эле-менты и их составляющие создаются в интегральной схеме путем их формирования через плоскость (plane – плоскость).

Одна или несколько технологических операций при изготовлении ИС заключается в со-единении отдельных элементов в схему и присоединении их к специальным контактным площадкам. Поэтому необходимо, чтобы выводы всех элементов и контактные площадки на-ходились в одной плоскости. Такую возможность обеспечивает планарная технология [3].

2015-02-27

2015-02-27 364

364