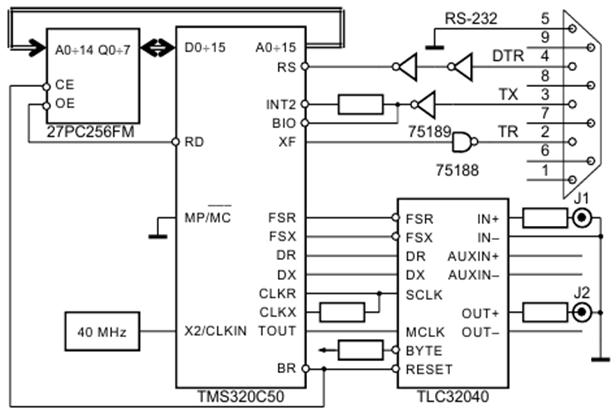

Лабораторный макет построен на базе процессора TMS320C50 и аналогового интерфейса (АИ) TLC32040. Структурная схема макета представлена на рис. 2.1

В состав макета входит также кварцевый генератор частотой 40 МГц, ПЗУ (PROM) для загрузки программного ядра емкостью 32К байт (27PC256FM) и преобразователь напряжения. Макет выполнен в виде отдельной платы и подключается к ПЭВМ типа IBM PC через интерфейс RS-232. Питание макета осуществляется от внешнего источника переменного напряжения ±9В, которое преобразуется в постоянные напряжения +9В и –9В (для питания последовательного интерфейса), а также в стабилизированное напряжение +5В и –5В (для питания цифровых схем). Для сопряжения TTL-уровней микросхемы процессора с уровнями интерфейса RS-232 используются две микросхемы преобразователей уровня сигналов (75188 и 75189). Макет имеет также пять разъемов для подключения к шине TMS дополнительного оборудования, два разъема для ввода и вывода аналоговых сигналов, разъем для интерфейса и разъем питания.

Поскольку АИ подключается к макету через последовательный интерфейс, то для связи с ПЭВМ используются программно управляемые выводы процессора XF и BIO, а поскольку макет не имеет внешней памяти данных, то вывод управления глобальной памятью BR используется для сброса АИ и выбора PROM.

Внутреннее ПЗУ программ процессора содержит программу-загрузчик для загрузки программы-монитора (программного ядра) из PROM в макет, которая служит для управления и отладки пользовательских программ.

Пользовательские программы загружаются в блок SARAM, сконфигурированный как память программ и данных. При этом часть памяти занята под программное ядро.

Для обмена информацией с АИ используются регистры последовательного интерфейса TMS320C50 - передатчика DXR и приемника DRR.

2015-02-04

2015-02-04 873

873