- функция 2И-НЕ

- функция 2И-НЕ

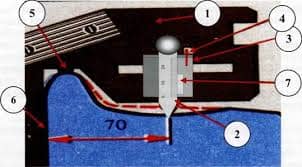

В этой схеме 3 каскада:

- входной каскад на транзисторе VT1, реализующий функцию и;

- 2-ой каскад – фазоразделительный на транзисторе VT2 и два выходных каскада VT3 и VT4.

Если на все входы х1 и х2 подать напряжение или сигнал высокого уровня соответствующий 1, то эммиторный переход транзистора VT1 окажется закрытым. При этом ток, протекающий через R1 и коллекторный переход транзистора VT1, откроет транзистор VT2; падение напряжения на R4 будет достаточным для открывания транзистора VT4. Напряжение на коллекторе VT2 таково, что оно закроет транзистор VT3 в результате на выходе элемента установится напряжение низкого уровня, соответствующее логическому 0. Если хоть на один из входов подать напряжение низкого уровня или соединить его с землей, то эммиторный переход транзистора VT4 откроется и зашунтирует базовый переход транзистора VT2. Транзистор VT2 закроется, это приведет к закрыванию VT4 и открыванию VT3. На выходе установится напряжение высокого уровня. В логическом элементе выполняется функция 2и-не. Транзистор VT1 называется многоэммитерным. Количество эмиттеров определяет количество входов, участвующих в операциях и. Для ИМС типа ТТЛ 0 и 1 считаются соответственно при напряжении источника 5 В. Сигнал 0 не более 0,4 в и сигнал 1 не менее 2,4 В.

Уровни напряжения зависит от нагрузки на выходе, поэтому, как правило, микросхема нормируются величиной входов других элементов, присоединенных к входу, как правило, нагрузочная способность не более 10. Если нагрузочная способность большая – это микросхемы более мощные источники.

2015-03-07

2015-03-07 888

888