Матричная схема или логическая матрица представляет собой сетку ортогональных линий, в пересечениях которых могут устанавливаться полупроводниковые элементы: диоды либо транзисторы, реализующие необходимую схему.

Для возможности программирования матрицы эти диоды или транзисторы подключаются к соответствующим проводникам матрицы через легкоплавкие перемычки. Во время программирования эти перемычки либо пережигают, либо оставляют, в зависимости от схемы, которую следует реализовать с помощью матрицы. Матричные схемы ориентированы на реализацию булевых функций узлов больших интегральных схем (БИС).

Таким образом, из матричной структуры путём её программирования получают требуемое комбинационное устройство. Поэтому такие структуры называют программируемые логические матрицы (ПЛМ).

ПЛМ, как правило, имеют два схемотехнических уровня: на первом из них создаются требуемые конъюнкции, а на втором – дизъюнкции. Обе матрицы соединяются каскадно.

Существуют также ПЛМ, имеющие в своём составе встроенные элементы памяти. Такие ПЛМ характеризуются разрядностью регистра памяти.

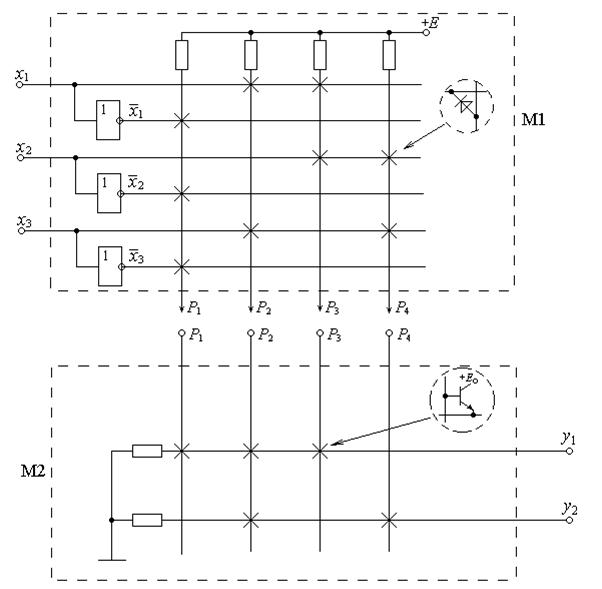

Рассмотрим матрицы на рис. 17.1.

Матрица М1 имеет три возможных входа х 1, х 2, х 3, шесть горизонтальных и четыре вертикальные шины. Горизонтальные шины х 1, х 2, х 3 в М1 являются входными, а вертикальные P 1… Р 4 – выходными.

Выходы Р носят названия линий терм.

Входные шины х 1, х 2, х 3 связаны с вертикальными шинами как непосредственно, так и через инверторы (шины  ,

,  ,

,  ).

).

МатрицаМ1работает как дешифратор, выходами которого являются конъюнктивные термы P 1… Р 4. Способ включения полупроводниковых элементов (например, диодов) на пересечениях, обозначенных крестиками, позволяет реализовать на любом из выходов, любую конъюнкцию её входных переменных, т.е. функцию И.

Действительно, при появлении единицы на одном из входов хі, на выходе соответствующего инвертора появляется  логический нуль. Если, например, есть перемычка на горизонтальной линии хі , то единичный потенциал линии хі закроет “свой” диод и на соответствующей вертикальной линии терм будет напряжение, примерно равное напряжению (+ Е), т.е единица.

логический нуль. Если, например, есть перемычка на горизонтальной линии хі , то единичный потенциал линии хі закроет “свой” диод и на соответствующей вертикальной линии терм будет напряжение, примерно равное напряжению (+ Е), т.е единица.

Если перемычка находится на линии инверсного входа, то низкий уровень линии  откроет “свой” диод и практически весь ток вертикальной шины потечёт через горизонтальную линию, оставляя обесточенной вертикальную шину, т.е. на выходе будет логический нуль.

откроет “свой” диод и практически весь ток вертикальной шины потечёт через горизонтальную линию, оставляя обесточенной вертикальную шину, т.е. на выходе будет логический нуль.

Рисунок 17.1 – Программируемая логическая матрица:

М1 – матрица конъюнкции; М2 – матрица дизъюнкци

Сохранить высокий уровень логической единицы на вертикальной шине PN можно лишь тогда, когда все диоды на этой линии будут закрыты, что возможно только при уровнях логической единицы на всех горизонтальных линиях, к которым подключена вертикальная шина PN.

Таким образом, на вертикальной линии PN реализуется конъюнкция переменных. Матрица конъюнкций М1 реализует функции конъюнкций согласно логическим уравнениям:

(17.1)

(17.1)

Матрица М2 имеет четыре вертикальные шины P 1 … Р 4 и две горизонтальные у 1 и у 2. Способ включения транзисторов на пересечениях шин позволяет реализовать на любом из её выходов любую дизъюнкцию (функцию ИЛИ) входных переменных. В матрице М2 входными являются вертикальные шины, а выходными – горизонтальные.

В этой матрице показан пример реализации дизъюнкций, описываемых математическими выражениями

(17.2)

(17.2)

В матрице дизъюнкций М2 транзистор на обозначенном крестиком пересечении ортогональных линий будет открыт лишь при наличии тока в вертикальной линии, а при отсутствии тока – закрыт. Для матрицы М2 достаточно, чтобы на её горизонтальной линии был открыт хотя бы один транзистор, тогда на выходе yj будет уровень логической единицы. Только отсутствие токов на всех горизонтальных линиях обеспечивает на вертикальной шине логический ноль, что определяет операцию дизъюнкции. В приведенном примере (рис. 17.1) реализуется функция, описываемая уравнениями (17.2).

В матрице дизъюнкций М2 транзистор на обозначенном крестиком пересечении ортогональных линий будет открыт лишь при наличии тока в вертикальной линии, а при отсутствии тока – закрыт. Для матрицы М2 достаточно, чтобы на её горизонтальной линии был открыт хотя бы один транзистор, тогда на выходе yj будет уровень логической единицы. Только отсутствие токов на всех горизонтальных линиях обеспечивает на вертикальной шине логический ноль, что определяет операцию дизъюнкции. В приведенном примере (рис. 17.1) реализуется функция, описываемая уравнениями (17.2).

Если соединить обе матрицы М1 и М2, как показано на рис. 17.2, то полученная схема будет реализовать систему булевых функций

(17.3)

(17.3)

Построение схем с матричной структурой сводится к определению точек пересечения шин, где должны быть включены полупроводниковые приборы. В табл. 17.1 столбцы содержат переменные х 1,..., хL и функции у 1,..., уN .

Реализацию системы функций матрицами М1 и М2 можно показать в виде табл. 17.1.

На пресечении j -й строки и столбца хl (l =

На пресечении j -й строки и столбца хl (l =  ) записываются:

) записываются:

– 1, если переменная хi входит в j -ю конъюнкцию без инверсии;

– 0, если переменная хi входит в j -ю конъюнкцию c инверсией;

– чёрточка (–), если переменная хi невходит в j -ю конъюнкцию.

На пресечении j -й строки и столбца  записываются:

записываются:

– 1, если j -я конъюнкция входит в дизъюнкцию yn;

– точка (∙), если j -я конъюнкция не входит в дизъюнкцию yn.

Соответствующим образом любая система булевых функций у 1,..., уN входных переменных х 1,..., хL может быть реализована двухуровневой матричной схемой, на первом уровне которой создаются разные конъюнкции Р 1,..., Р В, а на втором – дизъюнкции у 1,..., уN соответствующих конъюнкций. В результате построение схемы с матричной структурой сводится к определению точек пересечения шин, где должны быть включены диоды или транзисторы.

Сложность матричной реализации оценивается суммарной ёмкостью (площадью) матриц. В общем случае в схеме, имеющей L входов; N выходов и В вертикалей площадь составляет

S(M) = S(M1) + S(M2) = 2 LB + BN. (17.4)

На базе ПЛМ можно строить комбинационные цифровые устройства на довольно простых принципах.

Основным этапом разработки является составление таблицы программирования ПЛМ, являющейся инструкцией процедуры пережигания ненужных перемычек в матрицах.

С целью расширения функциональных возможностей использования ПЛМ промышленностью выпускаются её упрощённые варианты, например, программируемые матрицы вентилей, программируемые матрицы логики, программируемые мультиплексоры и т.п.

2015-04-06

2015-04-06 1761

1761