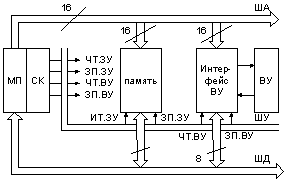

Отличительной особенностью этого интерфейса является раздельная адресация памяти и внешних устройств. Так, при адресации памяти в системах, построенных на базе МП КР580 (рис. 4.1), используются вся 16-разрядная шина адреса и управляющие сигналы ЧТ.ЗУ и ЗП.ЗУ, формируемые системным контроллером СК. При этом для обмена данными между МП и памятью используется значительное количество команд микропроцессора.

Для адресации же внешних устройств используются только 8 разрядов шины адреса и сигналы управления ЧТ.ВУ и ЗП.ВУ. Для обмена данными между МП и ВУ используются только две специальные команды IN ADR - ввод данных и OUT ADR - вывод данных, реализующие обмен данными только через аккумулятор МП. Такая процедура обмена снижает общую производительность системы, так как для обмена данными между ВУ и памятью потребуется дополнительно использовать несколько команд, обеспечивающих сохранность содержимого аккумулятора до начала обмена с ВУ и восстановление ее после обмена.

Рис. 4.1

Единственное достоинство интерфейса с раздельными шинами является использование всей шины адреса для адресации памяти, что позволяет построить модуль памяти максимального объема. Напомним, что 16-разрядная шина адреса позволяет адресовать 64 К ячеек памяти.

2015-04-30

2015-04-30 681

681