|

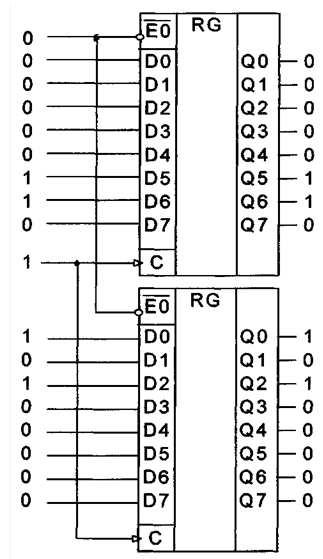

Рассмотрим принцип построения выходного регистра. Для построения 16 - разрядного регистра, необходимо взять 2 восьмиразрядных регистра и запараллелить входы ЕО между собой, а также входы С. Таким образом, получим регистр на 16 входов и 16 выходов. Пример такого регистра показан на рисунке 15.

Рисунок 15 - Шестнадцатиразрядный регистр.

Для того, чтобы данные от входов отобразились на выходах, надо на его вход С подать напряжение высокого уровня, а на вход ЕО подать напряжение низкого уровня, т.к. если подать напряжение высокого уровня, то в регистре установится третье z - состояние.

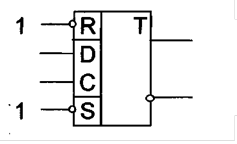

В качестве триггера для приема сигнала переноса выбрали микросхему 1533ТМ2.

|

Рисунок 17 - Микросхема типа ТМ2.

Для того чтобы триггер принимал сигнал переноса, необходимо на его вход S и R подать напряжение высокого уровня, т.е. уровень логической 1, чтобы в триггер загрузить входные данные. На вход С - подать напряжение высокого уровня, чтобы данные с входа передались на выходы. На вход D подадим сигнал переноса с четвертой микросхемы ИП3.

|

|

|

4.3 ОПИСАНИЕ РАБОТЫ ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ МНОГОРАЗРЯДНОГО ДВОИЧНОГО СУММАТОРА

Чтобы получить полную принципиальную схему многоразрядного двоичного сумматора, необходимо соединить принципиальную электрическую схему 16 - разрядного сумматора, схему 16 - разрядного регистра и схему триггера переноса (смотри принципиальную электрическую схему многоразрядного сумматора). Для этого соединим выходы FO...F3 устройств DD5...DD8 с входами DO...D7 устройств DDl1 и DD12. Выход сигнала переноса Сn+4 устройства DD8 соединим с входом D устройства DD10.1.

Результат суммирования с выходов FO...F3 поступит на входы DO...D7 устройств DD11 и DD12.

На вход С устройства D триггера и входного и выходного регистров подадим уровень логической 1, чтобы результат суммирования записался в эти устройства и отобразился на выходах Q0...Q7 устройств DD11 и DD12 и на выходе Q D триггера.

2015-05-20

2015-05-20 956

956