Для построения принципиальной электрической схемы 16-разрядного двоичного сумматора с параллельным переносом используйте микросхемы АЛУ и СУП, аналогичные ИПЗ и ИП4 ТТЛ. На микросхеме ИПЗ можно построить четырехразрядный двоичный сумматор.

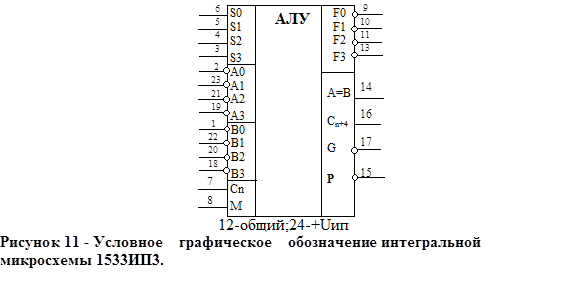

Условное графическое обозначение микросхемы ИПЗ для высоких уровней напряжения:

Микросхема ИПЗ представляет собой четырехразрядное арифметико-логическое устройство. Она может выполнять или 16 логических, или 16 арифметических операций. АЛУ имеет входы АО...A3 и ВО...ВЗ, на которые можно подать два четырехразрядных слова А и В. Входы SO...S3 позволяют выбрать 16 функций устройства. Однако благодаря входу М число функций можно увеличить в 2 раза, т.е. переключить режим, и АЛУ или выполняет 16 логических функций двух переменных, если на М подано напряжение высокого уровня, или 16 арифметических операций, при низком уровне напряжения на входе М. Вход Сn принимает входной сигнал переноса. Результат выполнения одной из 32 выбранных функций АЛУ отображает на выходах FO...F3. Кроме того, ИПЗ имеет три вспомогательных вывода: А=В - выход компаратора (открытый коллектор); G - выход генерации переноса, Р -выход распространения переноса. Последние два выхода G и Р имеют активные высоше уровни. Для организации переноса между несколькими ИПЗ, объединяемыми в многоразрядное АЛУ, используются входы Р и G, данные на которых не зависят от состояния входа переноса Сn. Так как ИПЗ имеет внутреннюю СУП, то сигнал переноса на выходе Сn+4 появляется при каждом входном сигнале переноса, поступившем на вход Gn. Для обеспечения высокоскоростных операций в многоразрядных АЛУ необходимо между ИПЗ включать специальные ИС, например ИП4, которая может обслуживать четыре ИПЗ.

На выходе компаратора А=В будет высокий уровень напряжения, если на всех выходах FO...F3 оказались высокие уровни. Сигнал выхода А=В можно использовать совместно с сигналом Сn+4 для выяснения соотношений: А>В или А<В.

АЛУ ИП3 может работать либо с высокими, либо с низкими уровнями напряжения. В зависимости от этого меняются знаки инверсии на входах и выходах.

Состояния АЛУ приведены в таблице 2.

Таблица 2 - Выбор функции при высоких активных уровнях операндов в ИПЗ.

| Выбор функций | Выходные данные при активных высоких уровнях | ||

| S3 S2 S1 SO | Логические функции (на выходе М =1) | Арифметические операции (на выходе М - напряжение низкого уровня) | |

| Сn = 0 (без переноса) | Сn = 1 (с переносом) | ||

| А-1 | А | |

| АВ-1 | АВ | |

+В +В | А  -1 -1 | А  | |

| -1 | |||

| А+(А+  ) ) | А+(А+  )+1 )+1 | |

| АВ+(А+  ) ) | АВ+(А+  )+1 )+1 | |

| А-В-1 | А-В | |

А+  | А+  | (А+  )+1 )+1 | |

| А+(А+В) | А+(А+В)+1 | |

| АÅВ | А+В | А+В+1 | |

| В |  +(А+В) +(А+В) |  +(А+В)+1 +(А+В)+1 | |

| А+В | А+В | (А+В)+1 | |

| А+А | (А+А)+1 | ||

А  | АВ+А | АВ+А+1 | |

| АВ | А  +А +А | А  +А+1 +А+1 | |

| А | А | А+1 |

Основные статические и динамические характеристики приведены в таблице 3.

Таблица 3 - Основные статические и динамические параметры микросхемы 1533ИП3.

| Тип микросхемы | Uип | U°вых, | U1вых, | I0 вх | I1 вх, | I пот | t0,1зд.р. | t1,0зд.р. |

| В | B | B | мА | мА | мА | нс | нс | |

| 1533ИП3 | 0,4 | 2,5 | -0,7 | 0,07 |

Микросхема ИП4 содержит схему ускоренного переноса для сумматора на 4, 16, 64 и более разрядов.

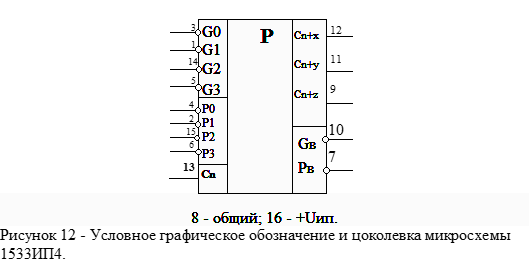

Условное графическое обозначение и цоколевка представлены на рисунке 12.

Микросхема 1533ИП4 - устройство ускоренного переноса, способное обеспечивать перенос четырех двоичных сумматоров или группы большого числа сумматоров, поскольку они имеют выходы каскадирования. Интегральная микросхема может работать как в режиме логики высокого уровня, так и в режиме логики низкого уровня, при этом активные уровни всех входов и выходов меняются на противоположные.

Рассмотрим работу микросхемы 1533ИП4 в режиме логики высоких уровней. Микросхема применяется совместно с четырьмя АЛУ типа ИП3. Она имеет четыре входа генерации переноса G0...G3 и четыре входа распространения переноса Р0...Р3, которые соединяются с соответствующими выходами G и Р каждого из четырех АЛУ ИПЗ. Входы G и Р имеют активные напряжения низкого уровня. Имеется также вход приема пульсирующего переноса Сn (активный уровень - высокий).

Устройство имеет три выхода переноса Сn+х, Cn+y, Cn+z (активные уровни высокие), а также выходы Gв и Рв (активные уровни ‑ низкие). Выход Gв - групповая генерация переноса, Рв - групповое распространение переноса.

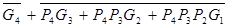

Работа микросхемы описывается следующими уравнениями:

Cn+x = Gl+Pl Cn;

Cn+y=G2 + P2G0+P2PlCn

Cn+z= G3 + P3G2 + P3P2G1 + РЗР2Р1 Cn

Gв =  ;

;

Pв =

Основные статические и динамические характеристики приведены в таблице 4.

Таблица 4 - Основные статические и динамические параметры для микросхемы 1533ИП4.

| Тип микросхемы | Uип | U°вых, | U1вых, | I0 вх | I1 вх, | I пот | t0,1зд.р. | t1,0зд.р. |

| В | B | B | мА | мА | мА | нс | нс | |

| 1533ИП4 | 0,4 | 2,5 | -0,2 | 0,02 |

Регистр - ПЦУ, которое предназначено для хранения n-разрядного двоичного числа.

Параллельный регистр осуществляет ввод информации одновременно всеми разрядами сразу при наличии активного уровня на входе синхронизации.

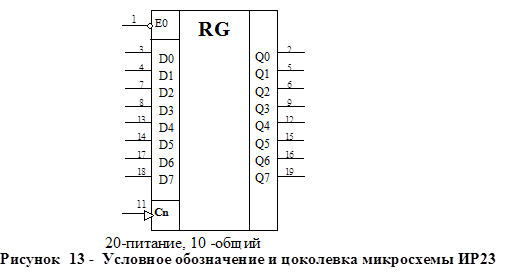

Для построения регистра будем использовать микросхему 1533ИР23. Условное графическое обозначение и цоколевка микросхемы приведены на рисунке 13.

Микросхема ИР23 - это восьмиразрядный регистр на D-триггерах, с динамическим С - входом. Регистр снабжен выходными буферными усилителями, имеющими z- состояние, которое можно установить с помощью входа разрешения ЕО, если подать на него напряжение высокого уровня. Выходные буферные усилители обладают высокой нагрузочной способностью.

Входная часть регистра - это восемь D-триггеров со входами разрешения параллельной записи С. Если на входе С действует высокий уровень напряжения, то данные от входов DO...D7 отображаются на выходах QO... Q7. _

Если на вход С подать напряжение низкого уровня, разрешается запись в триггеры нового восьмиразрядного кода.

Если на вход ЕО подано напряжение низкого уровня, то данные из D-триггеров регистра пройдут на выходы QO...Q7.

Регистр ИР23 принимает и отображает информацию синхронно с положительным перепадом тактового импульса, подаваемого на вход С.

Основные статические и динамические параметры приведены в таблице 5.

Таблица 5 - Основные статические и динамические параметры микросхемы 1533ИР23.

| Тип микросхемы | Uип | U°вых, | U1вых, | I0 вх | I1 вх, | I пот | t0,1зд.р. | t1,0зд.р. |

| В | B | B | мА | мА | мА | нс | нс | |

| 1533ИР23 | 0,4 | 2,4 | -0,2 | 0,02 |

Триггер - устройство, которое может находится в одном из двух состояний и переходить из одного состояния в другое под воздействием управляющего или входного сигнала, т.е. может использоваться для хранения значения одной логической переменной или одноразрядного двоичного числа.

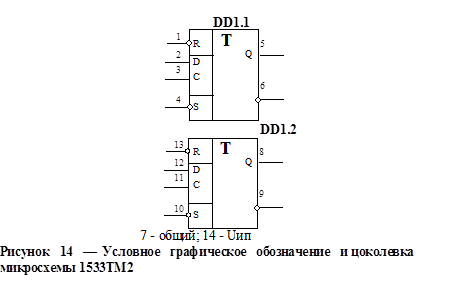

В качестве триггера для приема сигнала переноса выберем микросхему D - триггера 1533ТМ2.

Условное графическое обозначение и цоколевка микросхемы представлены на рисунке 14.

|

Микросхема ТМ2П содержит два независимых комбинированных D-триггера, имеющих общую цепь питания. У каждого триггера имеется один информационный вход D, вход синхронизации С и два дополнительных входа S, R независимой асинхронной установки триггера в ециничное и нулевое состояния.

Асинхронная установка D-триггера в единичное и нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы S и R. В это время входы D и С не влияют.

Если на входы R и S одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера  и Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов S и R состояние триггера будет неопределенным. Поэтому комбинация S = R = 0 для этих входов является запрещенной.

и Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов S и R состояние триггера будет неопределенным. Поэтому комбинация S = R = 0 для этих входов является запрещенной.

Загрузить в триггер входные уровни логического 0 и 1 можно, если на входы S и R подать напряжение высокого уровня: S = R = 1. Сигнал от входа D передается на входы триггера при поступлении положительного перепада импульса на вход С (изменение от низкого к высокому). Однако, чтобы D-триггер переключался правильно (согласно таблице состояний 6), необходимо уровень на входе D зафиксировать заранее, т.е. до прихода перепада на вход С.

Таблица 6 - Состояния триггера 1533ТМ2.

| Режим работы | Входы | Выходы | ||||

| S | R | D | C | Q |  | |

| Асинхронная установка | X | X | ||||

| Асинхронный оброс | X | X | ||||

| Неопределенность | X | X | ||||

| Загрузка “1”(установка) | | |||||

| Загрузка”0” (сброс) | |

Основные статические и динамические параметры приведены в таблице 7.

Таблица 7 - Основные статические и динамические параметры микросхемы 1533ТМ2.

| Тип микросхемы | Uип | U°вых, | U1вых, | I0 вх | I1 вх, | I пот | t0,1зд.р. | t1,0зд.р. |

| В | B | B | мА | мА | мА | нс | нс | |

| 1533ТМ2 | 0,4 | 2,5 | -0,3 | - |

2015-05-20

2015-05-20 1118

1118