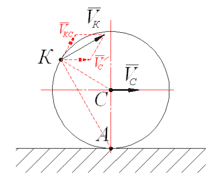

RISC Рис.1 (ReducedInstructionSetComputer архитектура процессора с сокращённым набором инструкций) архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Первые RISC-процессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).. Начало исследований данной области положено компанией IBM (в исследовательском центре IBM, имени Томаса Джона Уотсона) в 1975 году.

(Рис.1)

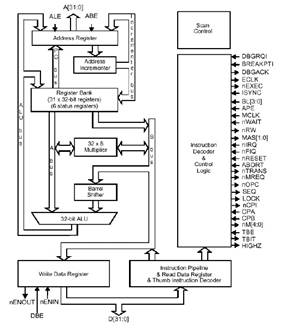

Схема Risc процессора(Рис.2)

(Рис.2)

На самом деле, термин «сокращённый» в названии описывает тот факт, что сокращён объём (и время) работы, выполняемый каждой отдельной инструкцией — как максимум один цикл доступа к памяти, — тогда как сложные инструкции CISC-процессоров могут требовать сотен циклов доступа к памяти для своего выполнения.

2015-05-22

2015-05-22 978

978