· Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды.

· Специализированные команды для операций с памятью — чтения или записи. Операции вида Read-Modify-Write («прочитать-изменить-записать») отсутствуют. Любые операции «изменить» выполняются только над содержимым регистров (т. н. архитектура load-and-store).

· Большое количество регистров общего назначения (32 и более).

· Отсутствие поддержки операций вида «изменить» над укороченными типами данных — байт, 16-битное слово. Так, например, система команд DEC Alpha содержала только операции над 64-битными словами, и требовала разработки и последующего вызова процедур для выполнения операций над байтами, 16- и 32-битными словами.

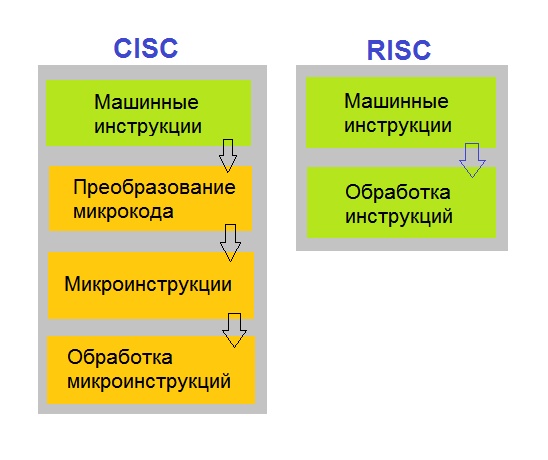

· Отсутствие микропрограмм внутри самого процессора. То, что в CISC-процессоре исполняется микропрограммами, в RISC-процессоре исполняется как обыкновенный (хотя и помещённый в специальное хранилище) машинный код, не отличающийся принципиально от кода ядра ОС и приложений. Так, например, обработка отказов страниц в DEC Alpha и интерпретация таблиц страниц содержалась в так называемом PALcode (Privileged Architecture Library), помещённом в ПЗУ. Заменой PALCode можно было превратить процессор Alpha из 64-битного в 32-битный, а также изменить порядок байтов в слове и формат входов таблиц страниц виртуальной памяти.

Иные архитектурные решения, типичные для RISC

· Спекулятивное исполнение. При встрече с командой условного перехода процессор исполняет (или, по крайней мере, читает в кэш инструкций) сразу обе ветви до тех пор, пока не окончится вычисление управляющего выражения перехода. Позволяет отказаться от простоев конвейера при условных переходах.

· Переименование регистров. Каждый регистр процессора на самом деле представляет собой несколько параллельных регистров, хранящих несколько версий значения. Используется для реализации спекулятивного исполнения.

Основными преимуществами RISC-архитектуры является наличие следующих свойств:

- Большое число регистров общего назначения.

- Универсальный формат всех микроопераций.

- Равное время выполнения всех машинных команд.

- Практически все операции пересылки данных осуществляются по маршруту регистр – регистр.

Аппаратные блоки в RISC-архитектуре:

- Блок загрузки инструкций включает в себя следующие составные части: блок выборки инструкций из памяти инструкций, регистр инструкций, куда помещается инструкция после ее выборки и блок декодирования инструкций. Эта ступень называется ступенью выборки инструкций.

- Регистры общего назначения совместно с блоками управления регистрами образуют вторую ступень конвейера, отвечающую за чтение операндов инструкций. Операнды могут храниться в самой инструкции или в одном из регистров общего назначения. Эта ступень называется ступенью выборки операндов.

- Арифметико-логическое устройство и, если в данной архитектуре реализован, аккумулятор, вместе с логикой управления, которая исходя из содержимого регистра инструкций определяет тип выполняемой микрооперации. Источником данных помимо регистра инструкций может быть счетчик команд, при выполнении микроопераций условного или безусловного перехода. Данная ступень называется исполнительной ступенью конвейера.

- Набор состоящий из регистров общего назначения, логики записи и иногда из RAM образуют ступень сохранения данных. На этой ступени результат выполнения инструкций записываются в регистры общего назначения или в основную память.

Главные отличия архитектуры RISC от CISC

RISC - Набор команд в процессорах построенных на данной архитектуре, как видно из названия, упрощенный. Что позволяет поднять частоту, снизить стоимость производства и оптимально распараллеливать задачи. Вот собственно основное отличие.

В CISC архитектуре соответственно длина команды не ограничена, одна инструкция содержит (может содержать) несколько арифметических действий. Как следствие - требуются суперскалярные вычисления и использование в процессоре конвейера. По сути процессор построенный по CISC архитектуре выполняет те же команды что и процессор на RISC архитектуре, но внутри себя содержит командный интерпретатор, "переделывающий" сложные команды в несколько простых.

Основной проблемой по реализации RISC архитектуры являлась недостаточная поддержка со стороны софта и программного обеспечения. Но с появлением поддержки UNIX\Linux подобных систем, эта проблема практически решилась.

Самыми известными и успешными представителями архитектуры RISC являются ARM от разработанная ARM Holdings. Процессоры с данной архитектурой, применяемые в абсолютном большинстве мобильных устройств и даже серверных системах, благодаря очень низкому энергопотреблению и тепловыделению.

Из наиболее известных RISC архитектур можно также выделить разработки компании IBM (PowerPC, Power), компанией SunMicrosystems (SPARC- архитектура) и компанией Atmel (AVR– архитектура).

На данный момент, RISC – архитектура является одной самых распространённых в мире, имея более 40% мирового рынка. Данный результат в основном благодаря ARM архитектуре и то, что в современных мобильных устройствах используются именно процессоры ARM (в абсолютном большинстве).

2015-05-22

2015-05-22 6309

6309