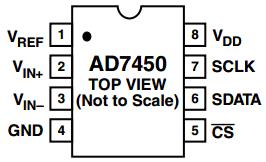

Процессы начала преобразования и выдачи данных синхронизируются сигналом на входе CS и последовательными тактовыми импульсами, что позволяет передавать данные в микропроцессоры или DSP. Выборка входного сигнала, преобразование и выдача данных начинаются по срезу сигнала CS. [18]. Описание конфигурации выходов AD7450 представлено на рис. 8.

Рисунок 8 Конфигурация выходов АЦП

В таблице 6 представлено описание каждого выхода АЦП.

Таблица 6. Описание выходов AD7450

| № выводов | Значения | Функции |

| VREF | Справочный вход AD7450. Для 5В питания VREF = 2.5В (±1%), для 3В питания VREF = 1.25В (±1%). VREF должен быть заземлен с конденсатором от 0.1 мкФ. | |

| VIN+ | Положительный дифференциальный аналоговый вход | |

| VIN- | Отрицательный дифференциальный аналоговый вход | |

| GND | Аналоговая Земля для АЦП. | |

| VDD | Вход электропитания 3 В (±10%) или 5 В (±5%). Подаваемое напряжение должно быть заземлено с конденсаторами на 0.1 мкФ и 10 мкФ для фильтрации входного сигнала. | |

| SCLK | Логический вход. Используется для процесса преобразования данных. | |

| SDATA | Логический выход. Результат преобразования АЦП в виде последовательного потока данных. Данные состоят из 4х нулей в начале и 12 бит банных (всего 16 бит). Данные представлены в двоичном виде. | |

| __ CS | Вход начала преобразования и передачи данных. Преобразование начинается при CS = 0. |

2015-06-10

2015-06-10 371

371