При проектировании системы EWSD определяется объем следующего оборудования координационного процессора СР113:

- число процессоров обработки вызовов САР;

- объем общей памяти CMY;

- число процессоров ввода-вывода IOР;

- число устройств управления вводом/выводом IOС;

Если нагрузка на станцию превышает некоторую, заданную для данной версии системы величину, то в конфигурацию СР113 кроме, основных процессоров ВАРМ и ВАРS включаются процессоры обработки вызовов САР. Табл. 29 содержит данные для определения числа процессоров обработки вызовов САР NCAP (количество вызовов измеряется в КВНСА - тысяча вызовов в час наибольшей нагрузки).

Таблица 29

| Координационный процессор СР113 | |||||||

| Версия | ВАР0/1 | +CAP0 | +CAP1 | +САР2 | +САРЗ | +САР4 | +САР5 |

| V7.1W | |||||||

| V10 |

Сначала необходимо определить общее количество вызовов, поступающих на станцию в ЧНН.

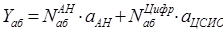

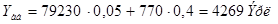

1. Нагрузка, поступающая на станцию по абонентским линиям, равна:

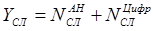

Нагрузка, поступающая на станцию по входящим соединительным линиям (Таблица 13, Таблица 26)

2. Средняя длительность занятия абонентской линии равна tАЛ =72 с.

3. Средняя длительность занятия соединительной линии равна tСЛ =60 с.

4. Количество вызовов, поступающих на станцию в ЧНН, равно:

NЧНН = Yаб ·3600/72+ YСЛ ·3600/60 (в кило вызовов в ЧНН).

NЧНН =3397 ·3600/72+1203,6 ·3600/60=242064 кило вызовов в ЧНН

Следовательно, для обслуживания данного количества вызовов в ЧНН в состав процессора СР113 для версий 7 кроме основных процессоров ВАР 0/1 необходимо включить один процессор обработки вызовов CAP0.

Таблица 30

Ёмкость общей памяти CMYкоординационного процессора.

| Количество LTG в системе EWSD | до 31 | до 63 | до 126 | до 252 | до 504 |

| Емкость общей памяти CMY, Мбайт |

Согласно расчётам, данная станция EWSD содержит 126 LTG, поэтому объём общей памяти CMY равен 256 Мбайт.

-Определение числа процессоров ввода-вывода IOР.

Число процессоров ввода-вывода IOP:МB для центрального генератора тактовой частоты IOP:MB(CCG) и системной панели IOP:MB(SYP) всегда равно двум (для обеспечения надежности).

Число процессоров ввода-вывода для группы буферов сообщений IOP:MBU(MBG) рассчитывается по формуле:

NIOP MBU(MBG) = ∑NMBG

где ∑NMBG - общее количество групп буферов сообщений MBG с учетом дублирования.

NIOP MBU(MBG) =2

Число процессоров ввода-вывода для устройства управления системой сигнализации ОКС №7 IOP:MBU(CCNC) рассчитывается по формуле:

NIOP MBU(CCNC) = 2· NCCNC

где NCCNC =2- число блоков CCNC на станции.

NIOP MBU(CCNC) = 2·2=4

Всего процессоров ввода-вывода: NIOP = 10

Определение числа устройств управления вводом/выводом IOС.

Одно устройство управление вводом/выводом IOС позволяет включать до 16 процессоров ввода-вывода IOР, но из соображений надежности устройства управления вводом/выводом дублируются - имеется IOC0 и IOС1, поэтому NIOC = 2

Координационный процессор занимает два статива: один для процессоров ВАР и общей памяти (R:CP113А), другой статив (R:DEVD) -для процессоров ввода-вывода и устройств машинной периферии. Т.к. необходимо использование CAP, то требуется установка еще одного статива R:CP113B.

2015-06-26

2015-06-26 605

605