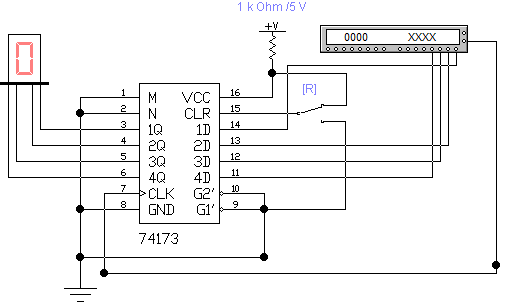

Рассмотрим четырехразрядный регистр на микросхеме ТТЛ 74173. Эта микросхема представляет собой четырехразрядный статический регистр, построенный на D-триггерах с прямыми динамическими входами 1D...4D, входом сброса Clear и выходами 1Q...4Q с третьим (Z) состоянием, управляемым сигналом G1' и G2'. При обычной работе на управляющих выводах надо задать низкий уровень напряжения; аналогично низкий уровень напряжения подается на входы разрешения записи М и N. Вход сброса имеет высокий активный уровень.

Рис. 2

Соберем схему по рис. 3, проведем испытания регистра. От крыв лицевую панель генератора слов, сделаем на ней необходимые установки (0 – F) и выберем пошаговый режим Step. Включаем моделирование и, нажимая многократноклавишу Step, шаг за шагом загружаем в регистр выбранные слова. Очистку регистра можно произвести ключом [R], кратковременно подав на вход CLR лог. 1.

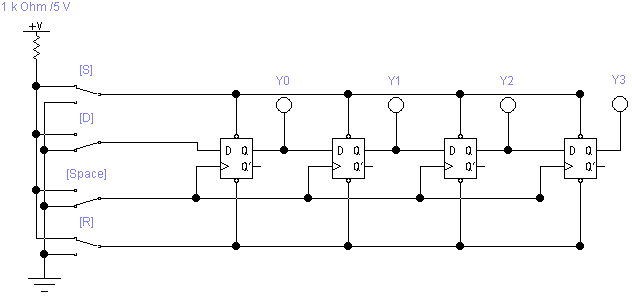

- Последовательно-параллельный регистр

Рис. 3

Регистр собран на четырех D-триггерах и работает следующим образом. Исходное состояние: переключатели S = R = 1; D и Space – в положении – 0. Введем в регистр последовательно (слева – направо) двоичное число 10012:

1) Установим D = 1 и дважды нажмем на клавишу Space. Убедимся в том, что триггер младшего разряда установлен в положение 1 (комбинация 1000);

2) Установим D = 0 и дважды нажмем на клавишу Space. Убедимся в том, что триггер младшего разряда установлен в положение 0, а триггер следующего разряда установлен в 1 (комбинация 0100);

3) Установим D = 0 и дважды нажмем на клавишу Space. Убедимся в том, что триггер младшего разряда установлен в положение 0, а два триггера следующих разрядов установлены в 0 и 1 соответственно (комбинация 0010);

4) Установим D = 1 и дважды нажмем на клавишу Space. Убедимся в том, что триггер младшего разряда установлен в положение 1, а три триггера следующих разрядов установлены в 0, 0 и 1 соответственно (комбинация 1001).

Таким образом, в регистр последовательно введено двоичное число 10012. Считывать информацию из регистра можно в параллельном двоичном коде. Для этого к основным выходам триггеров Q подключены логические пробники. Кроме того, данный регистр позволяет легко выполнить операцию обращения кода. Для этого достаточно снимать сигнал c инверсных выходов триггеров  регистра.

регистра.

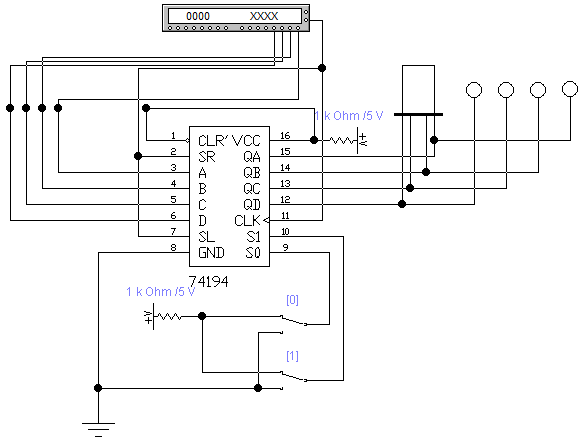

3. Четырехразрядный двунаправленный универсальный регистр сдвига на микросхеме 74194

Среди различных регистров в интегральном исполнении выделяется однокорпусная микросхема 74194, представляющая собой четырехразрядный двунаправленный универсальный регистр сдвига. Этот регистр позволяет сдвигать информацию и влево, и вправо, загружать данные как последовательно, так и параллельно. Регистр можно каскадировать и использовать для кольцевого перемещения информации.

В программе EWB выбираем микросхему 74194. Если на вход (CLEAR)'поступает напряжение низкого уровня, то на выходах QA...QD также устанавливается низкий уровень независимо от состояний всех других входов. При подаче на вход (CLEAR)' напряжения низкого уровня, режим работы регистра определяется состояниями входов S1 и S0. Данные, поступающие последовательно на вход SL (Serial Left - последовательно влево), когда на вход S0 подается напряжение низкого уровня, а на вход S1 - напряжение высокого уровня (S1=1,S0=0), сдвигаются влево на каждом фронте тактового импульса CLC (на переходе - POS). Сдвиг данных вправо происходит, когда на вход S0 подается напряжение высокого уровня, а на вход S1 - напряжение низкого уровня (S1=0, S0=1), при этом данные поступают последовательно на вход SR (Serial Right - последовательно вправо). Синхронная параллельная загрузка данных через входы A…D производится при S1=S0=1. В это время последовательные вводы и сдвиги запрещены (соответствующие порты заперты).

В сжатом виде таблица операций такова:

| S1 | S0 | Операция |

| Хранение | ||

| Сдвиг вправо | ||

| Сдвиг влево | ||

| Параллельная загрузка |

Соберем схему (рис. 4)

Рис. 4

Ограничим пределы кодовых комбинаций от 0000 до 000F и выберем пошаговый режим работы. Теперь, задавая ключами [0] и [1] различные состояния управляющих входов S0 и S1, проверим все случаи загрузки и сдвига.

Установим S0 = 0 и S1 = 1, т.е. включим режим сдвига влево. До включения моделирования регистр пуст: индикаторы - 0000, дисплей - 0. При включении моделирования показания будут таковы: индикаторы - 1000, дисплей - 8; Stepl индикаторы - 1100, дисплей - С, Step2 индикаторы - 1110, дисплей - Е, Step3. индикаторы -1111, дисплей - F. Регистр заполнился за четыре такта (считая включение) и дальнейшие шаги не изменяют его состояния, так как на смену уходящей единице приходит новая. Если после шага Stepl: индикаторы - 1100, дисплей - С, не выключая моделирование, поменять положение ключей и задать S0=1 и S1=0, то после очередного шага единица самого старшего разряда исчезнет, но ее место тут же займет единица из предыдущего разряда, одновременно в самом младшем разряде появится единица. В результате получим: индикаторы - 1001, дисплей - 9. Если после этого, не выключая моделирование, поменять положение ключа 1, сделав S0=1 и S1=1, а далее осуществить загрузку, то результат будет таким: индикаторы - 0011, дисплей - 3. Так как мы находились в ячейке 0002 генератора слов, а перешли на данном шаге и загрузили следующую ячейку 0003.

2015-06-26

2015-06-26 5177

5177