1. Убедитесь, что питание NI ELVIS выключено, выключатель расположен на задней стенке устройства.

2. Осторожно вставьте модуль расширения Emona DATEx в сокет NI ELVIS.

3. Установите переключатель Control Mode (режим управления) на модуле DATEx (в верхнем правом углу) в положение PC CONTROL (Управление от компьютера).

Примечание: все эти действия могли быть выполнены ранее.

6. Включите питание NI ELVIS, затем включите питание макетной платы, выключатель расположен на передней панели устройства.

7. Включите компьютер и дайте ему загрузиться.

9. Запустите программу NI ELVIS по указанию преподавателя.

Примечание: Если программа NI ELVIS запустилась успешно, появится окно “ELVIS – Instrument Launcher” – окно запуска измерительных приборов.

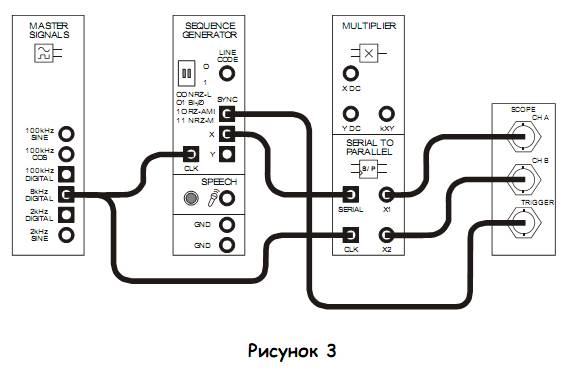

11. Соберите схему, изображенную на рисунке 3.

Примечание: Вставьте черные штекеры кабеля осциллографа в гнездо заземление (GND).

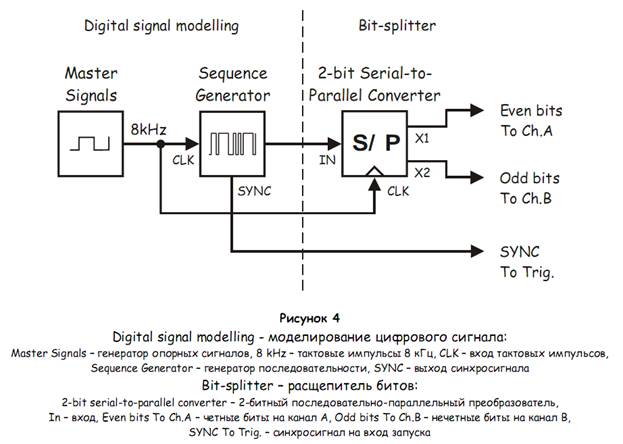

Схема на рисунке 3 может быть представлена блок-схемой, приведенной на рисунке 4. Для моделирования цифровых данных используется генератор последовательностей (SEQUENCE GENERATOR). 2-разрядный последовательно-параллельный преобразователь (SERIAL-TO-PARALLEL CONVERTER) расщепляет исходный поток данных на поток четных битов и поток нечетных битов.

12. Установите те же настройки осциллографа, что и в эксперименте 1, со следующими изменениями:

· Trigger Source (Источник сигнала запуска) – TRIGGER (Внешний) вместо CH A

13. Включите канал B осциллографа для одновременного наблюдения сигналов на обоих выходах последовательно-параллельного преобразователя.

14. Сравните цифровые сигналы. Вы должны увидеть, что сигналы отличаются друг от друга.

Вопрос 1

Каково соотношение между скоростью следования бит на выходах последовательно-параллельного преобразователя и на его входе?

Скорость передачи данных на выходах в два раза ниже, чем на входе.

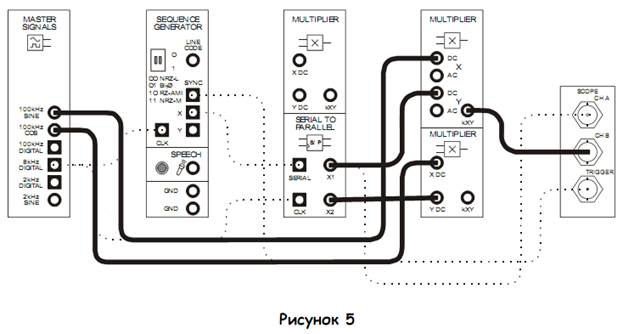

15. Внесите изменения в собранную схему, как показано на рисунке 5.

Напоминание: Пунктирными линиями обозначены уже выполненные соединения.

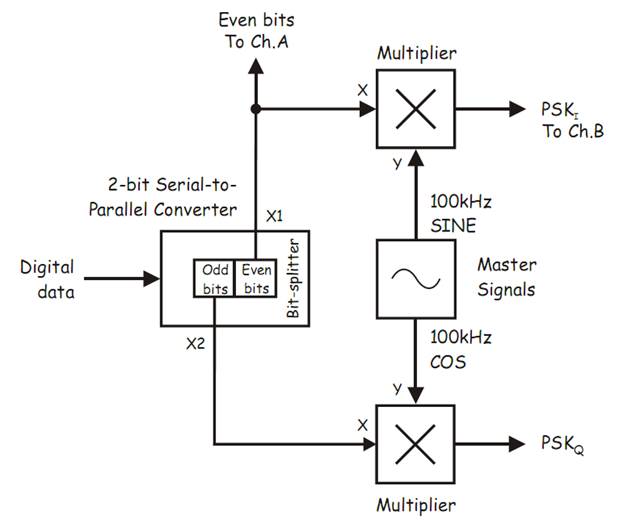

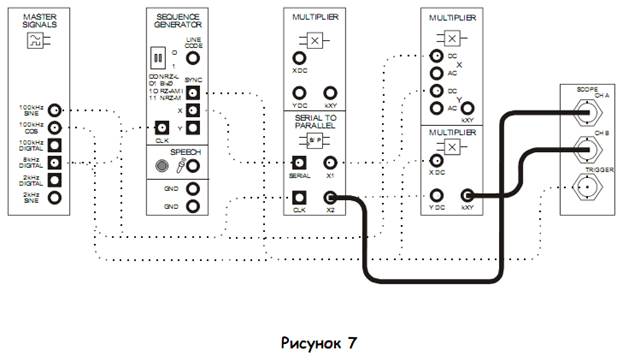

Все узлы схемы, приведенной на рисунке 5, кроме блоков моделирования цифровых данных, могут быть представлены блок-схемой, показанной на рисунке 6. Обратите внимание, что оба выхода расщепителя бит подключены к разным умножителям. На вторые входы умножителей поданы синусоидальные сигналы частотой 100 кГц, сдвинутые друг относительно друга по фазе на 90°, это необходимо для получения QPSK сигнала.

16. Установите масштаб по оси времени 200 мкс/дел.

17. Сопоставьте четные биты с выходным сигналом первого умножителя PSKI.

Совет: Возможно, вам будет проще это сделать, если установите масштаб по напряжению канала B – 2 В/дел.

18. Установите переключатель источника сигнала запуска осциллографа (Trigger Source) в положение CH A (канал A).

19. Установите масштаб по оси времени – 50 мкс/дел.

20. Исследуйте поведение несущей, обратите внимание, что происходит при изменении логического уровня сигнала в цифровом потоке данных.

Вопрос 2

На каком основании можно предположить, что на выходе умножителя – BPSK сигнал?

При изменении логического уровня цифрового сигнала фаза сигнала на выходе умножителя изменяется на противоположную.

21. Снова установите масштаб по оси времени 500 мкс/дел., а переключатель источников сигнала запуска осциллографа Trigger Source в положение Trigger (Внешний).

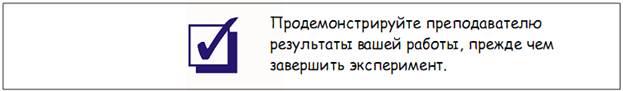

22. Подключите осциллограф так, как показано на рисунке 7.

Изменение подключения осциллографа учтено в блок-схеме, приведенной на рисунке 8.

23. Установите масштаб по оси времени 200 мкс/дел.

24. Сравните нечетные биты в потоке данных с сигналом на выходе второго умножителя PSKI.

25. Установите переключатель источника сигнала запуска осциллографа (Trigger Source) в положение CH A (канал A).

26. Установите масштаб по оси времени 50 мкс/дел.

27. Исследуя поведение несущей, обратите внимание, что происходит при изменении логического уровня сигнала в цифровом потоке данных.

Вопрос 3

Какого типа сигнал формируется на выходе умножителя?

BPSK.

28. Снова установите масштаб по оси времени 500 мкс/дел., а переключатель источников сигнала запуска осциллографа “Trigger Source” в положение “Trigger” (Внешний).

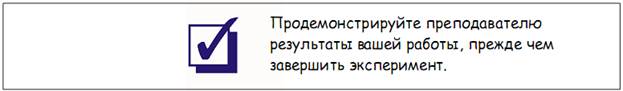

29. Внесите изменения в схему, как показано на рисунке 9.

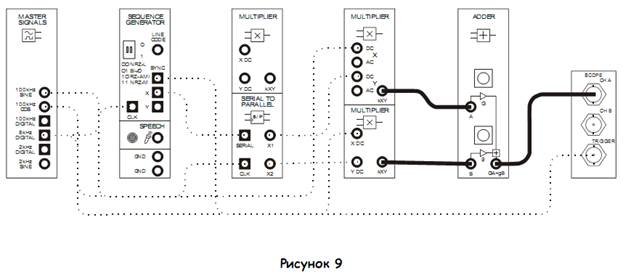

Эту схему можно представить блок-схемой, приведенной на рисунке 10. Сложение сигналов PSKI и PSKQ осуществляет модуль ADDER (Сумматор), и, тем самым, превращает схему в полноценный QPSK модулятор.

30. Отсоедините проводник от входа A сумматора.

Примечание: при этом из выходного сигнала сумматора убирается составляющая BPSKI.

31. Найдите модуль ADDER (Сумматор) на программной панели управления DATEx и с помощью виртуального регулятора g подберите такой коэффициент усиления, чтобы на выходе установился сигнал с размахом 4 В.

32. Верните обратно проводник на вход A сумматора.

33. Теперь отсоедините проводник от входа B сумматора.

Примечание: из выходного сигнала сумматора убирается составляющая BPSKQ.

34. С помощью виртуального регулятора G подберите такой коэффициент усиления, чтобы на выходе установился сигнал с размахом 4 В.

35. Верните обратно проводник на вход B сумматора.

Вопрос 4

Какой метод модуляции реализован в сигнале, формируемом на выходе сумматора?

QPSK.

2015-07-04

2015-07-04 836

836