На основе изложенных требований принимаем решение о необходимости проектирования главного вычислительного комплекса на основе микропроцессорного комплекта КР1810.

Однокристальный 16-разрядный МП КР1810ВМ86 (далее для краткости обозначаемый К1810) по своей архитектуре, логической организации и принципам управления ближе к мини-ЭВМ, чем к 8-разрядному МП. Он обладает высокой производительностью, мощной системой команд, средствами работы с операционными системами в режимах мультипрограммирования, мультипроцессирования и обработки сложных структур данных.

Архитектура МП имеет существенные особенности: возможность выполнения арифметических и логических операций над 8-, 16-, 32- и 64-разрядными словами, операций над последовательностями (цепочками) байт и слов, а также операций над двоично-кодированными десятичными данными. В 16-разрядном АЛУ реализуются операции умножения и деления с фиксированной запятой. Многочисленные режимы адресации позволяют увеличивать число базовых команд до нескольких сотен.

Микропроцессор имеет практически неограниченное число уровней прерывания. Прямо адресуемая область памяти составляет 1 Мбайт. Для организации связи с памятью и УВВ используется интерфейс типа И41. Программы, составленные для МП К580, относительно легко переделать для выполнения на МП К1810, так как система команд МП К580 представляет собой подмножество команд МП К1810 и обеспечивается программная совместимость снизу вверх.Микропроцессор имеет одно напряжение питания +5В однофазную синхронизацию с частотой 5 МГц и выпускается в 40-контактном керамическом корпусе с двусторонними выводами. Кристалл МП с геометрическими размерами 5,5X5,5 мм содержит около 29 000 транзисторов.

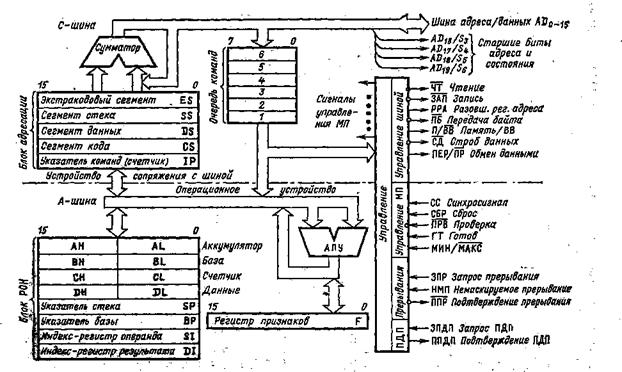

3.1. ЛОГИЧЕСКАЯ ОРГАНИЗАЦИЯ И ИНТЕРФЕЙС МИКРОПРОЦЕССОРА К1810

На рисунке 2 показана схема МП, в которой имеются относительно автономное устройство сопряжения с шиной (УСШ), организующее опережающую выборку команд из памяти и формирующее очередь выбранных байт последовательности команд, и операционное устройство извлекающее команды из очереди и реализующее предписанные командами операции в 16-разрядном АЛУ.

В состав УСШ входят 6-байтная очередь команд счетчик команд, четыре сегментных регистра и сумматор В со став операционного устройства (ОУ) входят блок регистров общего назначения (в том числе два регистра указателя и два индексных регистра), арифметическо-логическое устройство (АЛУ) и регистр признаков F. Устройство управления МП осуществляет управление УСШ, ОУ и кроме того периферийным оборудованием системы, обеспечивая обмен данными с использованием механизмов квитирования, прерывания и прямого доступа к памяти.

Рисунок 2. Схема и интерфейс микропроцессора К1810ВМ86.

; 3.1.1. УСТРОЙСТВО СОПРЯЖЕНИЯ С ШИНОЙ

Шесть однобайтных регистров очереди команд фактически образуют регистр команды МП, из которого ОУ последовательно извлекает очередную команду побайтно. Как только в очереди освободятся два регистра, так параллельно с работой ОУ и независимо от него УСШ выбирает из памяти программ следующие 2 байта. Имеет место совмещение, при котором в течение одного цикла обращения к памяти ОУ может выполнить две однобайтные команды.

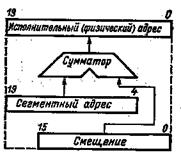

Рисунок 3. Механизм адресации памяти.

Адресуемая область памяти составляет 1 Мбайт и, следовательно, формат адреса равен 20 бит. Хотя МП генерирует 20-разрядные адреса памяти, но сам он манипулирует логическими адресами, содержащими 16-разрядный сегментный (базовый) адрес и 16-разрядное внутри сегментное смещение. Логические адреса преобразуются МП в физические (исполнительные) адреса в соответствии с рисунком. 3. Подобная организация формирования адреса в МП требует использования специального механизма сегментации памяти. Все адресуемое пространство разбивается на сегменты емкостью 64 Кбайт каждый. Начальный адрес каждого сегмента (20 бит) имеет в четырех младших разрядах нули — ХХХХО16, т. е. сегменты могут начинаться на границах блоков по 16 байт.

Структура памяти такова, что два смежных байта образуют двухбайтное слово, при чем старший байт хранится в ячейке с большим адресом. Слово может начинаться по четному или нечетному адресу. В первом случае слово передается за один цикл шины, а во втором — за два цикла. Следовательно, для достижения наивысшей производительности МП слова необходимо размещать по четным адресам памяти данных. (Порядок размещения команд в памяти на производительность МП не влияет, так как их длина составляет от 1 до 6 байт).

Сегментный адрес (начальный адрес сегмента) хранится в 16-разрядном сегментном регистре, а обращение к байту или слову внутри сегмента осуществляется с использованием 16-разрядного смещения, формируемого в ОУ. Если содержимое сегментного регистра равно нулю, то исполнительный адрес равен смещению. (В системах, где емкость памяти не превышает 64 Кбайт, сегментные регистры обнуляются и не используются.)

Адресуемое пространство ввода — вывода состоит из 65536 портов ВВ. Порты ВВ адресуются аналогично ячейкам памяти, но сегментные регистры при этом не используются. Все порты ВВ принадлежат как бы одному сегменту. Первые 256 портов ВВ могут быть доступны по командам с прямой адресацией (подобно МП К580), но. все порты ВВ адресуются косвенно (адрес содержится в регистре, определяемом командой). Исполнительный адрес портов ВВ имеет формат 20 бит, но старшие четыре разряда всегда равны нулю.

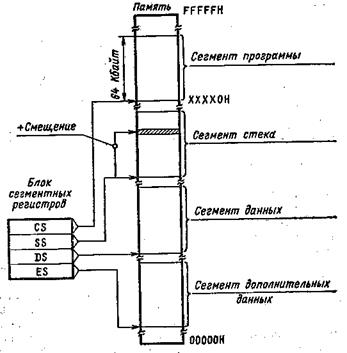

Большинство команд МП оперирует только 16-разрядными смещениями, а сегментные адреса находятся в одном из четырех регистров. Четыре 16-разрядных сегментных регистра содержат начальные адреса сегментов, адресуемых в процессе выполнения программы. Каждый сегментный регистр задает конкретный сегмент, что находит отражение и в их названиях: CS — код (программа), DS — данные, SS — стек, ES — экстракод (дополнительная информация). При всех операциях с обращением к памяти содержимое сегментных регистров автоматически суммируется со смещением, передаваемым из ОУ, и таким образом участвует в формировании исполнительного адреса (рисунок 4).

Рисунок 4. Организация адресного пространства памяти

Выборка команд из памяти осуществляется из текущего  сегмента по адресу, сформированному путем суммирования содержимого сегментного регистра кода CS и смещения, в качестве которого используется содержимое указателя команд IP (счетчика команд).

сегмента по адресу, сформированному путем суммирования содержимого сегментного регистра кода CS и смещения, в качестве которого используется содержимое указателя команд IP (счетчика команд).

При формировании исполнительных адресов данных содержимое DS суммируется со смещением, выдаваемым из ОУ (кроме тех случаев, когда смещение формируется через ВР или SP, а в операциях с цепочками — через DI).

Все обращения к стеку, в том числе неявные действия при прерываниях, обращениях к подпрограммам и при воз вратах, а также явные операции включения в стек и исключения из стека, осуществляются через сегментный регистр стека SS. В операциях над цепочками байт с использованием индексного регистра DI исполнительный адрес формируется через экстракодовый регистр ES. Сегментные регистры не используются только при выполнении команд ввода—вывода информации. Здесь следует отметить, что лю бой команде может предшествовать однобайтный префикс «пересегментирования», т. е. принудительного задания сегмента.

Основное назначение сегментных регистров — динамическое перемещение программ и данных в памяти, которое необходимо в мультипрограммной среде. Для динамического перемещения достаточно модифицировать содержимое сегментных регистров (при условии, что сама программа не изменяет их содержимого). Манипуляции с сегментными регистрами осуществляет операционная система.

3.1.2. ОПЕРАЦИОННОЕ УСТРОЙСТВО

Разработчики МП стремились сохранить программную совместимость с 8-разрядным МП (К580), и это оказало влияние на нерегулярность структуры ОУ и специализацию многих внутренних регистров. Хотя прямой программной совместимости не достигнуто, но все регистры МП К580 имеют аналоги в блоке РОН МП К1810, и в результате этого программы МП К580 легко трансформировать для выполнения в этом 16-разрядном МП.

В состав блока РОН входят четыре 16-разрядных регистрах АХ, ВХ, СХ и DX, допускающих независимую адресацию старших (Н) и младших (L) половин. Такая организация адресации регистров позволяет прямо обрабатывать как байты, так и двухбайтные слова.

Все регистры блока РОН на общих основаниях участвуют в выполнении арифметических и логических операций, представляя операнды и фиксируя результат выпол нения операции. Наряду с этим в системе команд МП имеется множество команд, которые специализируют неко торые РОН:

регистр АХ выполняет функции аккумулятора; с ним связаны операции умножения, деления, преобразования и десятичной коррекции. Он участвует во всех операциях ВВ в качестве или источника или приемника информации. Регистр AL соответствует аккумулятору МП К.580, а регистр АН является его расширением:

регистр ВХ используется как источник базового адреса и в некоторой степени соответствует регистровой паре HL микропроцессора К580;

регистр СХ используется в качестве счетчика в командах сдвигов и зацикливания, а также при операциях с цепочками байт;

регистр DX неявным образом адресуется в командах умножения и деления и, кроме того, содержит адрес порта ВВ.при косвенно-регистровой адресации.

Четыре 16-разрядных указательных и индексных регистра (SP, ВР, SI, DI) предназначены для хранения внутрисегментных смещений, обеспечивая косвенную адресацию и динамичные вычисления исполнительных адресов. Эти же регистры могут участвовать в выполнении арифметических и логических операций над двухбайтными словами.

Указательные регистры SP (стека) и ВР (базы) пред назначены для упрощения доступа к данным в текущем сегменте стека, но не в сегменте данных. Если сегмент специально не определен, то смещения SP и ВР по умолчанию относятся к текущему сегменту стека.

Индексные регистры SI (источника) и DI (приемника) содержат смещения, которые по умолчанию относятся к текущему сегменту данных. Эти четыре регистра специализируются в некоторых командах, что находит отражение в их названиях и аббревиатурах.

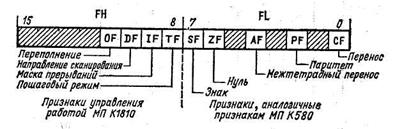

Формат 16-разрядного регистра признаков F показан на рис. 3.4. Его младший байт FL полностью соответствует регистру признаков МП К580: CF —перенос, PF — чет/нечет (в байте), AF — межтетрадный перенос (в байте), ZF — нуль, SF — знак. Кроме перечисленных признаков, которые фиксируют особенности результата последней арифметической или логической операции в. МП К1810, имеет место признак переполнения OF.

В дополнение к этому в регистре признаков F фиксируются некоторые признаки, предназначенные для управления вычислительным процессом в МП:

В дополнение к этому в регистре признаков F фиксируются некоторые признаки, предназначенные для управления вычислительным процессом в МП:

признак направления DF определяет направление ска нирования массива данных в операциях с цепочками (при DF=0 выполняется инкрементирование, а при DF=1 декрементирование содержимого регистра-указателя массива);

Рис. 5. Формат регистра признаков

признак прерывания IF используется в механизме маскирования прерываний (при IF=1 прерывания разрешены, т.е, МП воспринимает запросы на прерывание);

признак прослеживания TF, будучи установленным в единичное состояние, переводит МП в режим исполнения программы по командам (пошаговый режим), что необходимо при отладке программ.

Специализация некоторых регистров блока РОН позволила разработчикам МП закодировать команды МП в укороченном формате путем использования неявной адресации, что привело к необходимости (из-за привнесенной нерегулярности структуры РОН) внимательно следить при программировании за распределением и использованием этих уже неидеально «общих» регистров.

3.1.3. ИНТЕРФЕЙС МП И РЕАКЦИЯ УСТРОЙСТВА УПРАВЛЕНИЯ НА ВНЕШНИЕ СИГНАЛЫ

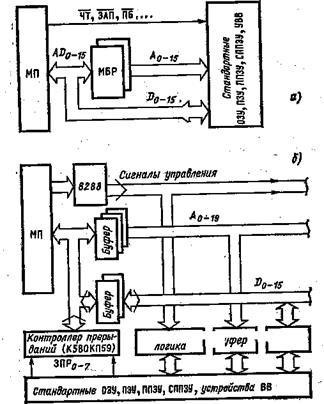

В зависимости от значения сигнала на управляющей линии МИН/МАКС микропроцессор может работать в минимальной или максимальной конфигурации (режиме). В зависимости от значения сигнала на этой управляющей линии меняется интерпретация восьми внешних сигналов МП. Как показано на. рисунке 6, в минимальной конфигурации, рассчитанной на простые системы (а), МП сам вырабатывает управляющие сигналы для системы (для памяти и УВВ), а в максимальной конфигурации (б), рассчитанной на большие сложные системы, МП вырабатывает управляющие сигналы только для специализированной БИС контроллера шины которая в свою очередь управляет системой. На рис. 3.1 приводится функциональное назначение линий управления МП в минимальной конфигурации. Описание работы МП также дается для минимальной конфигурации МП-системы.

Рисунок 6. Две конфигурации МП-систем:

а — минимальная; б — максимальная

Шина адреса/данных. По двунаправленным линиям AD0-15 в режиме временного мультиплексирования переда  ются младшие 16 разрядов адресов памяти и полные адреса УВВ. В первом такте машинного цикла МП выставляет адрес, а затем — принимает или передает 16-разрядное слово. Шина адреса/данных может быть установлена в высокримпедансное состояние.

ются младшие 16 разрядов адресов памяти и полные адреса УВВ. В первом такте машинного цикла МП выставляет адрес, а затем — принимает или передает 16-разрядное слово. Шина адреса/данных может быть установлена в высокримпедансное состояние.

Линии адреса/состояния. На выходных линиях AD16-19 в первом такте машинного цикла представлены значения четырех старших разрядов кода адреса. В остальных тактах машинного цикла по этим линиям передаются сигналы S3-6: сигналы S3-4 идентифицируют сегмент памяти, участвующий в формировании исполнительного адреса.(00àES, 01àCS, 10àSS, 11àDS); сигнал на линии S5 разрешает (единица) или запрещает (нуль) прерывания. Сигнал на линии Sб не используется.

Управление шиной. Сигналы на этих выходных линиях определяют операцию, выполняемую МП, и режим работы шины адреса/данных.

Сигналы чтения и записи (ЧТ, ЗАП) предназначены для управления режимом работы блоков памяти и УВВ.

Сигнал П/ВВ используется для селектирования памяти (единица) и УВВ (нуль) в адресном пространстве системы.

Сигнал разрешения работы регистра адреса (РРА) по является в качестве стробирующего сигнала в первом так те машинного цикла и, идентифицируя наличие на шине AD кода адреса, используется для загрузки адреса во внешний регистр.

Управляющий сигнал на линии ПБ выполняет две функции: в первом такте машинного цикла наличие нулевого значения означает, что байт данных передается по старшей половине шины (AD8-15), и это позволяет часть 8-битных УВВ подключить к старшей половине шины, а часть — к младшей (AD0-7); в остальных тактах машинного цикла на этой линии выставляется сигнал состояния S7.

Сигнал на линии ПЕР/ПР определяет направление передачи данных и используется совместно с сигналом стробирования данных СД для управления режимом работы шинных драйверов.

Управление микропроцессором. Сигналы на этих входных линиях определяют состояние и режим работы МП.

Сигнал на линии готовности ГТ обеспечивает МП возможность работы с любым типом внешней памяти и УВВ, так как позволяет приостановить работу МП и перевести его в состояние ожидания Тож. Кроме того, сигнал ГТ может быть использован в процессе отладки для пошагового исполнения программы в том случае, если он инициируется от соответствующей клавиши на пульте управления.

Сигнал проверки ПРВ совместно с командой ожидания WAIT используется как аппаратно-программное средство отладки системы. По команде WAIT проверяется значение сигнала на линии ПРВ, и при ПРВ = 1 микропроцессор переходит в состояние ожидания, т. е. не переходит к выполнению следующей команды. Сигнал ПРВ может быть использован в механизме взаимной синхронизации нескольких МП, так как из состояния ожидания МП выводится толь ко по сигналу прерывания.

Сигнал сброса СБР (обычно от пульта управления) переводит МП в начальное состояние, при котором в сегментный регистр кода загружается FFFFi6, а указатель команды IP (счетчик команд) устанавливается в нулевое состоя ние. Таким образом, сразу же по окончании сигнала сброса МП обращается по адресу FFFF016 в сегменте кода (программы).

Управление МП по прерываниям. Сигнал на входе не маскируемого прерывания НМП воспринимается независимо от текущего состояния МП. К этому входу, как правило, подключают схемы, которые фиксируют то или иное аварийное состояние МП-системы или объекта управления. На вход программно-маскируемого прерывания ЗПР от внешних устройств поступают сигналы готовности к обмену данными. В последнем машинном цикле каждой команды МП проверяет наличие запросов прерывания.

По сигналу немаскируемого прерывания МП помещает в стек содержимое регистра признаков F, сегментного регистра кода CS и регистра-указателя команды IP, a затем передает управление подпрограмме с фиксированным начальным адресом 0816.

При разрешенных программой прерываниях и в случае, если НМП = 0, а ЗПР= 1, МП помещает в стек содержимое F, CS и IP, формирует выходной сигнал подтверждения прерывания ППР и переходит к одной из 256 подпрограмм обслуживания прерывании. Начальный адрес подпрограммы обслуживания задается байтом, который передается в МП из интерфейса прерывающего устройства по сигналу подтверждения прерывания.

Управление МП в режиме прямого доступа к памяти. На вход ЗПДП от контроллера быстродействующего внеш  него устройства поступает сигнал запроса ПДП. По окончании текущего цикла передачи по шине МП переводит буферные схемы шины AD0-19. И некоторых управляющих сигналов в высокоимпедансное состояние и формирует сигнал ППДП подтверждения режима прямого доступа к памяти, по которому управление шиной передается контроллеру внешнего устройства. Из состояния «приостановки» выполнения программы МП выходит по окончании сигнала ЗПДП.

него устройства поступает сигнал запроса ПДП. По окончании текущего цикла передачи по шине МП переводит буферные схемы шины AD0-19. И некоторых управляющих сигналов в высокоимпедансное состояние и формирует сигнал ППДП подтверждения режима прямого доступа к памяти, по которому управление шиной передается контроллеру внешнего устройства. Из состояния «приостановки» выполнения программы МП выходит по окончании сигнала ЗПДП.

3.2. РАБОТА УСТРОЙСТВА УПРАВЛЕНИЯ МП

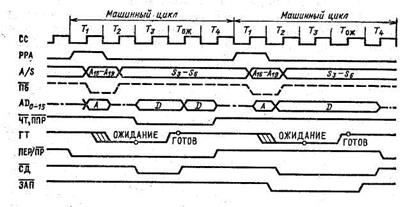

На рисунке 7 показана временная диаграмма МП КР1810ВМ86. Модель дискретного машинного времени для МП задается на входе СС синхросигналом от внешнего генератора (fcc = 5 МГц). Каждый машинный цикл МП состоит из четырех тактов, которым соответствуют состояния Ti, T2, Т3, Т4 автомата управления МП. Между тактами Т3 и Т4 с помощью сигнала готовности ГТ можно ввести произвольное число состояний ожидания Тож, что обеспечивает МП возможность работы с любым типом внешних мед ленно действующих устройств.

Рисунок.7. Временная диаграмма работы МП

Каждый машинный цикл МП представляет собой по существу цикл шины, так как МП в такте Ti каждого машинного цикла выдает на линии AD0_19 код адреса памяти и формирует сигнал сопровождения и идентификации информации РРА (разрешение регистра адреса). По этому сигналу код адреса должен быть обязательно зафиксирован на внешнем регистре, так как в следующих тактах машинного цикла по шине осуществляется передача данных. Кроме того, в тактах Т2—Т4 по линиям A16-19 передается код состояния S3-6, который идентифицирует тип машинного цикла в минимальной конфигурации МП-системы. (Остальные сигналы состояния So-2 используются только в максимальной конфигурации системы.)

Одновременно с передачей адреса по шине МП может формировать сигнал ПБ, который сопровождает передачу байта данных по линиям AD8-15- В такте T1 по шине AD0-15 передается адрес, а в тактах Т1—Т4 принимается или передается двухбайтное слово. Стробирующий сигнал ЧТ используется для управления режимом работы регистра данных памяти или УВВ. В режиме прямого доступа к памяти линия ЧТ переводится в высокоимпедансное состояние. Стробирующий сигнал ППР используется для ввода в МП вектора прерывания из контроллера УВВ, запросившего прерывание. В режиме прямого доступа к памяти линия ППР переводится в высокоимпедансное состояние.

Сигнал ГТ используется МП в качестве сигнала подтверждения окончания передачи данных из памяти или пор та УВВ. Устройство управления МП опрашивает значение сигнала на линии ГТ в начале такта Т3 и в зависимости от него переходит или к состоянию Тож или к состоянию Т4. Сигнал ПЕР/ПР управляет работой шинных драйверов и определяет направление передачи из МП в память/УВВ или в МП из памяти/УВВ. Управляющий сигнал стробирования данных СД формируется в МП при обращении к памяти и УВВ в тактах передачи данных по шине, а также в машинном цикле подтверждения прерывания. Сигнал ЗАП приобретает действующее нулевое значение в циклах записи в память и вывода информации в адресуемый порт УВВ.

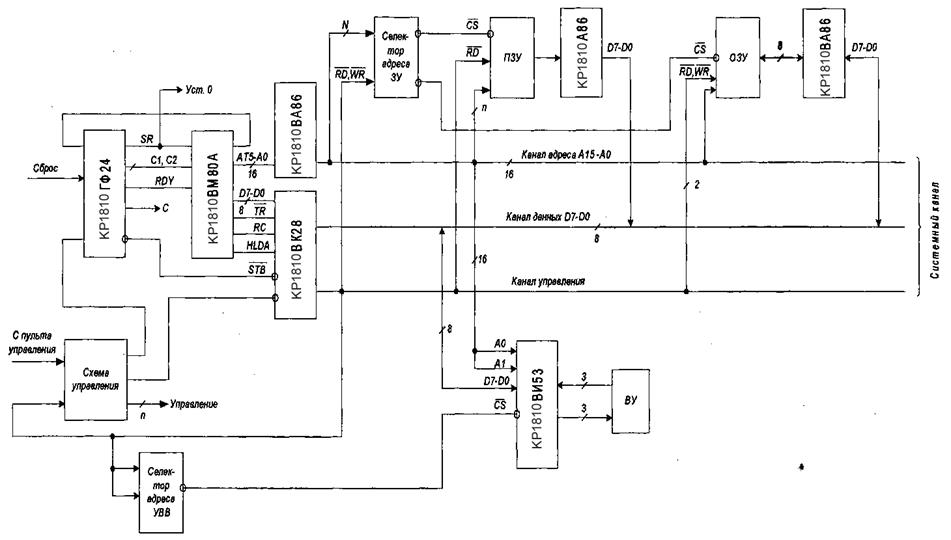

Рисунок 8. Структурная схема микропроцессорной системы на базе МПК серии КР1810

2015-07-02

2015-07-02 828

828