Таблица 3.1. Арифметические и логические команды

| Мнемо-ника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| ADD | Rd,Rr 0≤d≤31 0≤r≤31 | Сложить без переноса | Rd Rd + Rr | Z, C, N, V, H | |

| ADC | Rd.Rr 0≤d≤31 0≤r≤31 | Сложить с переносом | Rd Rd + Rr+ С | Z, C, N, V, H | |

| ADIW | Rd,K dE{24,26,28,30} 0≤K≤63 | Сложить непосредственное значение со словом | Rdh:RdlRdh:Rdl+ К | Z, C, N, V | |

| SUB | Rd,Rr 0≤d≤31 0≤r≤31 | Вычесть без заема | Rd Rd – Rr | Z, C, N, V, H | |

| SUBI | Rd, К 16≤d≤31 0≤K≤255 | Вычесть непосредственное значение | Rd Rd – К | Z, C, N, V, H | |

| SBC | Rd, Rr 0≤d≤31 0≤r≤31 | Вычесть с заемом | RdßRd-Rr-C | Z, C, N, V, H | |

| SBCI | Rd, К 16≤d≤32 0≤K≤255 | Вычесть непосредственное значение с заемом | RdßRd-K-C | Z, C, N, V, H | |

| SBIW | Rd, К dE{24,26,28,30} О≤К≤бЗ | Вычесть непосредственное значение из слова | Rdh:RdlßRdh:Rdl-K | Z, C, N, V | |

| AND | Rd, Rr 0≤d≤31 0≤r≤31 | Выполнить логическое AND | Rd ß Rd • Rr | Z, N, V | |

| ANDI | Rd, К 16<d<31 0<k≤255 | Выполнить логическое AND | Rd ß Rd • К | Z, N, V | |

| OR | Rd, Rr 0≤d≥31 0≤r≤31 | Выполнить логическое OR | Rd ßRd v Rr | Z, N, V | |

| ORI | Rd, К 16≤d≤31 0≤K≤255 | Выполнить логическое OR с непосредственным значением | Rd ßRd v К | Z, N, V | |

| EOR | Rd, Rr 0≤d≤31 0≤г≤31 | Выполнить исключающее OR | Rd ßRd Rr | Z, N, V | |

| СОМ | Rd 0≤d≤31 | Выполнить дополнение до единицы | RdßSFF-Rd | Z, C, N, V | |

| NEG | Rd 0≤d≤31 | Выполнить дополнение до двух | Rd ß S00 - Rd | Z, C, N, V, H | |

| SBR | Rd, К 16≤d≤31 0≤K≤255 | Установить биты в регистре | Rd ß Rd v К | Z, N,V | |

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| CBR | Rd, К 16≤d≤31 O≤K≤255 | Очистить биты в регистре | Rd ßRd • (SFF - К) | Z, N, V | |

| INC | Rd 0≤d≤31 | Инкрементировать | Rd ßRd + 1 | Z, N,V | |

| DEC | Rd 0≤d≤31 | Декрементировать | Rd ß Rd - 1 | Z, N,V | |

| TST | Rd 0≤r≤31 | Проверить на ноль или минус | RdßRd.Rd | Z, N, V | |

| CLR | Rd 0≤d≤31 | Очистить регистр | Rd ß Rd Å Rd | Z, N, V | |

| SER | Rd 16≤d≤31 | Установить все биты регистра | Rd ßSFF | нет | |

| CP | Rd, Rr 0≤d≤31 0≤r≤31 | Сравнить | Rd-Rr | Z, C, N, V, H | |

| CPC | Rd, Rr 0≤d≤31 0≤r≤31 | Сравнить с учетом переноса | Rd-Rr-C | Z, C, N, V, H | |

| CPI | Rd, К 16≤d≤31 0≤K≤255 | Сравнить с константой | Rd-K | Z, C, N, V, H |

Таблица 3.2. Команды сдвигов и операций с битами

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| LSL | Rd 0≤d≤31 | Логически сдвинуть влево | Rd(n+1)ßRd(n), Rd(0)ß0, CßRd(7) | Z,C,N,V,H | |

| LSR | Rd 0≤d≤31 | Логически сдвинуть вправо | Rd(n)ßRd(n+1), Rd(7) ß0, CßRd(0) | Z,C,N,V | |

| ROL | Rd 0≤d≤31 | Сдвинуть влево через перенос | Rd(0) ßC, Rd(n+1)ßRd(n), CßRd(7) | Z,C,N,V,H | |

| ROR | Rd 0≤d≤31 | Сдвинуть вправо через перенос | Rd(7) ßC, Rd(n)ßRd(n+1), C ß Rd(0) | Z,C,N,V | |

| ASR | Rd 0≤d≤31 | Арифметически сдвинуть вправо | Rd(n)ßRd(n+1), n=0...6, Rd(0)ßC | Z,C,N,V | |

| SWAP | Rd 0≤d≤31 | Поменять нибблы местами | Rd(3...0) <–>Rd(7...4) | Нет | |

| BSET | s 0≤s≤7 | Установить флаг | SREG(s)ß 1 | SREG(s) | |

| BCLR | s 0≤s≤7 | Очистить флаг | SREG(s)ß 0 | SREG(s) | |

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| SBI | P,b O≤P≤31 0≤b≤7 | Установить бит в регистр I/O | l/0(P,b)ß 1 | Нет | |

| CBI | P,b 0≤P≤31 0≤b≤7 | Очистить бит в регистре I/O | l/0(P,b)ß 0 | Нет | |

| BST | Rd,b 0≤d≤31 0≤b≤7 | Переписать бит из регистра во флаг Т | Тß Rd(b) | Т | 1 |

| BLD | Rd,b 0≤d≤31 0≤b≤7 | Загрузить Т флаг в бит регистра | Rd(b) ß Т | Нет | |

| SEC | Установить флаг переноса | Сß 1 | С | ||

| CLC | Очистить флаг переноса | Сß0 | С | ||

| SEN | Установить флаг отрицательного значения | Мß1 | N | ||

| CLN | Очистить флаг отрицательного значения | Nß0 | N | ||

| SEZ | Установить флаг нулевого значения | Zß1 | Z | ||

| CLZ | Очистить флаг нулевого значения | Zß0 | Z | ||

| SEI | Установить флаг глобального прерывания | Iß 1 | I | ||

| CLI | Очистить флаг глобального прерывания | Iß0 | I | ||

| SES | Установить флаг знака | Sß 1 | S | ||

| CLS | Очистить флаг знака | Sß0 | S | ||

| SEV | Установить флаг переполнения | Vß 1 | V | ||

| CLV | Очистить флаг переполнения | Vß0 | V | ||

| SET | Установить флаг Т | Tß1 | T | ||

| CLT | Очистить флаг Т | Тß0 | T | ||

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| SEH | Установить флаг полу переноса | Нß 1 | Н | ||

| CLH | Очистить флаг полу переноса | Нß0 | Н | ||

| NOP | Выполнить холостую команду | Нет | |||

| SLEEP | Установить режим SLEEP | Нет | |||

| WDR | Сбросить сторожевой таймер | Нет |

Таблица 3.3. Команды пересылки данных

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| ELPM | Расширенная загрузка из памяти программ в регистр RO | R0ß (Z+RAMPZ) | Нет | ||

| MOV | Rd,Rr 0≤d≤31 0≤r≤31 | Копировать регистр | RdßRr | Нет | |

| LDI | Rd,k 16≤d≤31 0≤k≤255 | Загрузить непосредственное значение | RdßK | Нет | |

| LDS | Rd,k 0≤d≤31 0≤k≤65535 | Загрузить из ОЗУ | Rdß(k) | Нет | |

| LD | Rd,X 0≤d≤31 | Загрузить косвенно | Rd ß (X) | Нет | |

| LD | Rd,X+ 0≤d≤31 | Загрузить косвенно с постинкрементом | Rd ß (X), XßX+1 | Нет | |

| LD | Rd,X- 0≤d≤31 | Загрузить косвенно с преддекрементом | XßX-1, Rd ß (X) | Нет | |

| LD | Rd,Y 0≤d≤31 | Загрузить косвенно | Rdß(Y), | Нет | |

| LD | Rd,Y+ 0≤d≤31 | Загрузить косвенно с постинкрементом | Rdß(Y), YßY+1 | Нет | |

| LD | Rd,Y 0≤d≤31 | Загрузить косвенно с преддекрементом | YßY-1, Rd ß (Y) | Нет | |

| LDD | Rd,Y+q 0≤d≤31 0≤q≤63 | Загрузить косвенно со смещением | Rdß(Y+q) | Нет | |

| LD | Rd,Z 0≤d≤31 | Загрузить косвенно | Rd ß (Z) | Нет | |

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| LD | Rd,Z+ 0≤d≤31 | Загрузить косвенно с постинкрементом | Rd ß (Z), ZßZ+1 | Нет | |

| LD | Rd,-Z 0≤d≤31 | Загрузить косвенно с преддекрементом | ZßZ-1, Rdß(Z) | Нет | |

| LDD | Rd,Z+q 0≤d≤31 0≤q≤31 | Загрузить косвенно со смещением | Rd ß (Z+q) | Нет | |

| STS | k,Rr 0≤d≤31 0≤k≤65535 | Загрузить непосредственно в ОЗУ | (k) ßRr | Нет | |

| ST | X,Rr 0≤r≤31 | Записать косвенно | (X) ß Rr | Нет | |

| ST | X+,Rr 0≤r≤31 | Записать косвенно с постинкрементом | (X) ßRr, XßX+ 1 | Нет | |

| ST | -X,Rr 0≤r≤31 | Записать косвенно с преддекрементом | XßX-1, (X) ßRr | Нет | |

| ST | Y,Rr 0≤r≤31 | Записать косвенно | (Y) ßRr | Нет | |

| ST | Y+,Rr 0≤r≤31 | Записать косвенно с постинкрементом | (Y) ß Rr, YßY+ 1 | Нет | |

| ST | -Y,Rr 0≤r≤31 | Записать косвенно с преддекрементом | YßY-1, (Y) ß Rr | Нет | |

| STD | Y+q,Rr 0≤r≤31 0≤q≤63 | Записать косвенно со смещением | (Y+q)ßRr | Нет | |

| ST | Z,Rr 0≤r≤31 | Записать косвенно | (Z) ßRr | Нет | |

| ST | Z+,Rr 0≤r≤31 | Записать косвенно с постинкрементом | (Z) ß Rr, ZßZ+ 1 | Нет | |

| ST | -Z,Rr 0≤r≤31 | Записать косвенно с преддекрементом | ZßZ-1, (Z) ß Rr | Нет | |

| STD | Z+q,Rr 0≤r≤31 0≤q≤63 | Записать косвенно со смещением | (Z+q)ßRr | Нет | |

| LPM | Загрузить байт из памяти программ | R0 ß (Z) | Нет | ||

| IN | Rd,P 0≤d≤31 0≤P≤63 | Загрузить данные из порта I/O в регистр | RdßP | Нет | |

| OUT | P,Rr 0≤r≤31 0≤P≤63 | Записать данные из регистра в порт I/O | PßRr | Нет | |

| PUSH | Rr 0≤r≤31 | Сохранить регистр в стеке | STACK ßRr | Нет |

Таблица 3.4. Команды переходов

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов |

| RJMP | k -2K<k<2K | Перейти относительно | PC ßPC + k + 1 | Нет | |

| LJMP | Перейти косвенно | PCßZ | Нет | ||

| JMP | k 0<k<4M | Перейти | PCßk | Нет | |

| RCALL | k -2K≤k≤2K | Вызвать подпрограмму относительно | PC ß PC + k + 1 | Нет | |

| ICALL | Вызвать подпрограмму косвенно | PCßZ | Нет | ||

| CALL | k 0≤k≤64K | Выполнить длинный вызов подпрограммы | PCßk | Нет | |

| RET | Вернуться из подпрограммы | PC ß STACK | Нет | ||

| RETI | Вернуться из прерывания | PC ß STACK | I | ||

| CPSE | Rd,Rr 0≤d≤31, 0≤r≤31 | Сравнить и пропустить, если равно | If Rd=Rr then PC ß PC + 2 (or 3) | Нет | ½/3 |

| SBRC | Rr,b 0≤r≤31 0≤b≤7 | Пропустить, если бит в регистре очищен | if Rr(b)=0 then PC ß PC + 2 (or 3) | Нет | ½/3 |

| SBRS | Rr,b 0≤r≤31 0≤b≤7 | Пропустить, если бит в регистре установлен | If Rr(b)=1 then PC ßPC + 2 (or 3) | Нет | ½/3 |

| SBIC | P,b 0≤P≤31 0≤b≤7 | Пропустить, если бит в регистре I/O очищен | if l/O P(b)=0 then PC ß PC + 2 (or 3) | Нет | ½/3 |

| SBIS | P,b 0≤r≤31 0≤b≤7 | Пропустить, если бит в регистре I/O установлен | If l/O P(b)=1 then PC ßPC + 2 (or 3) | Нет | ½/3 |

| BRBS | s,k 0≤s≤7 -64≤k≤+63 | Перейти, если бит в регистре статуса установлен | if SREG(s)=1 then PC ß PC + k + 1 | Нет | ½ |

| BRBC | s,k 0≤s≤7 -64≤k≤+63 | Перейти, если бит в регистре статуса очищен | if SREG(s)=0 then PC ß PC + k + 1 | Нет | ½ |

| BREQ | k -64≤k≤+63 | Перейти, если равно | if Rd=Rr (Z=1) then PC ß PC + k + 1 | Нет | ½ |

| BRNE | k -64≤k≤+63 | Перейти, если не равно | if Rd¹Rr(Z=0) then PC<ßPC+ k+ 1 | Нет | ½ |

| Мнемоника | Операнды | Описание | Операция | Флаги | Кол-во циклов | |||

| BRCS | k -64£k£+63 | Перейти, если флаг переноса установлен | if C=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRCC | k -64≤k≤+63 | Перейти, если флаг переноса очищен | if C=0 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRSH | K -64≤k≤+63 | Перейти, если равно или больше (без знака) | if Rd<Rr(C=0) then PCßPC+ k+ 1 | Нет | 1/2 | |||

| BRLO | k -64≤k≤+63 | Перейти, если меньше (без знака) | if Rd<Rr (C=1) then PC ßPC + k + 1 | Нет | 1/2 | |||

| BRMI | k -64≤k≤+63 | Перейти, если минус | if N=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRPL | k -64≤k≤+63 | Перейти, если плюс | if N=0 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRGE | k -64≤k≤+63 | Перейти, если больше или равно (с учетом знака) | if Rd>Rr (NÅV=0) then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRLT | k -64≤k≤+63 | Перейти, если меньше чем (со знаком) | if Rd<Rr (NÅV=1)then PC ßPC + k+ 1 | Нет | 1/2 | |||

| BRHS | K -64≤k≤+63 | Перейти, если флаг полупереноса установлен | if H=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRHC | k -64≤k≤+63 | Перейти, если флаг полупереноса очищен | if H=0 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRTS | k -64≤k≤+63 | Перейти, если флаг Т установлен | if T=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRTC | k -64≤k≤+63 | Перейти, если флаг Т очищен | if T=0 then PC ß pc + k + 1 | Нет | 1/2 | |||

| BRVS | k -64≤k≤+63 | Перейти, если флаг переполнения установлен | if V=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRVC | k -64≤k≤+63 | Перейти, если флаг переполнения очищен | if V=0 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRIE | k -64≤k≤+63 | Перейти, если глобальное прерывание разрешено | if I=1 then PC ß PC + k + 1 | Нет | 1/2 | |||

| BRID | k -64k£k£+63 | Перейти, если глобальное прерывание запрещено | if I=0 then PC ß PC + k + 1 | Нет | 1/2 | |||

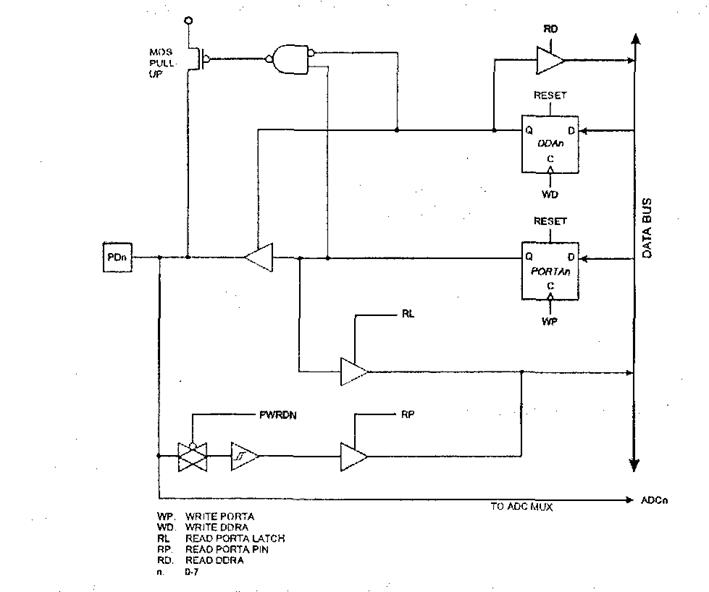

ПОРТЫ ВВОДА-ВЫВОДА

При арифметических операциях используется регистр состояния SREG, располагаемый по адресу $3F($5F). Формат этого регистра следующий:

2015-07-21

2015-07-21 521

521