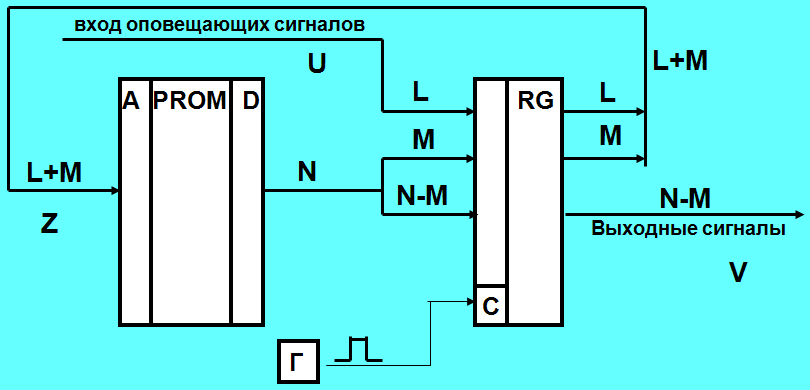

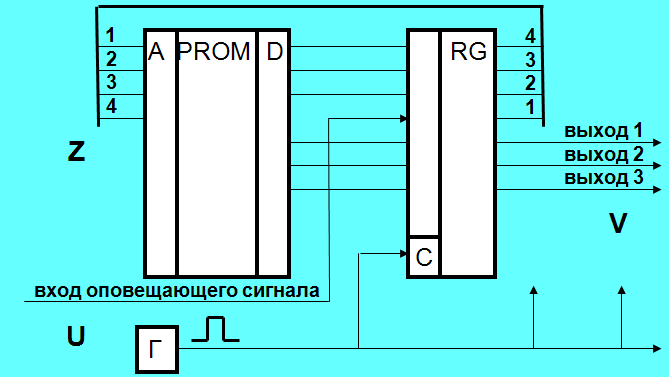

Схема микропрограммного автомата синхронизируется с элементами остальной схемы с помощью генератора синхроимпульсов «Г». ППЗУ является энергонезависимой долговременной памятью и синхронизации не подлежит, т.к. выдает данные на выход при появлении на входе адреса памяти. Для сопряжения ППЗУ с остальной схемой используется регистр.

Порядок построения простой горизонтальной микропрограммы для микропрограммного автомата схемы генерации сигналов.

В ответ на положительный фронт входного сигнала надо выработать три выходных сигнала, "вложенных" один в другой. Во время формирова-ния выходной последовательности автомат не должен реагировать на входной сигнал, а после ее окончания должен ожидать следующего положи-тельного фронта на входе.

Для упрощения задачи примем все временные сдвиги равными 1 мкс. Поэтому частота тактового генератора должна быть 1 Мгц.

Как видно из временной диаграммы, выходная последовательность состоит из шести тактов (включая все единичные уровни). Поэтому требует-ся 3 адресных входа ППЗУ (8 возможных состояний). Но помимо этого есть один входной сигнал, значит количество адресных разрядов ППЗУ будет 4, а количество разрядов регистра должно быть равно 7 (еще добавится три выходных сигнала). Схема примет вид, показанный на рисунке.

Теперь составим прошивку ППЗУ для нашего автомата (таблица).

Нетрудно заметить, что здесь реализованы следующие режимы:

1. Последовательный перебор адресов (при отработке выходной последовательности).

2. Останов с ожиданием.

3. Отключение реакции на входной сигнал (путем дублирования последовательного перебора в зоне адресов, соответствующей изменению входного сигнала).

| Адрес ППЗУ | Данные ППЗУ | Комментарий | ||||||||

| Вх | Текущий адрес | Выходы 1 2 3 | Следующий адрес | |||||||

| 1. Ожидание входного сигнала | ||||||||||

| 2. Отработка выходной последовательности при условии, что входной сигнал постоянно находится в состоянии логической единицы | ||||||||||

| 3. Ожидание снятия вх. сигнала | ||||||||||

| 4. Отработка выходной последовательности при снятии входного сигнала до окончания | ||||||||||

| 5. Переход на ожидание входного сигнала | ||||||||||

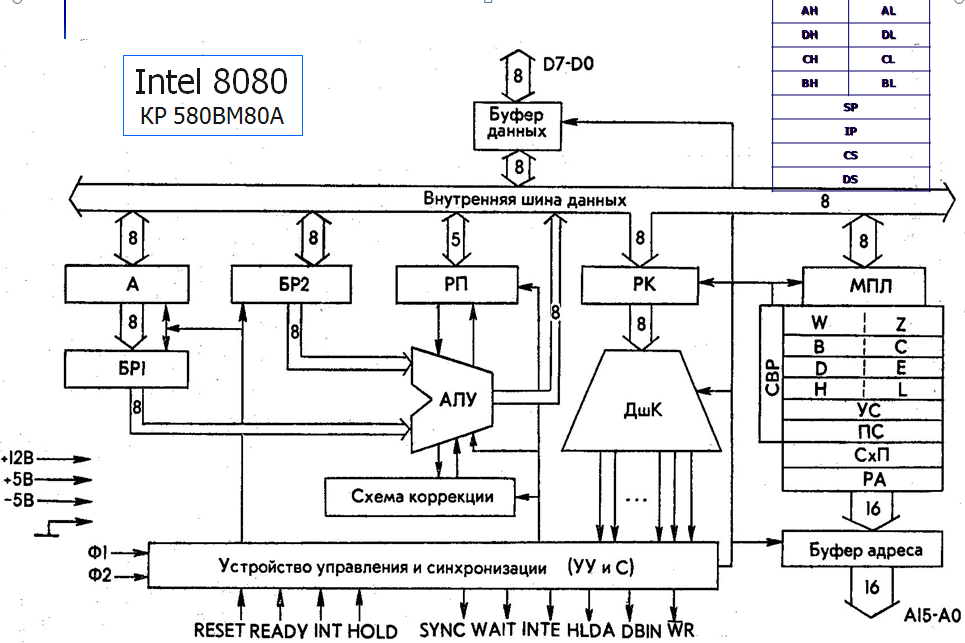

16 Базовая схема центрального микропроцессора.

А - регистр аккумулятор,

БР1, БР2 – буферные регистры,

РП - регистр признаков (флагов) – слово состояния ЦП,

АЛУ - арифметическое логическое устройство – сумматор,

РК - регистр команд (регистр приема кода операции),

ДшК - дешифратор команд (дешифратор кода операции),

МПЛ - мультиплексор выбора регистров,

СВР - схема выбора и подключения регистров к шине данных,

B, C, D, E, H, L, W, Z – блок 8-разрядных регистров общего назначения,

УС - 16-разрядный регистр – указатель стека,

ПС - программный счетчик (счетчик команд),

РА - 16-разрядный регистр адреса,

СхП - схема приращения адреса.

Внешние сигналы:

RESET - сигнал начальной установки состояния процессора,

READY - сигнал готовности памяти или порта ввода/вывода к обмену данными

INT - сигнал запроса на прерывание (от контроллера прерываний),

HOLD - сигнал запроса на захват шины (от контроллера прямого доступа),

SYNC - сигнал сопровождения выдачи на шину данных слова состояния ЦП,

WAIT - сигнал ожидания готовности READY,

INTE - сигнал разрешения прерывания выполнения программы,

HLDA - сигнал подтверждения захвата шины,

DBIN - сигнал, подтверждающий, что буфер данных включен на чтения,

WR - сигнал, подтверждающий, что буфер данных включен на запись,

Ф1, Ф2 - сигналы генератора синхронизации с различным сдвигом фаз.

2015-08-21

2015-08-21 1111

1111