Якісний стрибок у розвитку мікропроцесорних систем відбувся з появою мікропроцесора 8086. Але цей прогрес було досягнуто ціною збільшення кількості команд, ускладненням системи адресації та, у цілому, значним ускладненням програмування. Подальше удосконалення мікропроцесорів і створення таких процесорів, як 80286, 80386, 80486 ще більше ускладнило роботу з ними.

Тоді саме було встановлено; що далеко не всі команди застосовуються однаково часто. Лише невелика частина їх охоч'е використовувалась програмістами (близько 20 %), тоді як решта (80 %) застосовувалась вельми рідко. З цієї причини ще наприкінці 70-х років було висунуто "революційну" пропозицію - скоротити список команд процесора, обмежившись лише найнеобхіднішими. А більш складні операції виконувати за допомогою цих простих команд. Так виник новий напрямок у архітектурі мікропроцесорних систем -Reduced Instruction Set Computer, себто комп'ютер зі скороченим комплектом команд. Такі процесори й комп'ютери дістали назву RISC-процесорів та RISC-комп'ютерів на відміну від процесорів та комп'ютерів зі складною системою команд Complex Instruction Set Computer (CISC-комп'ютер).

Перший "справжній" RISC-комп'ютер було створено наприкінці 70-х років в університеті Берклі. Він обходився 31 командою. Усередині 80-х років з'явилися вже RISC-процесори другого покоління з 75 командами. Але це було все ж значно менше, ніж у сучасного їм процесора 80386, в якого список команд складав кілька сотень.

Перелічимо основні ознаки, за якими RISC-процесори відрізняються від CISC-процесорів:

- скорочений (порядку 100) набір команд замість кількох сотень у CISC-процесорів. Команди мають простий, чітко визначений формат і передбачають небагато методів адресації;

- завдяки широко застосованій конвеєризації команд процесор видає кожного такту принаймі одну виконану команду. Для цього застосовуються конвеєрні лінії з жорсткою логікою, які при своєму функціонуванні не потребують керування мікрокомандами;

- усі команди обробки даних працюють лише з вмістом робочих регістрів, котрі завантажуються конвеєрним методом. Для цього робиться велика кількість робочих регістрів: 32, 64, навіть 128, а також містка багаторівнева кеш-пам'ять;

- застосовується метод динамічного виконання (оптимізуючої компіляції).

Сучасні RISC-процесори належать до групи суперскалярних процесорів. Нагадаємо, що векторним процесорами звуться процесори, які виконують багато команд паралельно й одночасно. Звичайно вони є багатопроцесорними системами.

Скалярні процесори обслуговують команди послідовно, одну за одною. Суперскалярні процесори, які вважаються підкласом скалярних, обробляють по кілька команд одночасно паралельно в декількох своїх внутрішніх конвеєрах.

Спочатку CISC і RISC-процесори сильно відрізнялися між собою. Але згодом вони починають зближатися, запозичуючи один від одного деякі елементи. Останнім "чистим" CISC-процесором був 80386-й, У 80486-ого вже є декілька запозичень від RISC-процесорів: конвеєрні лінії, внутрішній та зог ішній кеш, Ще більше таких запозичень є в Pentium та в процесорів шостого покоління.

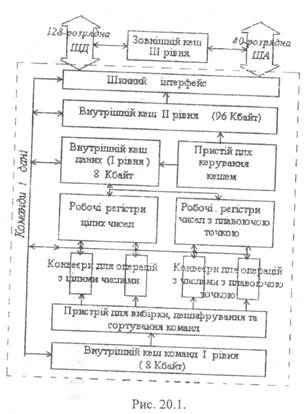

Особливості архітектури сучасних RISC-процесорів можна простежити на прикладі блок-схеми RISC-процесора третього покоління Alpha 21164 фірми DEC (рис. 20.1).

Як видно, архітектура цього процесора зовсім не схожа на архітектуру розглянутих нами раніше процесорів Intel-лінії.

Особливостями цього процесора є:

- наявність кеш-пам'ягі трьох рівнів - дві внутрішні (окремо для команд і для даних) та одна зовнішня;

- Замість АЛЛ, що керується мікрокомандами, у даного процесора є набір конвеєрів із жорсткою логікою. Ці конвеєри вузько спеціалізовані (наприклад, існують для додавання або віднімання цілих чисел або чисел із плаваючою точкою, для операцій зсуву, операцій розгалуження тощо).

Перш ніж потрапити на них, команди сортуються та спрямовуються на відповідний конвеєр. Конвеєри цього процесора досить "довгі" - вони складаються із семи ступенів для цілих чисел та з дев'яти для чисел із плаваючою точкою. Кожний конвеєр забезпечується певною кількістю робочих регістрів, до яких записуються вхідні дані та результати обчислень.

Перевагою такої системи є те, що, по-перше, пристрої з жорсткою логікою працюють швидше, аніж ті, які потребують мікропрограмного керування; по-друге, у цих конвеєрах можуть оброблятися одночасно й незалежно одна від одної декілька команд. Слід, однак, мати на увазі, що коли підряд ідуть кілька однотипних команд, то виникає черга до відповідного конвеєра, тоді як інші конвеєри простоюють.

Паспортні дані розглянутого RISC-процесора виглядають досить показово:

- шина адреси - 40 розрядів;

- шина даних -128 розрядів;

- тактова частота - 300 МГц (внутрішня); зовнішня частина ЕОМ може працювати з частотою в 3 - 15 разів меншою, щоб узгодити швидкодію процесора зі швидкодією оперативної пам'яті;

- продуктивність 1200 MIPS;

- кількість транзисторів 9.3 млн шт.; усі вони розташовані на кристалі площею 300 мм2.

- потужність теплорозсіювання становить 50 Вт, отже для охолодження процесора потрібний досить сильний вентилятор;

- собівартість $43 0; відпускна ціна $3000 (за станом на 1997 p.).

Цей процесор, розроблений фірмою Intel у 1992-93 pp., мав дістати, здавалося б, назву 08586. Але фірма з якихось причин віддала перевагу комерційній назві "Pentium". Ось деякі його паспортні дані:

- розрядність шини адреси -32;

- розрядність шини даних - 64;

- тактова частота - до 150 МГц;

- продуктивність - понад 100 MIPS;

- кількість транзисторів на кристалі більше ніж 3 мли шт. при розмірах 0.8мкм;

- живлення від +5 В.

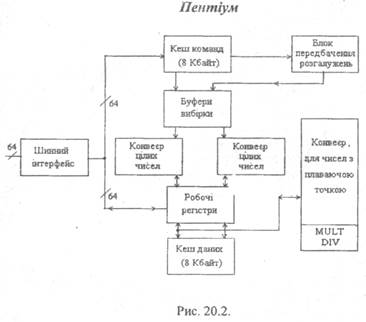

Структурну схему Pentium зображено на рис. 20.2.

Як видно, його архітектура істотно відрізняється від архітектури попередніх Intel-процесорів і більш нагадує архітектуру розглянутого вище RISC-процесора. Характерними особливостями архітектури Pentium є:

- 64 - розрядна внутрішня шина даних;

- два внутрішні кеша по 8 Кбайтів. окремо для команд і для даних (на відміну, наприклад, від i486, котрий має лише один загальний внутрішній кеш на 8 Кбайтів як для команд, так і для даних). Це дає можливість прискорити роботу процесора й виключає виникнення конфліктів на системній шині;

- Pentium може вважатися суперскалярним процесором, бо в його архітектурі передбачено два конвеєри, які паралельно виконують операції з цілими числами. Один із конвеєрів (U-конвеєр) має повний набір команд, другий (V-конвеєр) має дещо менший їх набір. Окремо створено конвеєр для роботи з числами з плаваючою точкою, У конвеєрах є лінії з жорсткою логікою, які спроможні виконувати певні етапи обробки даних без потреби мікрокомандного керування. У конвеєрах цілих чисел таких ділянок п'ять, а в конвеєрі для чис<?л із плаваючою точкою - вісім. У цьому самому блоці передбачені пристрої для апаратного підраховування найбільш важливих математичних функцій так, що цей блок можна вважати за вбудований математичний співпроцесор (як у i486).

- цікавою особливістю є блок передбачення розгалужень програми, який "переглядає вперед" програму, визначає місця можливих розгалужень і готується до них.

За швидкістю виконання команд із плаваючою точкою Pentium перевищує 486 DX у 10 разів, а 486 DX2 - у 2-3 рази. Завдяки достатньо великому внутрішньому кешу Pentium може працювати з частотою в кілька разів більшою, ніж усі інші блоки ПЕОМ.

Порівняння RISC і CISC процесорів

Природно виникає питання - яка ж архітектура краща - RISC чи CISC? Воно виникло одразу з появою перших RISC-процесорів і продовжує існувати досі, хоча, мабуть, наближається до свого вирішення. За цією суперечкою стоїть боротьба фірм, що спеціалізуються на розробці та виготовленню RISC та CISC-процесорів.

Зрозуміло, що паспортні дані RISC-процесорів виглядають значно вагоміше, аніж навіть у Pentium, не кажучи вже про більш ранні зразки CISC-процесорів. Але ЕОМ на RISC-процесорах значно дорожчі від CISC-ЕОМ (майже на порядок). RISC-ЕОМ працює лише з операційною системою UNIX, яка складніша від DOS або Windows і потребує більшого об'єму пам'яті.

Тому RISC-ЕОМ доцільно використовувати там, де такі високі параметри дійсно необхідні: для розв'язання особливо складних задач або в станціях, що обслуговують багато користувачів. Для звичайних користувачів ПЕОМ подібні RISC-машини "не по кишені", вони надто складні в роботі, а їхні високі параметри здебільшого зостаються нереалізованими. Можна, звичайно, увести RISC-машину в режим емуляції звичайної ПЕОМ. Але при цьому всі її вигоди втрачаються.

Щоправда, останнім часом ситуаі я починає дещо змінюватися. Ціна на RISC-ЕОМ поступово знижується, для них розробляються операційні системи, наближені до тих, котрі знайомі широким колам користувачів. З'явилась, наприклад, ОС Microsoft Windows NT, за якою може працювати RISC-ЕОМ і яка є близькою до звичайної Windows.

З іншого боку, CISC-процесори все більше запозичають від RISC-архітектури й відповідно наближаються до RISC-процесорів за своїми параметрами. Це ми вже простежили на прикладі i486 та Pentium. А процесори шостого покоління є вже й зовсім "RISC-подібними". Так що ці два напрямки в мікропроцесорній техніці, що так довго протистояли один одному, дедалі все більше наближаються один до одного.

попередників і ще більш наближує його до RISC-процесорів - це використання в ньому принципу динамічного виконання програм.

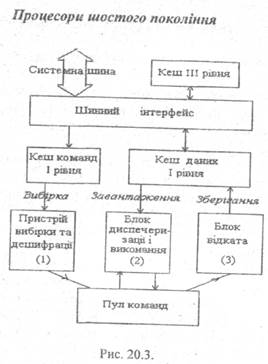

Нагадаємо - принцип динамічного виконання полягає в тому, що команди виконуються процесором не в тому порядку, в якому вони записані в програмі, а відповідно до їх готовності до виконання. Якщо в програмі зустрічається команда, для виконання якої потрібно перезавантажувати кеш, то процесор "обминає" її, відкладаючи виконання на час, коли всі потрібні дані будуть одержані. При цьому процесор не простоює, а виконує наступні команди, для виконання яких є все потрібне. Результат виконання цих команд тимчасово зберігається в області пам'яті, яка має назву пул команд і видобувається звідти в міру того, як попередні команди виявляться виконаними. Для здійснення цієї ідеї процесор Р6 має своєрідну архітектуру (рис. 20.3). Пристрій для видобування команд переглядає команди, що зберігаються в кеші команд на 20 - ЗО команд уперед щодо існуючого стану лічильника команд і обирає ті з них, для виконання яких є всі готові дані. Дешифратор (1) виробляє для таких команд відповідні мікрокоманди й надсилає їх до виконання в блок (2). А ті команди, для виконання яких ще немає всього потрібного матеріалу, очікують коли ж він надійде. Блок (2) складається з чотирьох спеціалізованих виконавчих пристроїв:

- пристою для оперування з цілими числами;

- пристою для роботи з числами з ги ваючою точкою;

- двох пристроїв для обробки розгалужень, а також пристроя-диспетчера або розподілювача.

Останній сортує команди за їх характером і спрямовує їх до відповідного виконавчого пристрою. Результати виконання мікрокоманд (мікропрограм) записуються в пул. Там вони зберігаються, аж доки не будуть виконані всі попередні команди. За цим слідкує блок відкоту (3). Коли виявляється, що команда, з вини якої виникла затримка, вже виконана, блок відкоту спрямовує її результат до кеша даних першого рівня й зразу вслід за нею всі подальші команди, що були виконані заздалегідь і результати яких зберігалися в пулі. Отже, блок відкоту відновлює ту черговість команд, яка існувала в програмі.

Завдяки такій архітектурі процесор не простоює жодного такту, а якщо з виконанням деякої команди виникає затримка, переходить до виконання наступних. Ясна річ, що швидкодія процесора при цьому

Розробка процесора шостого покоління, що умовно називається Р6 (комерційні назви Pentium Pro та Pentium її), розпочалась фірмою Intel у 1990 р. і початок його масового випуску припадає на 1996-97 pp. Припускається, що пік його продажу припаде на 1999-2000 pp. Кількість транзисторів у цьому процесорі складає 5.5 млн шт. при розмірах окремого транзистора порядку 0.35 мкм, що наближається до фізично можливої границі. Продуктивність цього процесора досягає 250 MIPS. Тактова частота складає 150 МГц і більше. Напруга живлення 2.9 В, що зменшує розігрів процесора. У керамічному корпусі розташовані дві мікросхеми - власне сам процесор та кристал надшвидкої кеш-пам'яті другого рівня. Потужність розсіювання досить значна і може досягати 20 В.

Розробка процесора шостого покоління, що умовно називається Р6 (комерційні назви Pentium Pro та Pentium її), розпочалась фірмою Intel у 1990 р. і початок його масового випуску припадає на 1996-97 pp. Припускається, що пік його продажу припаде на 1999-2000 pp. Кількість транзисторів у цьому процесорі складає 5.5 млн шт. при розмірах окремого транзистора порядку 0.35 мкм, що наближається до фізично можливої границі. Продуктивність цього процесора досягає 250 MIPS. Тактова частота складає 150 МГц і більше. Напруга живлення 2.9 В, що зменшує розігрів процесора. У керамічному корпусі розташовані дві мікросхеми - власне сам процесор та кристал надшвидкої кеш-пам'яті другого рівня. Потужність розсіювання досить значна і може досягати 20 В.

У Р6 застосовані методи прискорення швидкодії, які добре зарекомендували себе в процесорах i486 та Pentium, багаторівнева кеш-пам'ять і декілька спеціалізованих виконавчих пристроїв конвеєрного типу. Але основною новацією, що відрізняє Р6 від його

істотно зростає. Метод динамічного виконання програм уже давно застосовувався в RISC-процесорах. Тепер він знайшов застосування в черговому поколінні процесорів лінії Intel.

Іншою цікавою новацією є наявність у процесора другої системної шини, через яку він спілкується зі своїм кешем другого рівня, змонтованому поруч із процесором на тому самому кристалі. Завдяки цьому розвантажується основна системна шина, по якій процесор тримає зв'язок з усіма іншими блоками ЕОМ.

2015-10-16

2015-10-16 1198

1198