При пошуку несправностей у аналогових системах діють таким чином: подаюті. на вхід пристрою деякий тест-сигнал і далі за допомогою вольтаметра та осцилографа простежують його проходження по схеї» і. Повинні бути відомі напруги та форми сигналу в різних контрольних точках справної схеми - ці штатні напруги та епюри наводяться звичайно в інструкції з експлуатації та ремонту пристрою. Той вузол, в якому вигляд сигналу починає відрізнятись від штатного й виявляється здебільшого місцем несправності.

У цифровій техніці такий простий метод виявляється непридатним. Будь-який окремий провідник у цифровій °хемі, що

оперує даними в паралельному форматі, несе на собі лише малу частину інформації, що знаходиться в даний момент у системі. Ця частка змінюється майже довільним чином при зміні сигналів, що циркулюють по системі.

Тут можна навести таку наочну аналогію: візьміть на сторінці друкованого тексту вертикальний рядок літер, що розташовані одна над одною, і спробуйте встановити зміст тексту. Тут кожний такий вертикальний рядок подібний до розряду в паралельному форматі.

Якщо сигнал, узятий з одного окремого розряду проосцилографувати, то одержимо якусь нерегулярну послідовність імпульсів. Виявити в ній якісь закономірності та зміст практично неможливо. До того ж виникає питання: який саме розряд шини даних або шини адреси слід обирати?

Друга трудність полягає в тому, що при подачі на вхід пристрою, який перевіряється, деякої тестової програми результат на виході може виявитись неоднозначним. У системі, що випробовується, можуть знаходитись тригери та регістри, й інформація, яка була раніше записана в них, може відбитися на характері вихідного сигналу. Тому тестові програми мусять бути досить великими й тривалими, щоб задіяти всі елементи й вузли (включаючи елементи з пам'яттю) і одержати при "прокручуванні" тестової програми однозначні та відтворювані результати.

Але навіть тоді, коли при проходженні тестової програми щастить домогтися відтворюваності результатів, вихідний сигнал буде періодичним лише на великих відрізках часу (порядку багатьох сотень та тисяч тактів), залишаючись на коротких проміжках часу псевдовипадковим. Тому третя трудність полягає в тому, щоб будь-яким чином подати інформацію, що міститься у вихідному тест-сигналі, у компактній та зрозумілій формі, за якою можна було б судити про справність або несправність пристрою, що перевіряється.

Підрахунок переходів

Широко застосовуваний і простий спосіб компактного подання подібних псевдовипадкових послідовностей полягає в тому, що підраховується кількість переходів сигналу від одного стану до іншого (наприклад, переходів від високого рівня до низького або навпаки). Одержане число може вказувати на справність або несправність роботи вузла. Кількість переходів має бути досить

великою, бо тест-програма повинна передбачати всебічний контроль вузла. Але при цьому мають бути виконані такі умови:

- підраховування переходів має відбуватися протягом чітко визначеного проміжку часу, що вимірюється кількістю тактів випробовуваного пристрою. Цей проміжок часу має назву часового вікна.

- у часовому вікні мусить виконуватись певна тест-програма, котра всебічно перевіряє роботу вузла. Тест-програма повинна бути періодичною, щоб можна було проконтролювати відтворюваність її результатів від кількох актів тестування. Початок тест-програми має бути жорстко прив'язаний до початку часового вікна.

Заздалегідь проаналізувати процедуру тестування та передбачити кількість переходів практично неможливо. Тому це число визначається експериментальне на деякій відомо справній схемі. У документації пристрою вказується, який мусить бути вірний (штатний) результат підрахунку переходів у кожного з вузлів (при заданому часовому вікні та тест-програмі). Збіг результатів тестування зі штатним дає підстави вважати схему справною, а розходження вказує на її несправність.

Метод підрахунку переходів дає задовільну ймовірність виявлення несправності системи. Досвід показує, що невиявлення несправностей за таким методом складає лише кілька відсотків.

Сигнатурний метод

Більшу ймовірність виявлення несправностей цифрових пристроїв дає сигнатурний метод. При цьому ймовірність невиявлення несправностей знижується до 10~2 - 10"3 %.

У сигнатурному методі використовуються ті самі поняття про часове вікно та тест-програму, що й у попередньому методі підрахунку переході". Але тепер уже враховуються й запам'ятовуються не кількість переходів між рівнями, а конкретне значення сигналу в кожному такті. З першого погляду це здається неможливим, бо оброблювані часові послідовності можуть бути вельми великими й тривати багато тисяч тактів. Однак у сигнатурному методі вдається якоюсь мірою це зробити.

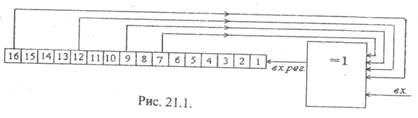

Принципову схему сигнатурного аналізатора зображено н рис. 21.1. Вона складаегься із зсувного регістра (у даному випадку -

точно таке число. Це число має назву сигнатури даної послідовності та подає її в стиснутій і компактній формі. Одержання сигнатур робиться таким чином:

- вміст зсувного регістра обнульовується;

- випробовувана система стимулюється до роботи заданою тест-програмою;

- випробування триває протягом певного числа тактів (часового вікна);

- протягом часу випробування вхід сигнатурного аналізатора має бути підключеним до випробуваного вузла й по закінченні часового вікна в регістрі залишиться сигнатура даного вузла від даної тест-програми.

Передбачити заздалегідь, якою має бути одержана сигнатура від того чи іншого вузла, практично неможливо. Тому вірна сигнатура визначається для даного вузла експериментальним шляхом, від відомо справної схеми. Значення сигнатур (разом з їх тест-програмами) наводяться в технічній документації пристрою. Сигнатура цілком однозначно визначає справність вузла або приладу. Невідповідність сигнатури хоча б в одному розряді вказує на несправність випробовуваного приладу. Не може бути майже вірної сигнатури. Вона може бути або вірною, або невірною.

Схема сигнатурного аналізатора, що кладається з 16-розрядного зсувного регістра зі зворотними зв'язками з указаних розрядів, була запропонована фірмою Хьюлетт-Паккард і дістала зараз стану стандарту. Хоча, у принципі, можна було б робити регістр іншої величини й утворювати зворотний зв'язок з інших розрядів, стандарт Хьюлетт-Паккарда є науково обгрунтованим і вважається оптимальним.

Цією самою фірмою була введена й дістала повсюдного застосування в сигнатурних аналізаторах своя система символів для шістнадцаткових чисел, котра якоюсь мірою зручніша від загальноприйнятої (табл. 21.1).

16-розрядного) і вхідного логічного пристрою, що являє собою багаторозрядну схему нерівнозначності. Перед початком вимірів усі комірки регістра обнульовуються. Далі при кожному такті в наймолодший розряд (1) записується чергове значення вхідного сигналу, а всі раніше записані значення зсуваються на один розряд ліворуч. Якщо б усе було саме так, то в регістрі опинилися б записаними значення вхідних сигналів за чергові 16 тактів; далі записана інформація витискалася б із найстаршого розряду й втрачалася б.

Але в сигнатурному аналізаторі передбачений зворотний зв'язок між окремим розрядами регістра та його входом. Він здійснюється через багатовходову схему виключаючого АБО з 7, 9, 12 та 16 розрядів регістра. Указана на рисунку логічна схема має п'ять уводів і видає одиницю на вході регістра лише тоді, коли на її входах є непарна кількість одиниць.

Завдяки зворотному зв'язку сигнал, що проходить через регістр, не втрачається безповоротно, а певним чином "відбивається" на нових вхідних сигналах. Зсувний регістр набуває "пам'яті", завдяки якій біти, що пройшли крізь нього та давно втратилися, продовжують якось впливати на записані в ньому дані. Тому, якщо зупинити в деякий момент потік вхідних даних, у регістрі виявиться якесь 16-розрядне число, у формуванні якого взяли участь усі біти, які раніше проходили через регістр. За цим числом, звичайно, не можна зідтворити послідовність усіх попередніх вхідних сигналів, що його сформували. Але якщо б ми повторили експеримент і подали на вхід гаку саму послідовність імпульсів, то в регістрі було б зафіксовано

Таблиця 21.1.

Десяткова 0123456789111111

Шістнадцяткова 0123456789ABCDEF звичайна

Шістнадцяткова 0 123456 7 89ACFHPU Хьюлетт-Паккард

За допомогою сигнатурних аналізаторів можна випробовувати не лише складні мікропроцесорні системи, але й будь-які простіші цифрові пристрої. Слід лише визначитися щодо тест-програм і часових вікон.

Метод контрольних сум

Контрольні суми є дуже простим і ефективним способом перевірки роботи ПЗП і записаних до них даних.

Для складання контрольної суми підсумовуються підряд усі числа, записані в комірках ПЗП. Переповнення, що при цьому виникає, ігнорується; цікавими є лише два наймолодші шістнадцаткові розряди. Якщо хоча б у одній із комірок ПЗП було записано невірне число (або ПЗП його невірно відтворив), то ця помилка виявиться в контрольній сумі, незалежно від кількості доданків. Звичайно, можз трапитись так, що помилку в одному з доданків буде компенсовано помилкою в іншому. Але ймовірність такої компенсації вельми мала. Цим самим методом можна перевіряти й справність оперативних запам'ятовуючих пристроїв (наприклад, оперативну пам'ять ЕОМ). Для цього в усі комірки ОЗП попередньо завантажується якась константа (наприклад, 55Н або ААН) і потім підраховується контрольна сума.

Самоконтроль у ЕОМ

З ускладненням ЕОМ та мікропроцесорних систем першорядного значення набуває необхідність вбудованих до них систем самоконтролю. В ідеалі машина при вмиканні живлення повинна здійснювати самоконтроль усіх своїх вузлів і не запускатися при виявленні їх відмови. Вона має також указати на підозрювану секцію або вузел, щоб їх можна було легко знайти й замінити. Такими

системами самоконтролю тою чи іншою мірою обладнано всі сучасні електронно-обчислювальні машини1.

Ідея попереднього тестування полягає в тому, що перед випробуваним блоком програмою ставиться певна тест-задача, при виконанні якої будуть задіяні всі ресурси цього блоку. Якщо результат виконання виявиться вірним (штатним), то блок вважається

справним.

Найпростішим прикладом такого тестування, яке наочно робиться усіма машинами при їх запуску, є перевірка памяті - ПЗП та ОЗП. Ця перевірка робиться описаним вище методом контрольних сум. При цьому, крім самого ПЗП або ОЗП перевіряються також усі дешифратори адрес та шина даних.

Для перевірки портів з одного порту до іншого переганяються задані числа (так, щоб були задіяні всі біти). Уведене число порівнюється з виведеним. Інші складніші блоки перевіряються методом сигнатур за допомогою тест-програм, закладених у систему самоконтролю ЕОМ.

Метод емуляції

Емуляція - це процес, в якому одна більш складна і "висококваліфікована" система використовується для виконання функцій іншої, менш "кваліфікованої" системи. При цьому дії "нижчої1" системи, котрі звичайно виконуються апаратно, здійснюються "вищою" системою за рахунок її програмних можливостей.

Так, у мікропроцесорній техніці пристрій-емулятор може виконувати функції різних вузлів іншого мікропроцесорного пристрою, тимчасово на період тестування замінюючи їх. Дійсно, у радіоелектроніці одним з основних методів пошуку несправностей є метод заміщення: підозрюваний вузел або деталь замінюють відомо справним вузлом або деталлю. Якщо при цьому функціонування системи відновлюється, то джерело несправності виявляється знайденим.

1 Так, наприклад, усі процесори, починаючи з МП-386, здійснюють при своїй ініціалізації перевірку 75 - 90 % вузлів ПЕОМ.

Так само й емулятор замінює підозрюваний блок мікропроцесорної системи. Широкі програмні можливості існуючих ЕОМ дозволяють універсально використовувати машину-емулятор для заміни нею різних блоків випробуваної системи. При цьому, природно, емулятор треба, щоразу перепрограмовувати під функції блоку, котрий він має заміняти.

Логічний аналізатор

Описані вище методи перевірки роботи складних цифрових пристроїв дають лише інформацію про їх справність чи несправність і дозволяють, у кращому разі, визначити місце несправності. Але вони не дають жодних відомостей щодо протікання процесів у випробовуваних схемах і взаємовідносини сигналів у різних його частинах, що часто-густо являє значний інтерес для визначення характеру несправності.

На початку даної глави йшлося про те, що осцилографування сигналу, узятого з одного окремого розряду, не може дати скільки-небудь корисної інформації, оскільки сигнали передаються всередині ЕОМ здебільшого в паралельному форматі й на одній лінії шини даних, адреси або керування міститься лише її мала частина, за якою судити про процеси в машині дуже важко..Ллє якби перед нами була вся картина сигналів, що передаються по всіх лініях усіх шин і до того ж протягом досить тривалого відрізку часу, то така інформація могла б бути вельми корисною. Зіставляючи миттєві значення рівнів сигналів на різних лініях у різні моменти часу, можна було б виявити певні закономірності, за якими можна було б судити про роботу різних вузлів та міру їх справності.

Для цього міг би згодитися багатопроменевий осцилограф із пам'яттю, який був би здатний відображати на екрані хід кількох сигналів, узятих і різних точок схеми. Але промисловість виготовляє серійно лише двопроменеві осцилографи з пам'яттю, та й вони досить дорогі й складні. До того ж момент запуску їх розгортки нелегко прив'язати до початку інтервалу часу, протягом якого виконується цікава для нас частина програми. Зручнішим і доцільнішим виявляється спеціальний пристрій - логічний аналізатор який працює на основі цифрових методів обробки та зберігання інформації.

Логічний аналізатор - це прилад, який здійснює огляд і зберігання сукупності логічних сигналів у реальному масштабі часу й подає ці сигнали у формі, зручній для користувача. Існуючі логічні аналізатори можуть мати до 32 входів, на які подаються сигнали з відповідної кількості точок випробуваного пристрою (наприклад, з 16 ліній ША, 8 ліній ШД та 8 ліній ШК). Ці сигнали заводяться на довгі (до 64 комірок) зсувні регістри й зсуваються в них тактовими імпульсами від випробуваного пристрою. Таким чином, у зсувних регістрах логічного аналізатора - матриці 32 х 64 бітів - знаходиться поточна інформація про стан 32 сигналів на даний момент часу та ще й від 63 попередніх тактів. Ця інформація "біжить" по комірках регістрів і втрачається на їх виходах.

Задача полягає в тому, щоб зупинити цю інформацію в потрібний момент часу й подати її у формі, зручній для огляду. Для цього до початку роботи оператором закладається в спеціальний регістр певне кодове слово, з яким порівнюються сигнали, що надходять від випробуваного пристрою. Таким словом може бути декотра адреса, слово даних або певний керуючий сигнал. У момент, коли в потоці цифрових сигналів, що потрапляють на вхід аналізатора, зустрінеться подібне слово, воно буде впізнано схемою порівняння й зупинить роботу зсувних регістрів, зафіксувавши їх вміст.

Далі вміст цих регістрів буде виведений у зручній формі на дисплей. У найпростішому випадку це можуть бути оди щі та нулі, згруповані для зручності по чотири. Приклад такого зображення подано в таблиці 21.2.

Таблиця 21.2.

| Такт | Шина | адреси | Шина даних | ||||||

| п |

Тут по вертикалі йде стан даного розряду для послідовності тактів. По горизонталі біти групуються в тетради для ША, ШД та ШК.

Таблиця 21.3.

У більш досконалих приладах замість двійкових тетрад ця сам» інформація може бути подана у вигляді шістнадцаткових чисел';

(табл. 21.3). І нарешті, найбільш "розумні" прилади можуть переводити сигнали шини, даних у мнемонічний запис. У декотрих, логічних аналізаторах вміст регістрів видається у вигляді часових діаграм і на екрані монітора одержується картина, подібна до тої, яка б мала місце на багатопроменевому осцилографі з пам'яттю.

Відтворюючи фрагмент за фрагментом | (по 64 такти в кожному фрагменті), можна проглянути таким чином | усю програму. Робота ЕОМ буде як на долоні - можна спостерігати роботу всіх її вузлів упродовж усієї програми. До цього ж слід і додати, що зупинку з упізнання кодового слова можна прив'язати не тільки до моменту його одержання (у цьому разі ми побачимо 64 такти, що передували цьому слову), але й через 64 після впізнання кодового слова (тоді ми побачили б 64 такти, наступні за цим словом). Можна реалізувати також усі проміжні варіанти, спостерігаючи фрагменти програми, що розміщені перед кодовим словом або після нього.

| Такт ША | ШД |

| 0 6ВЗС | ЗЕ |

| 1 52А2 | С9 |

| 2 7F98 | |

| n C65D | А1 |

ЗМІСТ

Передмова..................................................................

Лекція 1. Системи числення, які застосовуються в мікропроцесорній техніці. (Двійкова система числення. Шістнадцяткова й вісімкова системи числення. Переведення чисел з одної системи числення в іншу. Арифметичні дії з двійковими числами. Доповняльний код. Операції математичної логіки.........

Лекція 2. Мікропроцесори та малі електронно-обчислювальні машини (загальні принципи). (Будова та принципи дії центральної частини малої" ЕОМ. Принципи фон Неймака. Загальна блок-схема малої ЕОМ. Структурна схема та дія мікропроцесора. Параметри, що характеризують можливості мікропроцесора або ЕОМ)...................................................

Лекція 3. Структура й архітектура мікропроцесора КР580ВМ80. (Деякі особливі режими роботи мікропроцесора. ЇМС мікропроцесора КР580ВМ80. Що таке програмна модель та архітектура мікропроцесора та ЕОМ).....................................

Лекція 4. Як працює мікропроцесор. (Ієрархія циклів. Тактові імпульси. Процедура введення даних у мікропроцесор операція читання з пам'яті. Різновиди машинних циклів. Слово стану).............................................................................

Лекція 5. Системний контролер. Керуючий пристрій. Мікропрограмування. (Що таке системний контролер. Робота керуючого пристрою. Мікропрограмування)............................

Лекція 6. Організація пам'яті мікропроцесорної системи. (Деякі елементи, що входять до складу систем пам'яті. Шинні формувачі. Дешифратори. Розширення пам'яті Організація звернень до пам'яті або до зовнішніх пристроїв)........................

Лекція 7. Робота із зовнішніми пристроями. Паралельний інтерфейс. (Методи обміну інформацією. Паралельний програмований інтерфейс (ПЛІ) та паралельний програмований адаптер (ППА). Режими роботи ППА. Керуюче слово та

програмування ІШ)............................................................

Лекція 8. Послідовний інтерфейс. (Формати передачі даних. Структурна схема УСАПП. Схема підключення УСАПП до

мікропроцесора. Лінії передачі даних за стандартом RS-232).......

\ Лекція 9. Переривання. (Організація переривань. Команда рестарту. Пріоритети переривань. Програмований контролер

переривань (ПКП)).............................................................

Лекція 10. Прямий доступ до пам'яті (ПДП). (Принцип прямого доступу до пам'яті (ПДП). Контролер ПДП. Призначення

виводів КПДП типу КР580ВТ57. Режими програмування КПДП. Робота в режимі обміну. Програмування КПДП).........„;,:...........

Лекція 11. Клавіатура та індикація. (Принцип роботи клавіатури. Принцип роботи системи індикації. Побудова знаків. Знакоформувач. Знакомісця. Формування сигналів. Синхроімпульси. Блок-схема формування знаків на дисплеї")......

Лекція 12. Мікропроцесор К1810ВМ86 (8086). (Структура мікропроцесорного пристрою на К1810ВМ86. Часові діаграми роботи процесора. Організація пам'яті. Організація переривань. Особливості адресації в МП-86). Структурна схема мікропроцесора К1810ВМ86)................................................

Лекція 13. Система команд та методи адресації в мікропроцесорі К1810ВМ86. (Неявна адресація. Регістрова адресація. Безпосередня адресація. Пряма адресація (абсолютна адресація). Непряма регістрова адресація. Індексна адресація. Базова адресація. Базово-індексна адресація. Відносна адресація..Перетворення адрес на операнди. Формати кодів команд МП-86)...

Лекція 14. Мультипроцесорні системи. (Послідовний спосіб арбітражу. Паралельний спосіб арбітражу. Робота процесорного модуля в мультипроцесорній системі. Магістраль MULTIBUS).....

Лекція 15. Робота зі співпроцесором. (Зображення чисел з плаваючою точкою в електронно-обчислювальних системах. Обгрунтування необхідності співпроцесора. Формати чисел у співпроцесорі К1810ВМ87. Його можливості. Вмикання співпроцесора. Блок-схема співпроцесора К1810 М87. Як працює співпроцесор Поняття про програмування співпроцесора)............

Лекція 16. Тенденції в розвитку мікропроцесорної техніки. (Мікропроцесор К1821ВМ25. Мікропроцесор Z-80. Мікропроцесор 8088. Мікропроцесори 80186 та 80188. Однокристальні мікро-ЕОМ. Набори мікросхем або chipset. Навіщо були потрібні секціоновані мікропроцесори. Секціонований мікропроцесор)..............................................

Лекція 17. Деякі принципи роботи сучасних мікропроцесорів та ЕОМ. (Мультипрограмний режим роботи. Кеш-пам'ять. Подвоєння тактової частоти процесора. Черга команд. Конвеєризація адреси. Конвеєризація команд. Динамічне виконання (оптимізуюча компіляція)).....................................

Лекція 18. Віртуальна пам'ять. Мікропроцесор 80286.

(Принцип дії віртуальної пам'яті. Мікропроцесор 80286)............

Лекція 19. Мікропроцесори 80386 і 80486. Мікропроцесор 80386. Мікропроцесор 80486)...............................................

Лекція 20. Поняття про RISC-процесори. Процесори п'ятого та шостого поколінь. (Поняття про RISC-процесори. Пентіум. Порівняння RISC- і CISC-процесорів. Процесори шостого

покоління).......................................................................

Лекція 21. Діагностика несправностей у мікропроцесорних системах. (Проблеми, які виникають при аналізі сигналів у колах мікропроцесорних систем. Підрахунок переходів. Сигнатурний метод. Метод контрольних сум. Самоконтроль у ЕОМ. Метод

емуляції. Логічний аналізатор).............................................

Література......................................................................

2015-10-16

2015-10-16 469

469