Принципы работы делителей частоты приведены в книгах (2,3,6,7).

Делители частоты нашли широкое применение в вычислительной технике, устройствах автоматики, телемеханики, управления, бытовой технике.

Делителями частоты называются устройства, вырабатывающие М выходных импульсов в ответ на каждые N входных. Отношение N/М называется коэффициентом деления.

Делители частоты с любым коэффициентом деления строят на основе суммирующих или вычитающих счетчиков и логических элементов.

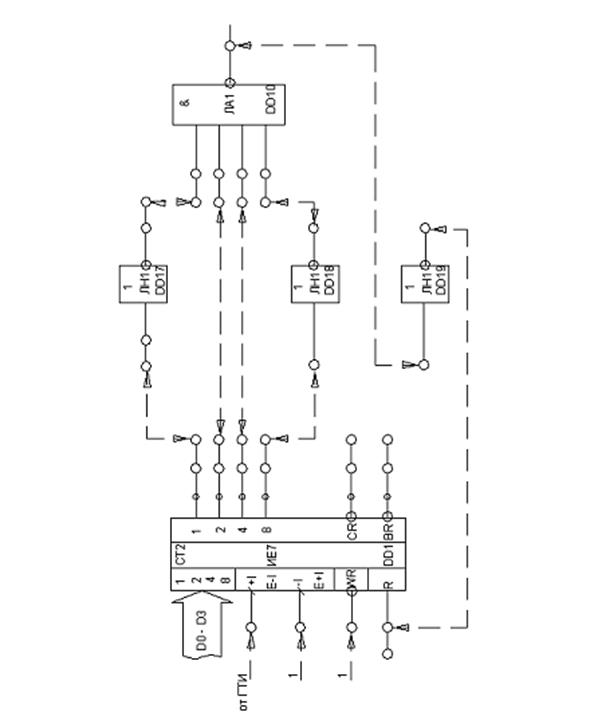

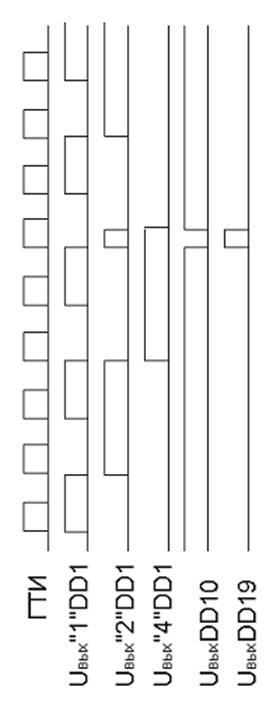

На рис.6.1 показана схема делителя частоты с коэффициентом деления 6, построенного на основе суммирующего двоичного счетчика, а на рис.6.2 представлены временные диаграммы его работы.

При поступлении шести импульсов на суммирующий вход счетчика его выходы установятся в следующее состояние – 0110, что соответствует цифре 6 в десятичной системе счисления. При этом на все четыре входа логического элемента DD10 поступают напряжения, равные по величине логической “1” и, следовательно, на выходе этого элемента возникает напряжение, равное логическому нулю. Элемент DD19 инвертирует его и уровень логической единицы, поступающий на вход R, сбрасывает счетчик в нулевое состояние. На выходе логического элемента DD10 появится уровень логической ”1”, на выходе элемента DD19 – уровень логического нуля, переводящий счетчик DD1 в режим счета. При дальнейшем поступлении входных импульсов цикл работы повторяется. Выходами делителя является выход DD10 (выходной импульс – “отрицательный”) или выход DD19 (выходной импульс – “положительный”). Подобным же образом строятся и другие делители частоты. В тех случаях, когда коэффициент деления можно разложить на множители, делители частоты можно сделать ступенчатыми, состоящими из нескольких делителей с коэффициентами деления, равными соответствующим множителям. Так, например, если необходимо построить делитель частоты на 24, то его можно образовать путем деления вначале на 2 (используя один счетный триггер), а затем выход этого делителя соединить со входом делителя на 12, построенного на интегральном счетчике DD1 и логических элементах по описанному выше принципу.

На рис.5.7,5.8 изображена схема и временные диаграммы работы делителя частоты с заданным коэффициентом пересчета, основанном на использовании вычитающего счетчика, имеющего режим параллельного занесения.

На входы D0 – D3 микросхемы DD1 подается двоичный код десятичного числа, равного коэффициенту деления. При подаче на вычитающий вход счетчика последовательности импульсов от ГТИ или ГОИ содержимое счетчика уменьшается и после поступления на вход счетчика количества импульсов, равного коэффициенту деления, счетчик обнуляется. На его выходе обратного переноса BR возникает перепад из “1” в “0”. Этот перепад поступает на вход разрешения параллельной записи WR и в счетчик снова заносится двоичное число, равное коэффициенту деления. После этого счетчик снова переводится в режим вычитания и цикл работы повторяется.

Выходом делителя является выход обратного переноса BR.

Рисунок 6.1 - Счетчик-делитель с коэффициентом деления 6

Рисунок 6.2 - Временная диаграмма работы счетчика делителя с коэффициентом деления 6

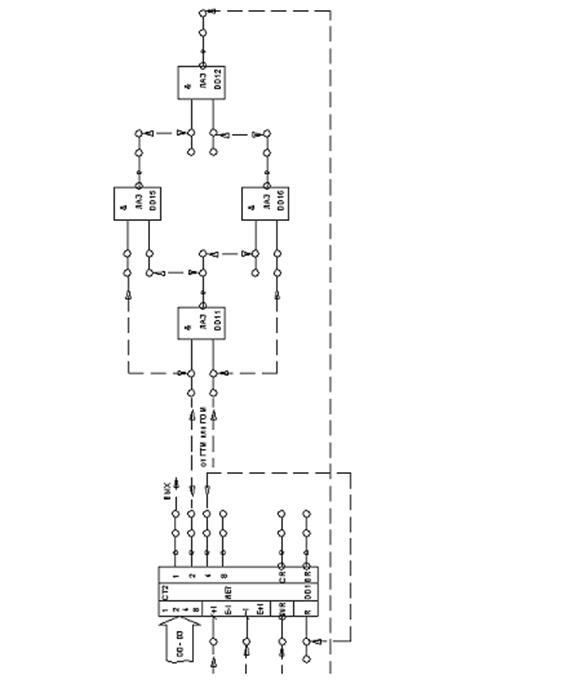

Рисунок 6.3 - Делитель частоты на 1,5

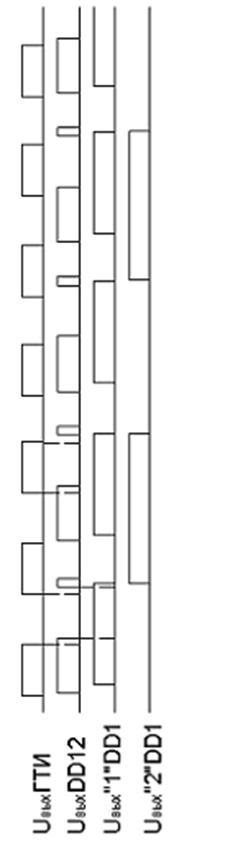

Рисунок 6.4 - Временная диаграмма работы делителя частоты на 1,5

На ри.5.11,5.12 представлена схема и временные диаграммы делителя частоты с коэффициентом пересчета 3*N, где N – любое число от 1 до 16. Схема представляет собой двухступенчатый делитель. Первая ступень делителя образована на основе микросхемы DD1 с коэффициентом деления N (от 1 до 16), вторая ступень делителя представляет собой триггерный двухразрядный счетчик – делитель на 3. При необходимости увеличения коэффициента деления разрядность двоичного счетчика необходимо увеличить. На рис.6.3 представлена схема делителя частоты с коэффициентом деления 1,5. Схема содержит двоичный счетчик DD1 и сумматор по модулю 2, выполненный на логических элементах 2”И-НЕ”. На счетный вход ”+I” счетчика поступает выходной сигнал схемы сумматора по модулю 2, а на входы схемы сумматора – тактовый сигнал и выходной сигнал со второго разряда счетчика. Если на выходе второго разряда счетчика устанавливается уровень логического нуля, то сигнал на выходе сумматора повторяет входной тактовый сигнал с учетом некоторой временной задержки. Если же на выходе второго разряда устанавливается уровень логической единицы, то тактовый сигнал на выходе сумматора инвертируется. Это приводит к увеличению количества переходов из “1” в “0” и из “0” в “1” на выходе схемы сумматора и вызывает дополнительные переключения счетчика DD1. В итоге на выходе ”1” счетчика частота сигнала меньше входной частоты не в 2, а в 1,5 раза, а на выходе ”2” – в 3 раза.

2015-10-13

2015-10-13 889

889