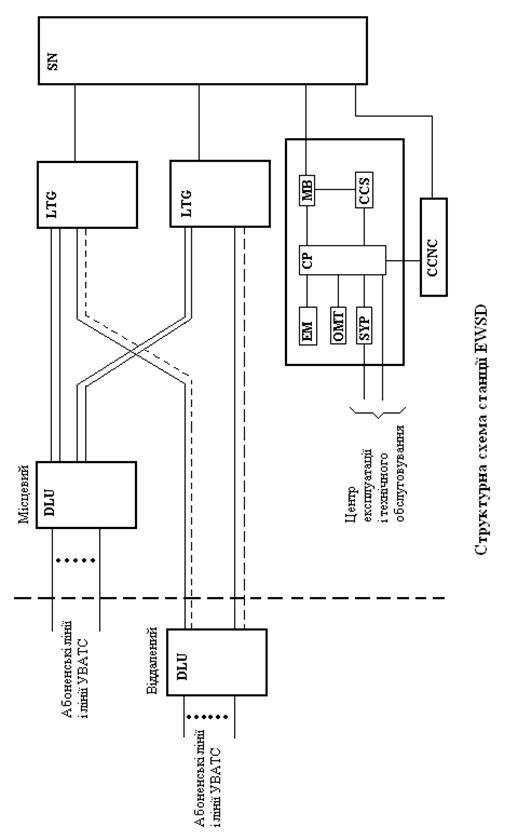

Структурна схема EWSD приведена на рисунку 5.5 і містить наступні підсистеми:

цифровий абонентський блок (DLU);

лінійна група (LTG);

комутаційне поле (SN);

керуючий пристрій мережі сигналізації по загальному каналу (CCNC);

координаційний процесор.

На блок-схемі також зображені зовнішній запам’ятовуючий пристрій (EM), термінал для експлуатації і техобслуговування (ОМТ), системна панель (SYP), буфер повідомлень (МВ) та центральний генератор тактової частоти (CCG).

Кожна підсистема має як найменш один власний мікропроцесор. З метою рівномірного розподілення навантаження і мінімізації потоків інформації між окремими підсистемами в EWSD використаний принцип розподіленого керування.

Абоненти підключаються в систему EWSD за допомогою цифрового абонентського блоку DLU. Блоки DLU встановлюються або на станції або на віддаленні від неї. Віддаленні DLU використовують в якості концентраторів.

Підключення DLU до лінійних груп LTG виконується за допомогою первинних цифрових систем передачі (PDC) зі швидкістю 2048 кбіт/с. З’єднувальні лінії до інших станцій або від них вмикаються в лінійні групи LTG.

Комутаційне поле з’єднує підсистеми LTG, CP i CCNC між собою. Воно забезпечує повнодоступність кожної LTG від (до) кожної LTG, CP або CCNC від кожної LTG, а в зворотньому напрямку - кожної LTG від CP чи CCNC.

Координаційний процесор 113 (СР 113) являє собою мультипроцесор, ємність якого нарощується модулями.

2015-10-22

2015-10-22 489

489