Логический элемент компьютера — это часть электронной схемы, которая реализует элементарную логическую функцию.

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, НЕ-И, НЕ-ИЛИ и другие (называемые обычно вентилями), а также триггер.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. В логических схемах производится преобразование информации, причем обычно у вентилей бывает от двух до восьми входов для входных сигналов и один или два выхода с которых снимаются выходные сигналы.

Чтобы описать схемы, которые строятся путем сочетания различных вентилей используется алгебра (алгебра логики) в которой все переменные и функции могут принимать только два значения: 0 и 1. Булева алгебра названа в честь английского математика Джорджа Буля (1815-1864). Алгебра логики оперирует с высказываниями. Высказывание – это повествовательное предложение, относительно которого можно утверждать, истинно оно или ложно. Над высказываниями можно производить определенные логические операции, в результате которых получаются новые высказывания. Для образования новых высказываний наиболее часто используются логические операции, выражаемые словами «не», «и», «или».

На структурных схемах ЭВМ каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Работу логических элементов описывают с помощью таблиц истинности булевой алгебры.

Логические операции. Рассмотрим логические операции и соответствующие им элементы логических схем.

Конъюнкция. Соединение двух (или нескольких) высказываний в одно с помощью союза И (AND) называется операцией логического умножения, или конъюнкцией. Эту операцию принято обозначать знаками «^, &» или знаком умножения «х». Сложное высказывание А & В истинно только в том случае, когда истинны оба входящих в него высказывания. Истинность такого высказывания задается табл. 1.15.

Таблица 1.15. Таблица истинности конъюнкции

| А | В | А&В |

| false | false | false |

| false | true | false |

| true | false | false |

| true | true | true |

Логическая схема И реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных диаграммах схемы И с двумя входами представлено на рис. а).

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет нуль, на выходе также будет нуль.

Связь между выходом z этой схемы и входами х и у описывается соотношением: z = х & у (читается как «х И у»). Операция конъюнкции на структурных схемах обозначается знаком «&».

Схемные логические элементы вычислительных машин

Дизъюнкция. Объединение двух (или нескольких) высказываний с помощью союза ИЛИ (OR) называется операцией логического сложения, или дизъюнкцией. Эту операцию обозначают знаками «|, v» или знаком сложения «+». Сложное высказывание A v В истинно, если истинно хотя бы одно из входящих в него высказываний.

Таблица истинности для логической суммы высказываний

| А ' | В | Av В | AXORB |

| false | false | false | false |

| false | true | true | true |

| true | false | true | true |

| true | true | true | false |

В последнем столбце табл. размещены результаты модифицированной операции ИЛИ — ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR). Отличается от обычного ИЛИ последней строкой (см. также рис. в, г).

Схема ИЛИ реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на ее выходе также будет единица.

Условное обозначение на структурных схемах схемы ИЛИ с двумя входами представлено на рис.б). Знак «1» на схеме — от классического обозначения дизъюнкции как «³1» (т. е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами х и у описывается соотношением: z = x Ú у (читается как «х ИЛИ.у»).

Инверсия. Присоединение частицы НЕ (NOT) к некоторому высказыванию называется операцией отрицания (инверсии) и обозначается `А (или А). Если высказывание А истинно, то В ложно, и наоборот (таблица).

| А | А |

| false | true |

| true | false |

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом х этой схемы и выходом z можно записать соотношением z = х, где х читается как «НЕ х» или «ИНВЕРСИЯ х».

Если на входе схемы «0», то на выходе «1», и наоборот. Условное обозначение на структурных схемах инвертора — на рис. в).

Вентили. Кроме схемных элементов, соответствующих перечисленным логическим операциям, в состав логических схем входят комбинированные связки, например следующие.

Схема НЕ-И состоит из элемента И и инвертора и осуществляет отрицание результата схемы И (табл.). Связь между выходом z и входами х и у схемы записывают как х& у, или «ИНВЕРСИЯ х И у». Условное обозначение на структурных схемах схемы И—НЕ с двумя входами представлено на рис. г).

Таблица истинности схемы НЕ-И

| X | У | (X&Y) ` |

| false | false | true |

| false | true | true |

| true | false | true |

| true | true | false |

Триггер.

Рассмотренные схемы, И, ИЛИ, НЕ не обладают памятью. В этих схемах информация на выходе присутствует до тех пор, пока присутствует информация на входе.

Триггер является элементом памяти, т.е. - это электронная схема, широко применяемая в регистрах компьютера для запоминания одного разряда двоичного кода. Триггер может находиться на одном из двух устойчивых состояний. Одному из этих состояний приписывается значение 1, а другому — 0. Состояние триггера распознается по его выходному сигналу.

Термин триггер происходит от английского слова trigger — защелка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье». Это звукоподражательное название электронной схемы указывает на ее способность мгновенно переходить («перебрасываться») из одного состояния в другое и обратно.

Самый распространенный тип триггера — так называемый RS-триггер (S и R соответственно от английских set — установка и reset — сброс).

Основные узлы ЭВМ

Сумматор

Используя основные логические схемы И, ИЛИ, НЕ и законы алгебры логики, можно строить и более сложные схемы — узлы ЭВМ. Сумматором называется узел ЭВМ, выполняющий арифметическое суммирование кодов чисел. Обычно сумматор представляет собой комбинацию однозарядных сумматоров, в которых осуществляется сложение трех цифр: цифры первого слагаемого, цифры второго слагаемого и цифры переноса из соседнего младшего разряда. В результате сложения получается цифра суммы для данного разряда и цифра переноса в следующий старший разряд. Рассмотрим принцип построения сложных схем на примере одноразрядного сумматора на два входа (ОС-2). Приведем пример из двоичной арифметики, т. е. правила выполнения суммирования лад двоичными числами:

0 + 0 = 0, 0+1 = 1, 1+0=1, l + l=0+ единица переноса в старший разряд.

Тогда ОС-2 можно представить как сложную схему с двумя входами А и В, на которые поступают знамения разрядов суммируемых чисел и двумя выходами С и П, на которых образуются значения суммы и переноса в следующий разряд соответственно.

Работа такого сумматора может быть определена следующей таблицей.

Таблицв А

| A | B | C | П |

Из таблицы видно, что перенос (П) равен единице в том случае, если присутствует информация на входе А и на входе В (т. е. A=B=l). Теперь составим другую таблицу, в которую занесем разные логические операции из значений А, В.

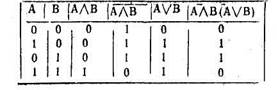

Таблица Б

Сравнивая таблицы А и Б мы приходим к выводу, что

C=(AÙB)(AÚB)

П= А/\В

На основании последнего выражения можно построить схему одноразрядного сумматора, логика которого oтpaжена в табл. А. Для построения такой схемы нам потребуется одна схема логического сложения (ИЛИ), две схемы логического умножения (И) и одна схема отрицания (НЕ). Надо предусмотреть, чтобы сигналы А и В одновременно (параллельно) поступали на входы схем логического сложения и умножения.

Аналогичным образом можно построить сумматоры и на большее число входов. Рассмотренный нами сумматор относится к типу сумматоров на основе комбинационных схем. Если же одноразрядные сумматоры выполнены на триггерах, то мы получим сумматор накапливающего типа.

Регистры

Регистр представляет собой совокупность триггеров, число которых соответствует количеству разрядов в машинном слове. Он выполняет следующие функции: запоминает и временно хранит код одного числа; преобразует последовательный код числа в параллельный и наоборот; сдвигает код числа на определенное количество разрядов вправо или влево (при выравнивании порядков или нормализации результата).

Регистр используется во всех устройствах ЭВМ. В запоминающем устройстве как элемент регистровой памяти, как информационный регистр, служащий для приема информации, считанной из памяти или для записи в память; в устройстве управления как регистр команд или как регистр, слова состояния программы, информация которого принимает участие в выполнении команд программы; а арифметическом устройстве как регистр для приема кодов чисел, считанных из оперативной памяти; в устройствах ввода-вывода как регистр, через который осуществляется обмен информацией между оперативной памятью и внешним устройством.

Счетчики.

Счетчик построен на триггерах, количество которых определяет его емкость, т. е. количество импульсов, которое он может сосчитать. Емкость счетчика определяется по формуле: 2n—1, где n — количество разрядов (триггеров) в счетчике. Единичные выходы триггеров соединены (через схемы логического умножения и линии задержки) со счетными входами триггеров соседних старших разрядов.

Он предназначен для подсчета электрических импульсов, поступающих на его вход. Счетчики используются для образования последовательностей адресов команд программы, для подсчета количества циклов выполнения операций и др.

Дешифраторы

Дешифратор представляет собой комбинационную схему, которая преобразует код, поступающий на входы, в сигнал на одном из выводов. Если на входы дешифратора подаются двоичные переменные, каждая из которых может принимать значения 0 или 1, то на одном из выходов дешифратора вырабатывается сигнал 1, а на остальных выходах сохраняются сигналы 0.

В общем случае дешифратор с N входами имеет 2N выходов, так как N разрядный код входного слова может принимать 2N различных значений и каждому из этих значений соответствует сигнал 1 на одном из выходов дешифратора.

Дешифраторы устанавливаются в схемах ЭВМ на выходах регистров или счетчиков и служат для преобразования кода слова, находящегося в регистре (счетчике), в управляющий сигнал на одном из выходов дешифратора.

Контрольные вопросы:

1. Логические элементы компьютера?

2. Регистр- это…

3. Дать определение триггера.

4. Логические операции?

Лекция №6

2015-10-22

2015-10-22 4608

4608