Лабораторна робота №2

Тема: Функціональна симуляція пристроїв у системі проектування Active-HDL

Мета: Засвоїти методику та отримати практичні навики створення та функціональної верифікації проектованих пристроїв в системі проектування Active-HDL

Теоретичні відомості

Послідовність проектування пристрою на функціональному рівні можна поділити на такі етапи:

Ø Створення файлів проекту: файли опису пристрою, тестових файлів, макросів.

Ø Компіляція файлів проекту.

Ø Симуляція на функціональному рівні.

Подальші кроки виготовлення конкретного пристрою вимагають наявності додаткових засобів для компіляції з функціонального VHDL опису пристрою у вентильний.

Active-HDL дозволяє створювати та редагувати різні компоненти такі як файли опису пристрою, використані в проекті бібліотеки, допоміжні файли, сукупність яких називається проектом (Design). Файли проекту за замовчуванням зберігаються в єдиній директорії, що носить назву проекту.

При запуску Active-HDL користувач повинен вибрати для роботи вже створений проект, або створити новий. По завершенні роботи з проектом, Active-HDL запам'ятовує встановлену користувачем конфігурацію системи, пов'язану з даним проектом.

Active-HDL дозволяє створювати резервні та архівні копії проекту. Це дозволяє повертатись до збережених раніше рівнів розробки у випадку виявлення архітектурних, чи функціональних помилок. Кількість резервних копій обмежується лише наявністю вільного місця на диску. При створенні архівної копії, всі файли, пов'язані з даним проектом поміщаються в заданий користувачем zip архів.

|

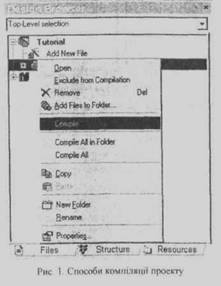

Для виконання наступного етапу проектування компілятор Active-HDL надає розробнику три способи компіляції (рис.1):

Ø Design/Compile - компіляція лише вибраного файлу;

Ø Design/Compile All- компіляція всіх файлів проекту в порядку їх створення;

Ø Design/Compile All in Folder - компіляція всіх файлів проекту, але на відміну від попереднього випадку, компіляція виконується враховуючи ієрархічні залежності.

|

Для виконання етапу симуляції необхідно вибрати Top Level проект у вікні Design Browser (рис. 2).

Для початку симуляції необхідно виконати ініціалізацію симулятора, використовуючи меню Simulation/Initilize Simulation. Далі необхідно відкрити нове вікно Waveform за допомогою кнопки. З'явиться вікно Waveform (рис. 3).

|

Далі у вікно необхідно додати сигнали, на які будуть подаватися стимули, а також сигнали, реакцію яких необхідно відслідковувати (рис. 4).

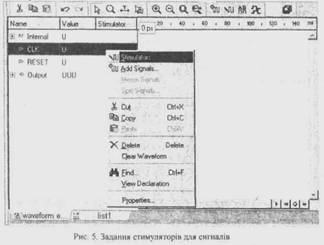

Для задання стимулів на відповідні сигнали використовується відповідне контекстне меню (рис. 5). Необхідно уникати задання будь-яких стимулів для сигналів, реакцію яких необхідно спостерігати.

Для задання стимулів на відповідні сигнали використовується відповідне контекстне меню (рис. 5). Необхідно уникати задання будь-яких стимулів для сигналів, реакцію яких необхідно спостерігати.

Після задання всіх сигналів стимуляції можна починати процес симулювання. Симуляція можлива, тільки за умови успішної компіляції. Існує три способи симуляції:

1. Simulation/Run - запуск симуляції без часового обмеження, симуляція припиняється при досягненні точки зупинки, або при втручанні користувача;

2. Simulation/Run For - запуск симуляції на заданий часовий інтервал;

3. Simulation/Run Until - виконання симуляції до моменту досягнення заданої часової відмітки.

|

В результаті виконання симулювання отримуємо часову діаграму роботи пристрою (рис. 6).

Active-HDL має потужні засоби відлагодження, зокрема:

Ø виконання коду в покроковому режимі;

Ø зупинка виконання коду при досягненні заданого рядку коду;

Ø зупинка виконання коду при зміні або набутті заданого значення вибоаним сигналом.

Існує три типи команд покрокової симуляції:  Trace Into,

Trace Into,  frace Over,

frace Over,  Trace Out.

Trace Out.

Результати симуляції динамічно відображаються у Waveform або/і List вікні. Додатково можна контролювати стан змінних, сигналів та процесів за допомогою вікон Watch та Process відповідно.

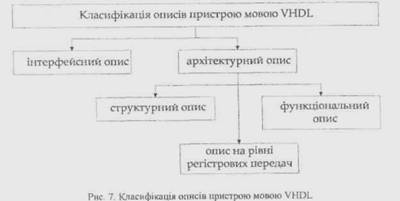

Для опису проекту мовою VHDL використовують два типи опису: інтерфейсний та архітектурний. Інтерфейсний опис призначений для опису проекту у вигляді чорного ящика з вхідними та вихідними портами. Архітектурний опис призначений для опису принципу функціонування проектованого пристрою, і в свою чергу поділяється на структурний, функціональний та на рівні регістрових передач. Структурний опис зручно використовувати при створенні архітектури проектованого пристрою, шляхом визначення функціональних зв'язків між компонентами проекту. Цей тип опису є традиційним описом для інженерів-схемотехніків. Функціональний опис використовується у випадку опису функціонування проектованого пристрою у вигляді алгоритму роботи проектованого пристрою мовою VHDL. Цей тип опису ближчий для інженерів-програмістів. Опис на рівні регістрових передач дозволяє описувати реакцію на вихідних портах проектованого пристрою, як результат логічних операцій над вхідними портами.

|

Обов'язковими для однозначного опису проектованого пристрою є інтерфейсний опис та один із архітектурних. На рис.7 зображено класифікацію описів пристрою мовою VHDL.

Порядок виконання роботи

1. Ознайомитись з викладеним вище теоретичним матеріалом.

2. Отримати індивідуальне завдання у викладача.

3. Синтезувати функціонально-логічну схему комбінаційного пристрою згідно індивідуального завдання.

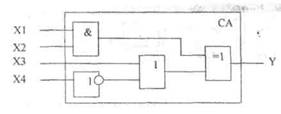

4. Розробити назву та графічне позначення комбінаційного автомату, вказавши назви та типи сигналів (вхід/вихід), наприклад (рис. 8):

5. Ознайомитись з наявною допоміжною документацією середовища Active-HDL.

6.

|

Завантажити систему симулювання Active-HDL. На запрошення системи (рис. 9) вибрати створення нового проекту (Create new design).

7.

|

Задати назву нового проекту, наприклад, Lab (рис. 10).

8.

|

Вибрати створення порожнього проекту (Create empty design) (рис. 11).

9. Після цього завантажиться основне вікно системи симулювання (рис. 12).

|

10.

|

У вікні броузера проекту (Design browser) вибрати правою клавішою миші додавання нового файлу (Add new file). У вікні створення нового файлу (рис. 13) обрати тип файлу (VHDL source code).

11.

|

Встановити прапорець додавання нового файлу до проекту (Add tfie generated file to the design) (рис. 14).

12.

|

Задати назву файлу для створення (бажано, щоб ця назва співпадала з назвою комбінаційного автомату, обрану у п. 4), задати назву пристрою - комбінаційного пристрою, обрану у п. 4, задати назву архітектури комбінаційного пристрою (рис. 15).

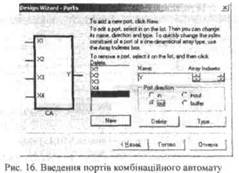

13. Використовуючи кнопку додавання нових портів до пристрою (New), поле назви порту (Name) та тип порту (Port direction), задати усі імена та типи сигналів комбінаційного пристрою. Після введення усіх портів вікно повинно мати такий вигляд (рис. 16):

|

14.

|

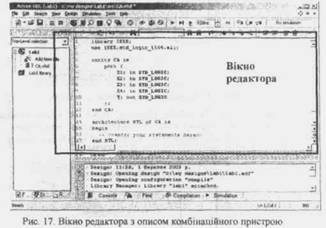

Після натискання кнопки "Готово", система симуляції автоматично згенерує VHDL файл з інтерфейсним описом комбінаційного пристрою та додасть його до проекту. Файл буде завантажений у вікно редактора для подальшого введення архітектурного опису комбінаційного пристрою (рис. 17).

15.

|

У секції архітектурного опису комбінаційного пристрою ввести декларації мови VHDL, які описують роботу комбінаційного пристрою згідно з отриманою схемою. Наприклад для схеми, що представлена на рисунку, декларації мови VHDL будуть такими:

Y <= (X1 and Х2) xor (Х3 or not(X4));

де "and", "xor", "or", "not" - логічні оператори мови VHDL, що відповідають логічним цифровим елементам, "<=" - оператор присвоювання сигналу.

Після введення інформації вікно редактора повинно мати вигляд:

library IEEE;

use IEEE.std_logic_l164.all;

entity CA is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

X3: in STD_LOGIC;

X4: in STD_LOGIC;

Y: out STD_LOGIC

);

end CA;

architecture RTL of CA is begin

Y <= (X1 and X2) хог (X3 or not(X4));

end RTL;

16. Перевірити правильність опису комбінаційного автомату шляхом компілювання файлу (кнопка F11). За необхідності виправити помилки.

17.

|

Вибрати описаний пристрій для симулювання. Для цього у вікні броузера проекту у полі вибору пристрою (Top level selection) вибрати скомпільований пристрій СА. Вікно броузера проекту повинно мати вигляд (рис. 18).

18.

|

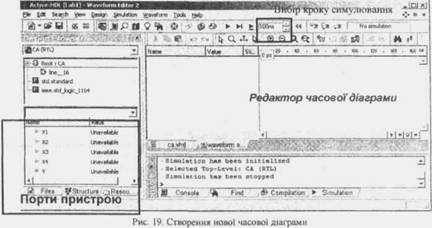

У броузері проекту вибрати закладку структури пристрою (Structure). Створити вікно з часовою діаграмою шляхом вибору пункту меню File -> New -> Waveform (рис. 19).

При виборі у броузері проекту пристрою СА у нижній частині вікна відобразяться вхідні і вихідні порти комбінаційного автомату.

19.

|

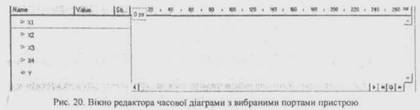

3адати часові діаграми для кожного вхідного сигналу комбінаційного автомату. Для цього у вікні портів пристрою вибрати усі порти комбінаційного автомату і перемістити їх на часову діаграму (для вибору портів утримувати кнопку Ctrl). Вікно редактора часової діаграми повинно мати вигляд (рис. 20)

20.

|

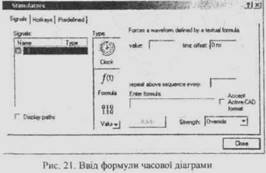

3адати часові діаграми для кожного вхідного порту (XI - Х4). Для цього почергово відмітити мишею необхідний порт, вибрати меню Waveform -> Stimulators... і задати формулу для часової діаграми у поле Formula (рис. 21).

Введення формули необхідно проводити таким чином, щоб забезпечити формування усіх комбінацій вхідних сигналів згідно з отриманим індивідуальним варіантом. Формат формули:

лог.рівень час ns, лог.рівень час ns,... лог.рівень час ns

|

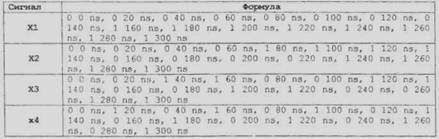

Наприклад, для формування усіх можливих комбінацій вхідних сигналів XI - Х4 можна задати такі формули:

Після введення формули для кожного порту необхідно натискати кнопку Apply. Також для задання вхідних послідовностей можна використати інші типи стимулів (наприклад Clock).

21.

|

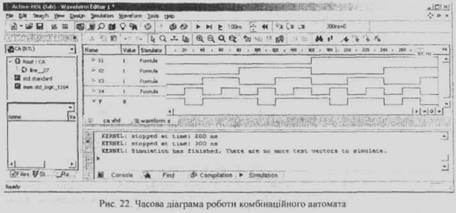

.Провести симулювання описаного-комбінаційного автомату. Для цього ініціалізувати симулювання шляхом вибору меню: Simulation -> Initilize Simulation. Встановити крок симуляції 100 ns (рис. 19). Симулювання можна проводити шляхом натискання кнопки F5 (покрокова симуляція). При цьому у редакторі часової діаграми буде відображатися зміна вхідних сигналів (згідно введених формул) та вихідного сигналу (згідно введеної VHDL конструкції у архітектурному описі комбінаційного автомата) (рис. 22).

Завершити симулювання шляхом вибору меню Simulation -> End Simulation. Перевірити правильність генерування вихідного сигналу згідно з індивідуальним завданням. За необхідності скоректувати архітектурний опис комбінаційного автомату.

Примітка: для переносу часової діаграми у звіт про виконання лабораторної роботи необхідно вибрати меню Waveform -> Edit Mode і у вікні редактора часової діаграми відмітити мишею часову діаграму. Після цього скопіювати часову діаграму у буфер обміну Windows (Ctrl-C).

22. Виконати структурний опис проектованого комбінаційного пристрою. Для цього схожим чином (пункти 10-14) необхідно добавити новий файл проекту типу Block Diagram. За допомогою засобів графічного редактора Block Diagram Editor скласти функціонально-логічну схему проектованого комбінаційного пристрою.

23. Повторити пункти 17-21 для отриманого структурного опису проекту.

24. Дати відповідь на контрольні запитання.

25. Скласти звіт з виконання лабораторної роботи та захистити його до початку виконання наступної лабораторної роботи.

3. Контрольні запитання

1. Назвіть послідовність етапів проектування пристроїв на функціональному рівні в Active-HDL.

2. Що таке функціональна верифікація проекту?

3. Які існують типи опису проекту мовою VHDL?

4. Які існують засоби покрокової симуляції? Поясніть їх призначення та основні відмінності.

5. Які існують засоби відображення результатів симуляції у Active-HDL?

6. Які типи стимуляторів передбачено у середовищі Active-HDL?

7. Наведіть класифікацію методів логічного моделювання в САПР.

Зміст звіту

1. Назва та зміст лабораторної роботи.

2. Відповідь на контрольні запитання.

3. Синтезована функціонально-логічна схема комбінаційного пристрою.

4. Інтерфейсний, на рівні регістрових передач та структурний описи синтезованого комбінаційного пристрою на мові VHDL.

5. Роздрук функціонально-логічної схеми проектованого пристрою, створеної засобами графічного редактору Block Diagram Editor.

6. Формули для задання вхідних сигналів.

7. Часові діаграми функціональної симуляції роботи пристрою.

8. Висновки.

2018-01-08

2018-01-08 718

718