Техническая реализация ЛУ на цифровых микросхемах

Техническая реализация ЛУ на базе диодной матрицы

Техническая реализация ЛУ на электромагнитных реле

Техническая реализация логических устройств на реальной элементной базе

|

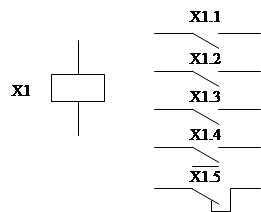

В выходных устройствах телемеханики систем электроснабжения применяются промежуточные реле РП-23. Преимуществом электромагнитных реле является гальваническая развязка слаботочных цепей ЛУ от сильноточных цепей исполнительных механизмов. Схема реле РП-23 представлена на рис. 3.1.

Рис. 3.1. Схема промежуточного реле РП-23

Реле содержит обмотку Х1, рассчитанную на ряд стандартных напряжений 24, 110 или 220 В, и пять групп контактов: четыре замыкающих контакта Х1.1 – Х1.4 и один размыкающий (инверсный) – Х1.5. Таким образом, одно реле может выполнять только одну операцию инверсии.

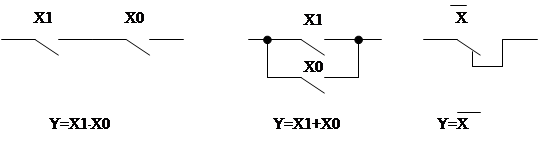

Логическая операция И выполняется на последовательно соединённых контактах реле, а логическая операция ИЛИ – на параллельно соединённых контактах. Пример выполнения логических операций на контактах реле представлен на рис. 3.2.

|

Рис. 3.2. Пример выполнения логических операций И, ИЛИ, НЕ на контактах реле

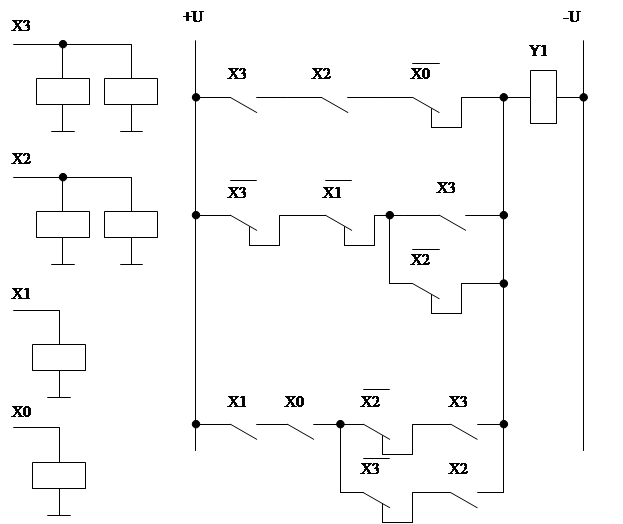

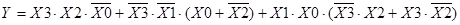

Чтобы построить логическое устройство на реле, необходимо сначала определить требуемое число реле РП-23. Для этого подсчитывают количество прямых и инверсных значений переменных в уравнениях ФАЛ. Предположим, имеется следующая ФАЛ:

. (3.1)

. (3.1)

Количество инверсных значение переменной одного типа, например Х3, показывает необходимое количество реле для реализации. Дополнительно количество прямых значений этой же переменной делят на 4 (число прямых контактов у одного реле), и проверяют, хватит ли прямых контактов. В выражении ФАЛ (3.1) количество инверсных значений переменной Х3 встречается два раза, прямых значений – тоже два раза, значит, потребуется два реле РП-23 для переменной Х3. Аналогично подсчитывается количество реле для переменных Х2 (2 штуки), Х1 (1 штука) и Х0 (1 штука). Схема логического устройства представлена на рис. 3.3.

|

Рис. 3.3. Схема логического устройства на контактах реле

Схема содержит реле входных переменных, которые выполняют первое действие в схеме автомата – инверсию. Цепочки контактов реле Х3, Х2, Х1 и Х0 построены в соответствии с уравнением ФАЛ. В схеме имеются две шины оперативного напряжения +U и –U, которые необходимы для питания выходного реле Y1. К этим шинам могут быть подключены и другие схемы логических устройств, например, для Y2 и Y3 и т.д.

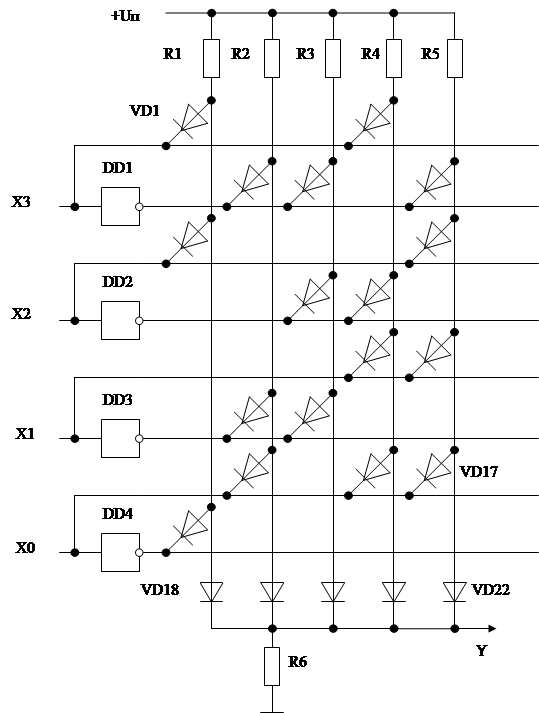

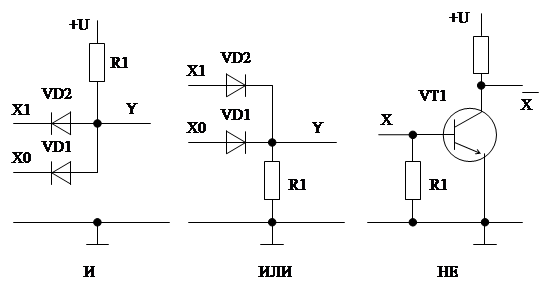

Диодные матрицы применяются в схемах согласования аппаратуры телемеханики с цепями внешних устройств, подлежащих контролю, а также для уменьшения количества промежуточных реле, если требуется произвести однотипную логическую операцию над большим числом входных переменных. Реализация логических операций в схемах с диодами представлена на рис. 3.4. Следует отметить, что на диодах невозможно осуществить инверсию сигнала, поэтому в качестве инвертора применяется ключ на транзисторе, включённом по схеме с общим эмиттером (ОЭ).

|

Рис. 3.4. Реализация логических операций И, ИЛИ, НЕ в схемах с диодами

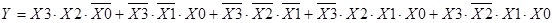

Порядок действий в схеме логического устройства на диодной матрице: инверсия, логическое умножение, логическое сложение. Диодная матрица не допускает изменения порядка действий введением скобок, поэтому ФАЛ для диодной матрицы должна иметь вид МДНФ без вынесения подобных членов за скобки. Преобразуем выражение (3.1) и составим схему по МДНФ из получившегося выражения:

. (3.2)

. (3.2)

Схема логического устройства на диодной матрице представлена на рис. 3.5. Для выполнения первого действия – инверсии - схема содержит 4 инвертора на элементах DD1…DD4. С их помощью создаются шины значений входных переменных  и

и  , которые служат горизонталями матрицы. Всего должно быть 2n шин при n входных переменных. В рассматриваемом примере 8 горизонтальных шин. Вертикали матрицы образованы шинами, подключёнными через резисторы R1…R5 к источнику +U. Количество вертикальных шин должно быть равно числу элементарных логических произведений в уравнении ФАЛ. В рассматриваемом примере 5 вертикальных шин.

, которые служат горизонталями матрицы. Всего должно быть 2n шин при n входных переменных. В рассматриваемом примере 8 горизонтальных шин. Вертикали матрицы образованы шинами, подключёнными через резисторы R1…R5 к источнику +U. Количество вертикальных шин должно быть равно числу элементарных логических произведений в уравнении ФАЛ. В рассматриваемом примере 5 вертикальных шин.

Для выполнения второго действия – логического умножения - диод, образующий соединение переменной в элементарном логическом произведении, подключается анодом к своей вертикальной шине, а катодом – к горизонтальной шине соответствующего значения переменной. Количество диодов, подключённых анодами к вертикальной шине, равно числу переменных в элементарном логическом произведении. В рассматриваемом примере к первой, второй и третьей вертикальным шинам подключается по три диода, а к четвёртой и пятой – по четыре. Всего используется 17 диодов VD1…VD17.

|

Рис. 3.5. Схема логического автомата на диодной матрице

Для выполнения третьего действия – логического сложения – вертикальные шины соединяют через диоды VD18…VD22, образующие вместе с резистором R6 схему ИЛИ. В рассматриваемом примере в уравнении ФАЛ складываются пять элементарных логический произведений, следовательно, требуется пять диодов. Выходной сигнал Y снимается с резистора R6.

Схема логического устройства на диодной матрице может наращиваться далее, к общим горизонтальным шинам через соответствующие диоды могут быть подключены другие вертикальные шины для элементарных логических произведений из ФАЛ для Y2, Y3 и т.д.

Цифровые микросхемы, на которых строится техническая реализация логических устройств, выпускаются сериями. В составе каждой серии имеются объединённые по функциональному признаку простые и сложные устройства – логические, счётные, арифметические, элементы памяти и т.д. Микросхемы одной серии имеют единое напряжение питания, конструктивное исполнение, одинаковые уровни логического нуля и логической единицы. Чем разнообразнее функциональный состав серии, тем большими возможностями может обладать электрическая схема – техническая реализация логического устройства.

Основой любой серии микросхем является базовый логический элемент. Обычно базовые логические элементы выполняют операции И-НЕ (штрих Шеффера) и ИЛИ-НЕ (стрелка Пирса). Наибольшее распространение получили два типа: транзисторно-транзисторная логика (ТТЛ) и комплементарные структуры металл – окисел –полупроводник (КМОП) или металл – диэлектрик – полупроводник (КМДП).

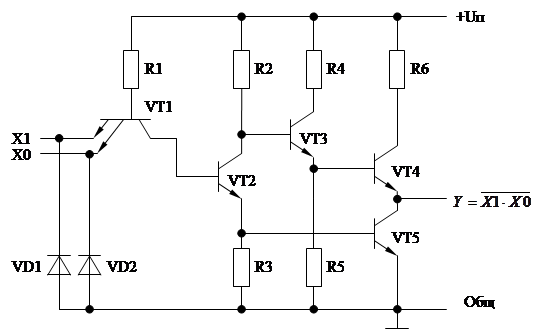

На рис. 3.6 представлена схема базового логического элемента ТТЛ.

|

Рис. 3.6. Схема базового логического элемента ТТЛ 2И-НЕ

На входе элемента включён многоэмиттерный транзистор VT1. Если на все входы элемента подать напряжение высокого уровня (логическую единицу), то эмиттерный переход VT1 будет закрыт. При этом ток, протекающий через резистор R1 и коллекторно-базовый переход VT1, откроет транзистор VT2. Ток, протекающий через транзистор VT2, будет создавать падение напряжения на резисторах R2 и R3, из-за которых закроются транзисторы VT3, VT4 и откроется транзистор VT5. В результате на выходе элемента будет низкий уровень напряжения (логический нуль). Если же хоть на один из входов подать логический нуль, то эмиттерный переход VT1 откроется, а транзисторы VT2 и VT5 закроются. Высоким уровнем напряжения с коллектора VT2 откроются транзисторы VT3, VT4, и на выходе элемента будет высокий уровень напряжения (логическая единица). Диоды VD1, VD2 защищают эмиттерный переход VT1 от выбросов напряжения отрицательной полярности, возникающих при переходных процессах.

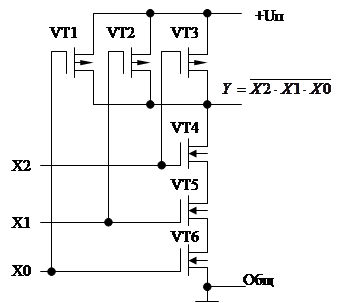

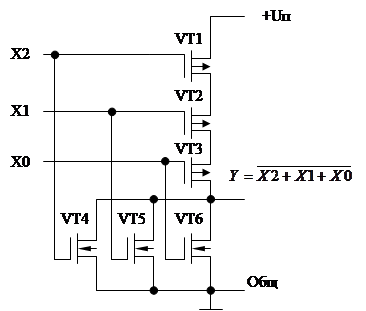

Из курса дисциплины «Электроника» известно, что комплементарная пара полевых транзисторов (с разным типом проводимости канала: p -канал и n -канал) является «идеальным» переключателем напряжения. При подаче на вход такого переключателя высокого уровня +U (логической единицы) закрывается транзистор с p -каналом и открывается транзистор с n -каналом. На рис. 3.7 представлены схемы базовых логических элементов И-НЕ (а) и ИЛИ-НЕ (б) микросхем серии КМОП.

а) |  б) б) |

Рис. 3.7. схемы базовых логических элементов И-НЕ (а) и ИЛИ-НЕ (б) микросхем серии КМОП

Рассмотрим работу элемента И-НЕ. Логический нуль на выходе такого элемента будет только тогда, когда на всех входах Х2, Х1, Х0 будут высокие уровни напряжения. Если хотя бы на один вход, например Х0, поступает низкий уровень напряжения, то закроется транзистор с n -каналом VT6 и откроется транзистор с p -каналом VT1, через который на выход поступит высокий уровень напряжения. Аналогичные рассуждения можно провести и для элемента ИЛИ-НЕ.

К основным параметрам логических элементов цифровых микросхем относятся напряжение источника питания, уровни напряжений логического нуля и логической единицы, нагрузочная способность, помехоустойчивость, быстродействие, потребляемая мощность.

Напряжение источника питания. Микросхемы ТТЛ рассчитаны на напряжение источника питания 5 В±10%, микросхемы КМОП – 9 В±10% (серия К176) и 3-15 В (серия К561 и другие на её основе).

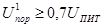

Уровни напряжений логического нуля и логической единицы. Различают пороговое напряжение логической единицы  - наименьшее напряжение высокого уровня на входе микросхемы и пороговое напряжение логического нуля

- наименьшее напряжение высокого уровня на входе микросхемы и пороговое напряжение логического нуля  - наибольшее напряжение низкого уровня на входе микросхемы, при которых происходит переключение логических элементов. Для микросхем ТТЛ

- наибольшее напряжение низкого уровня на входе микросхемы, при которых происходит переключение логических элементов. Для микросхем ТТЛ  = 2,4 В;

= 2,4 В;  = 0,4 В. Для микросхем КМОП

= 0,4 В. Для микросхем КМОП  ;

;  .

.

Нагрузочная способность – количество входов логических элементов, которые одновременно можно подключить к одному выходу без нарушения работы ЛУ. Количественно нагрузочная способность оценивается числом единичных нагрузок (коэффициентом разветвления). Единичная нагрузка – один вход базового логического элемента данной серии.

Помехоустойчивость базовых логических элементов оценивается в статическом и динамическом режимах. Статическая помехоустойчивость определяется уровнем напряжения, подаваемого на вход элемента относительно уровня логического нуля, при котором не происходит изменения состояния по выходу элемента. Для микросхем ТТЛ статическая помехоустойчивость составляет не менее 0,4 В, для микросхем КМОП – не менее 30% напряжения источника питания. Динамическая помехоустойчивость зависит от формы и амплитуды сигнала помехи, а также от скорости переключения логического элемента.

Быстродействие количественно можно выразить через предельную рабочую частоту переключения базового логического элемента fmax, а также через время задержки распространения сигнала tзд.

Потребляемая мощность для выходных сигналов логического нуля и логической единицы различна, поэтому потребляемая мощность в статическом режиме определяется как среднее значение этих величин. Для микросхем ТТЛ потребляемая мощность базового логического элемента составляет несколько мВт, для микросхем КМОП – несколько мкВт (в тысячу раз меньше).

Отдельно следует отметить надёжность микросхем, которая характеризуется интенсивностью частоты отказов базовых элементов. По статистическим данным интенсивность отказов составляет l = 1×10-7 1/ч.

Среди микросхем ТТЛ можно выделить три группы:

- стандартные – серии 155, 133;

- быстродействующие – серии 530, 531, 1531;

- маломощные – серии 555, 533, 1533.

Сравнительные характеристики различных серий микросхем ТТЛ представлены в таблице 3.1.

Таблица 3.1

Сравнительные характеристики базовых ЛЭ различных серий микросхем ТТЛ

| Серия | Р, мВт | tз, нс | fmax, МГц | Коэффициент разветвления по выходу |

Микросхемы КМОП можно разделить на две группы:

- быстродействующие – серии 561, 1561;

- стандартные – серия 176.

Сравнительные характеристики различных серий микросхем КМОП представлены в таблице 3.2.

Таблица 3.2

Сравнительные характеристики базовых ЛЭ различных серий микросхем КМОП

| Серия | Iп, мкА | Uп, В | tз, нс | fmax, МГц | Коэффициент разветвления по выходу |

| К561 | 0,1 | 3-15 | |||

| К176 | 0,1 |

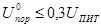

Конструктивное исполнение микросхем может быть в пластмассовом корпусе (К) или в металлокерамическом (КМ). Для микросхем в пластмассовом корпусе допустимый интервал температур окружающей среды составляет от -5 до +30 0С, в металлокерамическом - от -30 до +50 0С. На рис. 1.6 были представлены условные графические изображения элементов 2И-НЕ и 2ИЛИ-НЕ. В микросхемах ТТЛ и КМОП имеются различные варианты элементов, отличающиеся числом входов. Согласно ГОСТ 17467-79 цифровые микросхемы выпускаются в корпусе тип 201.14 (14 выводов) или тип 238.16 (16 выводов). Вид корпуса тип 201.14 представлен на рис. 3.8.

Рис. 3.8. Вид корпуса цифровой микросхемы тип 201.14

Из 14 выводов два служат для подачи напряжения питания (+Uпит и Общ., обычно это выводы 14 и 7), а остальные 12 могут быть использованы для ЛЭ. Поэтому в одном корпусе можно разместить 4 элемента 2И-НЕ, 3 элемента 3И-НЕ, 2 элемента 4И-НЕ или один элемент 8И-НЕ. Поэтому при технической реализации ЛУ на заданном типе микросхем может возникнуть две ситуации:

- число входных переменных меньше числа входов ЛЭ;

- число входных переменных больше числа входов ЛЭ.

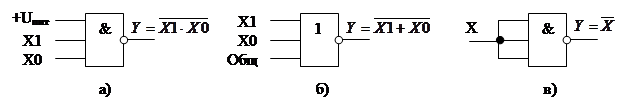

В первом случае у ЛЭ остаются свободные входы. На свободный вход можно подать неактивный уровень напряжения. Согласно теореме № 1 (таблица 1.7), для логического сложения это будет сигнал логического нуля, а для логического умножения – сигнал логической единицы. Можно также объединить свободный вход с входом, на который подан сигнал входной переменной. Частным случаем такого решения будет превращение многовходового элемента И-НЕ или ИЛИ-НЕ в инвертор, когда все входы элемента объединяются. Примеры таких действий представлены на рис. 3.9.

|

Рис. 3.9. Пример действий, когда число входных переменных меньше числа входов ЛЭ:

а – подача неактивного сигнала на элемент 3И-НЕ, б – подача неактивного сигнала

на элемент 3ИЛИ-НЕ, превращение элемента 3И-НЕ в инвертор

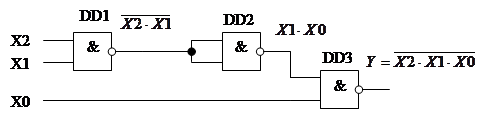

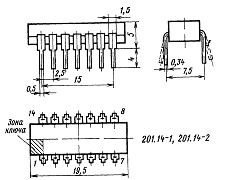

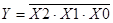

Во втором случае у ЛЭ не хватает входов для всех входных переменных. В такой ситуации приходится преобразовывать схему ЛУ. Рассмотрим случай, когда на элементах 2И-НЕ требуется реализовать схему для трёх входных переменных. Схема такого ЛУ представлена на рис.3.10.

Сначала производится умножение с инверсией входных переменных Х2 и Х1 на элементе DD1.Получается результат  . Затем сигнал с выхода элемента DD1 инвертируется элементом DD2, получается

. Затем сигнал с выхода элемента DD1 инвертируется элементом DD2, получается  . Этот сигнал на элементе DD3 умножается на Х0. На выходе схемы получается требуемый результат

. Этот сигнал на элементе DD3 умножается на Х0. На выходе схемы получается требуемый результат  .

.

|

Рис. 3.10. Схема для логического умножения трёх входных переменных на элементах 2И-НЕ

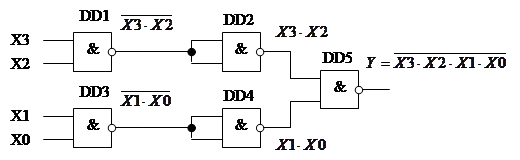

Схема для четырёх входных переменных строится по такому же принципу. Пример схемы представлен на рис. 3.11.

|

Рис. 3.11. Схема для логического умножения четырёх входных переменных на элементах 2И-НЕ

Воспользовавшись предложенным принципом, можно построить схему для любого числа входных переменных. Аналогичные схемы можно построить и для элементов 2ИЛИ-НЕ.

Контрольные вопросы

1. Почему схемы логических устройств выполняют на электромагнитных реле?

2. В чём заключаются особенности технической реализации логического устройства на электромагнитных реле? Как следует преобразовать ФАЛ для такой реализации?

3. В каких случаях техническую реализацию логического устройства выполняют на диодной матрице?

4. Каков порядок действий при реализации ФАЛ на диодной матрице? Приведите примеры выполнения логических операций И и ИЛИ на диодах.

5. Какой вид должна иметь ФАЛ для её реализации на диодной матрице?

6. Что такое базовый логический элемент цифровой микросхемы?

7. Почему логические операции И-НЕ (штрих Шеффера) и ИЛИ-НЕ (стрелка Пирса) выбраны для построения схем базовых логических элементов?

8. Нарисуйте схему базового логического элемента микросхемы ТТЛ. Объясните принцип работы схемы.

9. Нарисуйте схемы базовых логических элементов И-НЕ и ИЛИ-НЕ микросхем КМОП. Объясните принцип работы схем.

10. Перечислите основные параметры логических элементов цифровых микросхем.

11. Как следует поступить в случае, когда число входных переменных меньше числа входов ЛЭ? Приведите пример схемы.

12. Как следует поступить в случае, когда число входных переменных больше числа входов ЛЭ? Приведите пример схемы для трёх и четырёх входных переменных на элементах 2И-НЕ и 2ИЛИ-НЕ.

Типовым функциональным узлом называется цифровая микросхема, внутри которой собрана сложная схема на базовых логических элементах. Комбинационные логические устройства имеют следующие типовые функциональные узлы: мультиплексор, демультиплексор, шифратор (кодер), дешифратор (декодер) и цифровой компаратор. Кроме этого, к комбинационным логическим устройствам можно отнести специализированный ЛЭ – «Исключающее ИЛИ» и ЛЭ, реализующие сложные функции, например, И-ИЛИ-НЕ.

2014-01-31

2014-01-31 1361

1361