Рис. 1.14. Плата гибридной микросхемы

Рис. 1.13. Монтаж бескорпусного транзистора в гибридной микросхеме

Гибридные интегральные микросхемы

Рис. 1.12. Интегральный пленочный конденсатор

Рис. 1.11. Интегральный пленочный резистор

Гибридные микросхемы изготавливают на диэлектрической подложке, их пассивные элементы R, С, L, межсоединения и контактные площадки выполняют по пленочной технологии, т. е напылением. Применяют групповой метод обработки, при котором на одну подложку наносят до 16 — 18 идентичных групп элементов и межсоединений, затем подложку разрезают на части — платы каждая из которых содержит элементы и межсоединения одного функционального узла.

Транзисторы для гибридных микросхем изготавливают отдельно, в целях экономии объема в бескорпусном оформлении иногда в виде сборки. Их параметры имеют примерно те же численные значения, что и у дискретных аналогов. Бескорпусные транзисторы защищают от воздействий внешней среды специальным влагостойким покрытием.

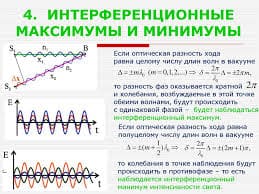

Монтаж транзистора 1 (рис. 1.13) на плате осуществляют термокомпрессионной сваркой шариковых 3 или балочных 5 выводов с контактными площадками 2 либо с помощью проволочных выводов.

Общий вид платы гибридной микросхемы показан на рис 1 14 а, На диэлектрическую подложку наносят через трафарет резистивные полоски Ri, R2, Rз из высокоомного материала, затем через другой трафарет распылением металла, имеющего высокую электропроводность, наносят нижнюю обкладку О, конденсатора С, межсоединения и контактные площадки 1 — 5. Далее через третий трафарет наносят пленку диэлектрика конденсатора Д и, наконец, через четвертый трафарет наносят последний слой — верхнюю обкладку конденсатора 02. Транзистор Т приклеивают к подложке и проволочными выводами подсоединяют к соответствующим контактным площадкам.

На рис. 1.14,6 показана принципиальная схема рассмотренного устройства. Оно функционально незавершено, поскольку может быть использовано (в усилителе с общим эмиттером, в эмиттерном повторителе и т. п.) лишь при подключении к нему ряда внешних элементов. Такая функциональная незавершенность обычно возникает из-за трудностей выполнения некоторых элементов (например, катушек) в виде, пригодном для монтажа внутри микросхемы. Иногда микросхему специально оставляют функционально незавершенной, чтобы расширить сферу ее использования.

Рассмотренная микросхема имеет один транзистор, один конденсатор и три резистора.

Выпускаемые промышленностью гибридные микросхемы во многих случаях значительно сложнее, число их элементов может достигать нескольких сотен.

Гибридные микросхемы могут выполняться и на основе толстопленочной технологии, более дешевой, но, как уже указывалось, менее совершенной. Подложка для толстопленочной микросхемы имеет размеры 16X10X1 или 10X10X1 мм и выполняется из высокоглиноземистой керамики, имеющей хорошую адгезию к наносимым материалам. Элементами толстопленочной микросхемы являются резисторы и конденсаторы, их выполняют так же, как и межсоединения, путем нанесения на поверхность подложки через сетчатый трафарет специальных проводящих, резистивных и диэлектрических паст, подвергаемых после нанесения термической обработке. Получаемые таким образом резисторы могут иметь сопротивление от 5 Ом до 70 кОм с разбросом (после подгонки) до 1 %, при удельной мощности рассеяния до 0,5 Вт/см2. Конденсаторы имеют емкость рт 60 до 350 пФ, добротность до 50, пробивное напряжение до 150 В. Температурный коэффициент у резисторов ±5-10~4 град-1, конденсаторов 4-10~4 град-1. Бескорпусные транзисторы и диоды монтируют в толстопленочных гибридных микросхемах обычным способом.

По числу содержащихся в корпусе микросхем элементов различают шесть степеней интеграции: первая степень — от 1 до 101; вторая — от 10 до 102; третья — от 102 до 103; четвертая — от 103 до 104; пятая — от 104 до 105; шестая — от 105 до 106 элементов.

Интегральные микросхемы, содержащие более 100 элементов, принято называть микросхемами повышенного уровня интеграции, используется также термин «большие интегральные схемы» (БИС) он соответствует четвертой-пятой степеням интеграции

Микросхемы повышенного уровня интеграции имеют по сравнению с микросхемами малого уровня интеграции значительно лучшие габаритные характеристики, меньшую стоимость в расчете на один функциональный элемент, а также ряд других преимуществ благодаря которым удается существенно улучшить основные технико-экономические характеристики аппаратуры.

Во-первых, значительно уменьшается число соединений в аппаратуре из-за большей функциональной сложности самих микросхем. Усредненные расчеты показывают, что микросхема, например с пятью логическими элементами нуждается в пяти внешних выводах на один элемент для обеспечения необходимых функциональных связей в устройстве. При увеличении количества логических элементов в микросхеме до 50 число внешних выводов уменьшается до двух на элемент. Известно, что в микроэлектронной аппаратуре кон-тактные соединения являются одной из основных причин ее отказов. Поэтому их уменьшение при использовании микросхем повышенной степени интеграции позволяет повысить надежность аппаратуры на один-два порядка по сравнению с аппаратурой на микросхемах малой степени интеграции.

Во-вторых, сокращается общая длина соединений между элементами, снижаются паразитные емкости нагрузок и, следовательно повышается быстродействие аппаратуры. При применении элементов со средней задержкой переключения 2 не реализовать их быстродействие можно только в том случае, если общая длина межсоединении не будет превышать 4 см, тогда задержка в межсоединениях будет примерно на порядок меньше, чем в элементе Отсюда следует, что создание устройств со сверхвысоким быстродействием принципиально возможно только на базе микросхем повышенного уровня интеграции, в которых длину соединений можно довести до 1 см, снизив тем самым задержку распространения сигнала между элементами до 0,05 — 0,1 не.

Вместе с отмеченными достоинствами микросхемы повышенного уровня интеграции имеют целый ряд особенностей, которые осложняют их разработку, изготовление и применение. Например возрастание удельной рассеиваемой мощности при увеличении степени интеграции требует принятия специальных мер по обеспечению теп-лоотвода, а при удельной мощности выше 20 Вт/см2 — применения принудительного охлаждения. Важной задачей при этом становится разработка функциональных структур, применение функциональных элементов и режимов, которые давали бы возможность снизить затраты энергии, приходящейся на одну выполняемую функцию

Повышение степени интеграции в большинстве случаев приводит к увеличению сложности функций, выполняемых микросхемой, С одной стороны, это положительный фактор, так как при использовании более сложных микросхем упрощается проектирование и изготовление аппаратуры. В то же время стоимость ремонта может существенно возрасти. Меньшая универсальность микросхемы повышенной степени интеграции ограничивает необходимый объем их выпуска, а следовательно, увеличивает их стоимость. (Последнее не относится к программно-управляемым микросхемам, для которых повышение степени интеграции не уменьшает универсальности.)

При повышении плотности упаковки усиливается электромагнитная связь между элементами за счет близкого расположения межсоединений и самих элементов, что приводит к понижению помехоустойчивости микросхем. Появляются значительные трудности при изготовлении малых по размерам корпусов с большим количеством выводов, что существенно сдерживает увеличение степени интеграции.

Тем не менее повышение уровня интеграции микросхем является прогрессивным направлением их развития, направлением, которое помогает существенно улучшить как функциональные, так и эксплуатационные показатели РЭЛ.

Существует два направления в разработке микросхем повышенного уровня интеграции. Одно из них базируется на гибридной технологии, использующей бескорпусные микросхемы малой степени интеграции и пленочную технологию их соединения на диэлектрической подложке. Бескорпусные микросхемы по сравнению с их аналогами в корпусах меньше по объему и массе примерно в 70 раз и по занимаемой площади в 30 раз. Устанавливают их на многослойную подложку, иногда называемую коммутационной платой. Соединения наносят либо по тонкопленочной, либо по толстопленочной технологии. Гибридная технология получила широкое распространение для изготовления микросхем повышенной степени интеграции благодаря сравнительно низкой стоимости проектирования и изготовления микросхем малой степени интеграции, хорошо отработанному технологическому процессу и высокому проценту выхода годных изделий.

Другое направление в разработке и производстве микросхем повышенной степени интеграции использует полупроводниковую технологию. Все элементы изготавливают в объеме полупроводниковой пластины и затем соединяют в требуемую схему с помощью тонких проводящих пленочных полосок, нанесенных на поверхность окисленной пластины. Межсоединения выполняют обычно по методу избирательного монтажа, при котором предварительно осуществляют на каждой пластине проверку годности элементов, после чего с помощью ЭВМ составляют схему межсоединений и затем только осуществляют межсоединения.

Полупроводниковые микросхемы повышенной степени интеграции изготавливают главным образом на основе МДП-транзисторов. Это объясняется их преимуществами перед микросхемами на биполярных транзисторах: втрое меньшим числом технологических операций и на порядок большей плотностью размещения элементов на подложке.

Однако по быстродействию они уступают микросхемам на биполярных транзисторах. Поэтому основную область их применения составляет аппаратура сравнительно невысокого быстродействия.

2013-12-29

2013-12-29 1037

1037