Лабораторная работа № 3

по курсу "Архитектура ЭВМ"

Моделирование работы регистров с помощью

Программы анализа электронных схем

Electronic Workbench

Цель работы: Ознакомление c возможностями моделирования работы схем регистров. Исследование схем регистров различного назначения, исследование преобразования параллельного и последовательного кода.

Продолжительность работы: 4 часа.

Основные понятия.

Регистр - это электронное устройство для запоминания (хранения) слова, а также для выполнения над словами некоторых логических операций.

Регистры выполняют следующие основные операции:

- установка регистра в нулевое состояние (сброс);

- приём слова из другого регистра;

- передача слова в другой регистр;

- сдвиг вправо и влево на требуемое число разрядов;

- преобразование последовательного кода в параллельный и

параллельного в последовательный.

Регистры, как правило, строятся на D-триггерах, т.к. эти триггеры позволяют производить запись информации однофазным кодом без предварительного "обнуления" по входу D (см.лаб.раб.2).

Приём информации в регистр и выдача может осуществляться параллельно и последовательно. В первом случае слово представляется в виде параллельного кода. При записи и при считывании все разряды кода слова передаются одновременно, каждый разряд по своей кодовой шине. При последовательной передаче кода слова, все разряды кода слова передаются последовательно во времени один за другим и строго в определенные дискретные моменты времени, совпадающие с управляющими сигналами.

Различают, сдвигающие регистры, в которых возможен сдвиг хранимого кода и регистры без сдвига с приемом информации параллельным кодом. Рассмотрим принцип работы регистров различного на значения.

Регистр с приёмом информации параллельным кодом. Эти регистры предназначены для приёма, хранения и выдачи информации кода одного m-разрядного слова, т.е. приём и выдача информации осуществляется в параллельном коде, рассматриваемый m-разрядный, регистр можно представить как совокупность одноразрядных регистров, имеющих общие шины управления. На рис. 3.1 представлен фрагмент схемы (3 разряда) регистра c приёмом информации параллельным однофазным кодом. Схема данного, регистра имеет выходную логику на элементах Э1-Э3, которая позволяет считывать информацию из регистра как в прямом, так и обратном коде в зависимости от значений разрешающего сигнала P2 и P3

Регистр (рис.3.1) выполнен на D-триггерах (T1-T3). Запись информации осуществляется по входам D в соответствии с уравнением D-триггера:

Qn+1=!CnQn V CnDn

Входное слово X=x1x2x3 поступает на входы D через конъюнкторы Э4-Э6 и при P1 =[TИ]=1 записывается в регистр.

Считывание выходного слова У=y1y2y3 производится через логические элементы Э1-Э3 - с прямых выходов Q1Q2 Q3 или с инверсных выходов!Q1,!Q2,!Q3. При P2=1, P3=0, Y=X т.е. считывание происходит в прямом коде, а при P2=0, P3=1 Y=!X, т.е. считывание происходит в обратном коде.

Сдвигающие регистры. В регистрах этого типа осуществляется сдвиг слова влево или вправо на заданное число разрядов. 3а один такт происходит сдвиг на один разряд. Применяются эти peгистры в основном для преобразования параллельного кода в последовательный и наоборот, а также в арифметических устройствах при выполнении операций над специальными кодами. Сдвигающие регистры выполняются на D-триггерах.

На рис. 3.2 представлена схема сдвигающего регистра, выполняющего операцию преобразования последовательного кода в параллельный. Число X=x1x2x3в последовательном коде поступает на вход D-триггера Т1 старшим разрядом вперёд. При поступлении I-го ТИ x3 записывается в T1. По второму ТИ x3 переписывается в T2, а в T1 записывается x2 и т.д.

Рис. 3.1

|

Рис. 3.2

|

Рис. 3.3

Таким образом, после трёх тактирующих импульсов всё число окажется записанным в регистр и может быть считано в параллельном коде с выходов Q1,Q2,Q3 (Y=X) или!Q1,!Q2,!Q3 (Y=!X). Процесс считывания организуется точно также как и в схеме рис. 3.1

На рис. 3.3 изображена схема сдвигающего регистра, выполняющего преобразования параллельного кода в последовательный. Входное слово X=x1x2x3 при P1=[ТИ]=1 и P2=0 записывается в T1T2T3 точно также как и в схеме рис. 3.1. Затем при P2=[ТИ]=1 и P1=0 происходит перезапись информации из T1 в T2, из T2 в T3 и т.д. Из младшего разряда в старший по каждому тактирующему импульсу. Таким образом, на входе последнего разряда Q3 будут последовательно появляться x3,x2,x1, т.е. входное слово X, представленное в параллельном коде будет преобразовано в выходное слово Y, представленное последовательным кодом.

В регистрах по схемах 3.1, 3.2, 3.3 количество триггеров в регистре зависят от разрядности преобразуемого машинного слова. Процесс записи, считывания и преобразования остаётся таким же, как было описано выше.

Используемые элементы программы EWB.

|

1) Voltage Source. С помощью этого источника на вход

триггеров и логических элементов подается логическая единица.

|

2) Переключатель (Basic->Switch). Переключение производится нажатием на клавишу, указанную в скобках над этим элементом.

3) Логический элемент "И" (Logic gates->2-Input AND gate).

4) Логический элемент "ИЛИ" (Logic gates->2-Input OR gate).

5) Триггер типа D (Digital->D Flip-Flop)

6) Светоиндикатор (Indicators->red Prob). При подаче на этот элемент логической единицы светодиод загорается красным цветом.

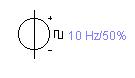

7) Источник прямоугольных сигналов (Sources->Clock).

Выполняет функцию синхронизатора, который обеспечивает

одновременность подачи сигналов на входы триггеров.

3. Задание на лабораторную работу

1. Для несинхронизируемого RS-триггера с инверсным управлением нарисовать условное обозначение. Получить структуру несинхронизируемого RS-триггера с инверсным управлением. Нарисовать таблицу истинности, а также диаграмму состояний несинхронизируемого RS-триггера с инверсным управлением. Пояснить процессы, происходящие в триггере при подаче на его входы запрещенной комбинации.

2. Путем анализа переходных процессов при переключении триггера определить значения динамических параметров:

одноступенчатый синхронизируемый RS-триггер – варианты 1, 5, 9, 13, 17, 21;

двухступенчатый несинхронизируемый T-триггер – варианты 2,6,10,14,18,22,25

двухступенчатый синхронизируемый T-триггер – варианты 3, 7, 11,15,19,23;

двухступенчатый D-триггер – варианты 4, 8, 12,16,20,24.

3. Пояснить принцип работы двухступенчатого D-триггера. Изобразить схему использования двухступенчатого D-триггера в качестве несинхронизируемого T-триггера.

Нарисовать диаграмму состояний двухступенчатого D-триггера.

4. Изобразить схему построения синхронизируемого T-триггера на основе двухступенчатого DV-триггера.

5. С помощью временных диаграмм пояснить различия в поведении одноступенчатых триггеров с динамическим управлением и двухступенчатого триггера для:

T-триггера – варианты 1, 3, 5, 7, 9, 11, 13,15,17,19,21,23,25;

D-триггера – варианты 2, 4, 6, 8, 10, 12, 14,16,18,20,22,24.

6. Нарисовать схему 4-разрядного параллельного регистра.

7.Нарисовать схему 4-разрядного последовательного регистра. Пояснить принцип работы регистра временными диаграммами записи числа A (А равно номеру варианта

плюс 1) в регистр.

регистр со сдвигом влево – варианты 1, 3, 5, 7, 9, 11, 13,15,17,19,21,23,25;

регистр со сдвигом вправо – варианты 2, 4, 6, 8, 10, 12, 14. 2, 4, 6, 8, 10, 12, 14,16,18,20,22,24.

Задание 3

Нарисовать схему 4-разрядного счетчика. Пояснить временными диаграммами

принцип работы счетчика.

суммирующий счетчик с параллельным переносом – варианты 1, 5, 9, 13; 17,21

вычитающий счетчик с параллельным переносом – варианты 2, 6, 10, 14; 18,22,25

суммирующий счетчик с последовательным переносом – варианты 3, 7, 11; 15,19,23

вычитающий счетчик с последовательным переносом – варианты 4, 8, 12; 16,20,24

Содержание отчета.

1. Схемы, моделирующие работу регистров по всем пунктам задания.

2. Временные диаграммы, поясняющие работу регистров.

3. Проанализировать работу регистров с помощью

программы EWB "логический анализатор".

5. Контрольные вопросы.

1. Назначение различных типов регистров в вычислительных устройствах.

2. Какие типы триггеров могут быть использованы для построения

регистров?

3. Назначение синхросигнала в работе регистров.

4. Какие дополнительные устройства необходимы для построения

универсального регистра.

5. Последовательность действий, выполняемых на регистрах с целью преобразования параллельного кода в последовательный код и обратно.

2018-02-20

2018-02-20 2012

2012