Задание, Постановка задачи 3

Описание JK-триггера 4,5

Алгоритм 6

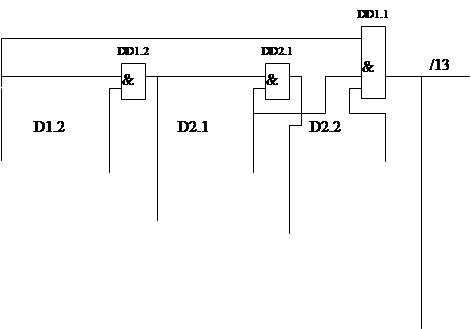

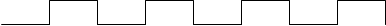

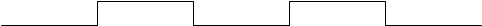

Функциональная схема, временная диаграмма 7

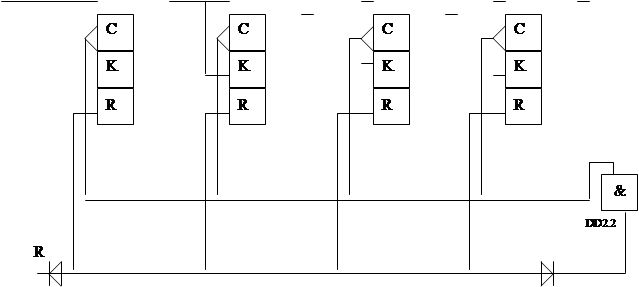

Принципиальная схема 8

Список литературы 9

Задание

Деление частоты на 13 с помощью JK-триггеров.

Постановка задачи

Для деления частоты на 13 необходимо пропускать только каждый тринадцатый импульс. Это может быть реализовано посредством применения счетчика, который дает выходной импульс при записи в него значения 13.

ОПИСАНИЕ JK-ТРИГГЕРА

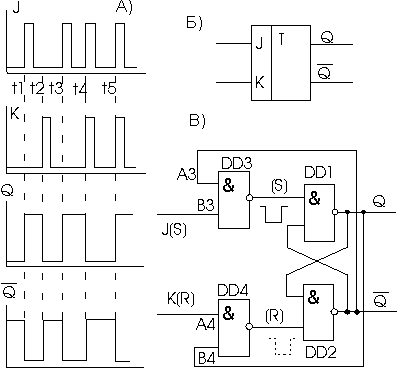

Триггер типа JK представляет собой устройство с двумя устойчивыми выходными состояниями, обладающее двумя информационными входами J и K (рис. 7.1). По принципу действия он сходен с RS-триггером, с той разницей, что в состояниях JK-триггера нет неопределенности при одновременном поступлении сигналов высокого уровня на оба входа. На рис. 7.1В показана схема JK-триггера на ЛЭ И-НЕ. Она отличается от схемы RS-триггера только тем, что элементы DD3 и DD4 включены не как инверторы, а по входам A3 и A4 управляются сигналами с выходов триггера /Q и Q, соответственно.

Работу схемы поясняет рис. 7.1А. Если JK-триггер находится в нулевом состоянии (Q = 0, a /Q = 1 -до момента t1) и на вход J поступит сигнал показанного на рисунке вида, на выходе DD3 за счет связи выхода /Q с входом A3, возникнет сигнал низкого уровня. Он будет действовать подобно сигналу /S на входе /R/S-триггера, образованного элементами DD1 и DD2, т. е. вызовет смену состояния триггера. Если JK-триггер пребывал в единичном состоянии (Q = 1 и /Q = 0 - до момента t2) и сигнал поступит на вход K, то, рассуждая аналогично, можно убедиться, что на выходе DD4 возникает сигнал (показан на рисунке штрихами), который действует подобно сигналу /R, т. е. состояние триггера снова изменится (в этом случае на выходе DD3 напряжение высокого уровня). Когда на обоих входах J и К одновременно напряжение низкого уровня, состояние триггера сохраняется.

Рис. 7.1. JK-триггер: А - временная диаграмма работы, Б - условное графическое обозначение, В - схема с четырьмя ЛЭ И-НЕ

Когда на входы J и К одновременно поступает напряжение высокого уровня, дальнейшее поведение триггера зависит от его исходного состояния.

1. Исходное состояние JK-триггера - единичное (Q = 1 и /Q = 0 - после момента t3). За счет связи /Q с A3 на входе A3 = 0 и на выходе DD3 сохраняется напряжение высокого уровня, на которое сигнал J= 1 на входе Вз не влияет. В то же самое время на выходе элемента И-НЕ (DD4) вследствие связи входа В4 с выходом Q (Q = 1) появится сигнал /R, от которого /R/S-триггер, состоящий из DD1 и DD2, сменит состояние (Q = 0, a /Q = l - после момента t4).

2. Исходное состояние триггера - нулевое (Q = 0 и /Q = 1 - после момента t4). Рассуждая аналогично, нетрудно убедиться, что на выходе DD4 сохранится напряжение высокого уровня, а на выходе DD3 появится сигнал /S, который сменит состояние /R/S-триггера (Q = 1, /Q = 0 - после момента t5).

Таким образом, в обоих случаях JK-триггер меняет свое состояние. В этом и состоит различие между JK- и RS-триггерами.

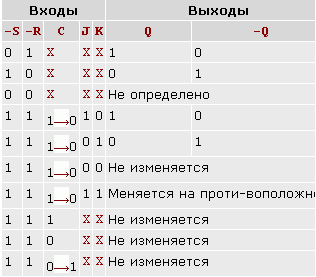

Работа JK-триггера определяется следующей таблицей состояний:

| J | K | Qn+1 | /Qn+1 |

| 0 | 0 | Qn | /Qn |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | /Qn | Qn |

|

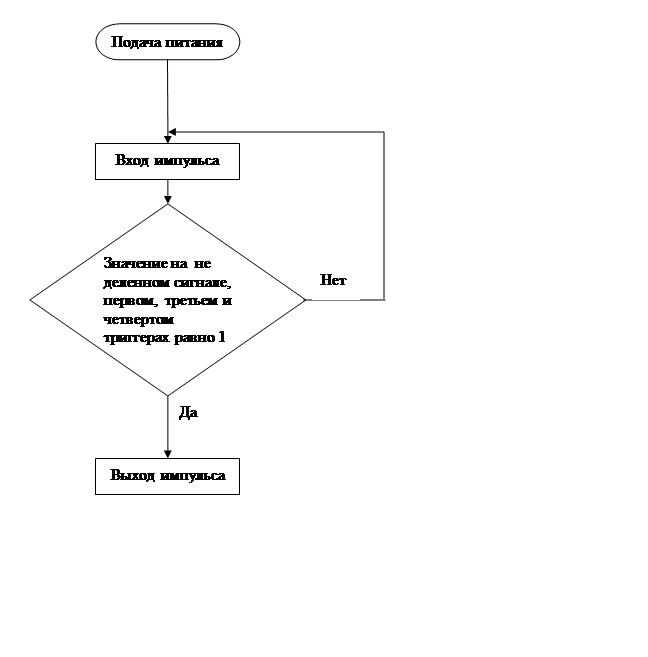

Алгоритм

Описание алгоритма

Описание алгоритма

1. Подача питания.

2. Вход импульса.

3. (Условный блок) Проверка уровня напряжения на не деленном сигнале, первом, третьем и четвертым триггерах на соответствие уровню логической единицы. В случае положительного результата сравнения происходит выход импульса, в случае отрицательного – вход нового.

4. Выход импульса.

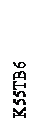

Функциональная схема, временная диаграмма

| |||

| |||

|

|

|

|

1

1

| ||||||||||

| ||||||||||

|  |  | ||||||||

C

C

D1.2

|  | ||||

| |||||

D2.1

| ||||

| ||||

| ||||

D2.2

D2.2

|

/13

/13

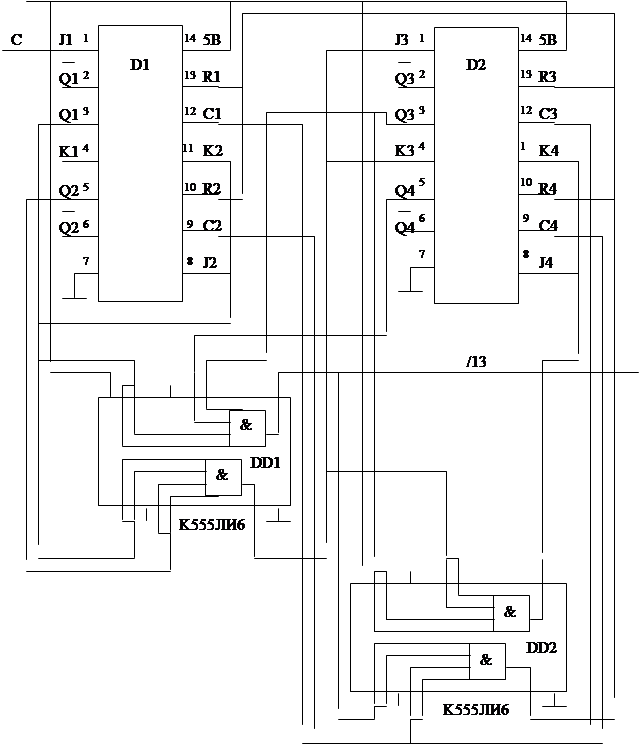

Принципиальная схема

+5B

Использовались микросхемы К555ТВ6 (2 JK-триггера без входа S) и микросхемы К555ЛИ6 (логическое И). Частота подается на C, деленная частота выходит на /13.

Список литературы

· Лекции. Зак Е.А.

· “Популярные цифровые микросхемы” Шило В.Л.

· “Применение интегральных микросхем серии ТТЛ” Бирюков С.А.

2020-01-15

2020-01-15 250

250