Часть I. Принципы построения.

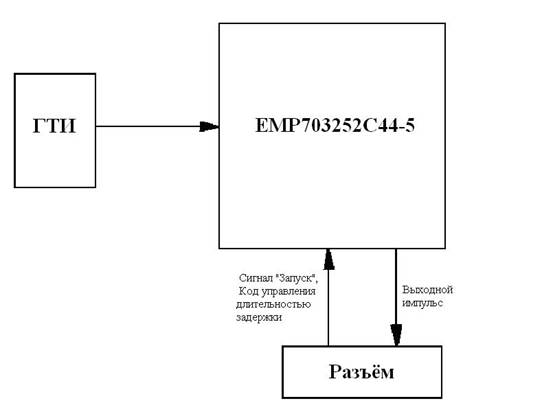

Для формирования задержек необходимой длительности, требуется отсчитывать нужное количество эталонных импульсов и сравнивать его с числом, задающимся входным кодом. Если числа совпадают, то на выходе устройства появляется калиброванный импульс.

Число вариантов длительности задержки выхода импульса можно рассчитать, учитывая максимальный формируемый интервал времени и длительность выходного импульса:

Х= (Тmax – Тmin) / Тmin = (5*10-4 с - 10-7 с) / (10-7 с) = 999

При этом длительность задержки выхода импульса будет рассчитываться по формуле (10-7 с)*Х, где Х – число от 0 до 999, записанное двоичным кодом. Чтобы подавать такое число, нам понадобится 10 входов, через которые будет поступать двоичный код, и десятиразрядный регистр, в котором это число будет храниться.

Для подсчёта эталонных импульсов используется десятиразрядный счётчик, для сравнения с заданным кодом используется устройство сравнения (компаратор) той же разрядности.

Необходимая длительность выходного импульса получается с помощью формирователя выходных импульсов.

Рис. 1 Структурная схема селектора импульсов.

Часть II. Разработка схемы устройства.

Функциональная схема проектируемого устройства.

В данной главе будет рассмотрен вопрос о функциональном устройстве проектируемого прибора и приведена внутренняя структура программируемой логической интегральной схемы, которая является основой рассматриваемого здесь цифрового таймера, а так же будут приведены результаты машинного моделирования. В качестве среды проектирования ПЛИС Altera мы берём MAX+PLUS II. Назначение семейства ПЛИС для реализации проекта предоставили компилятору для того, чтобы оценить требуемые ресурсы. На рис.3 приведена функциональная схема селектора импульсов.

Рис. 2. Функциональная схема таймера

Вся схема тактируется от кварцевого импульсного генератора частотой 10 МГц.

Внутренняя структура селектора импульсов.

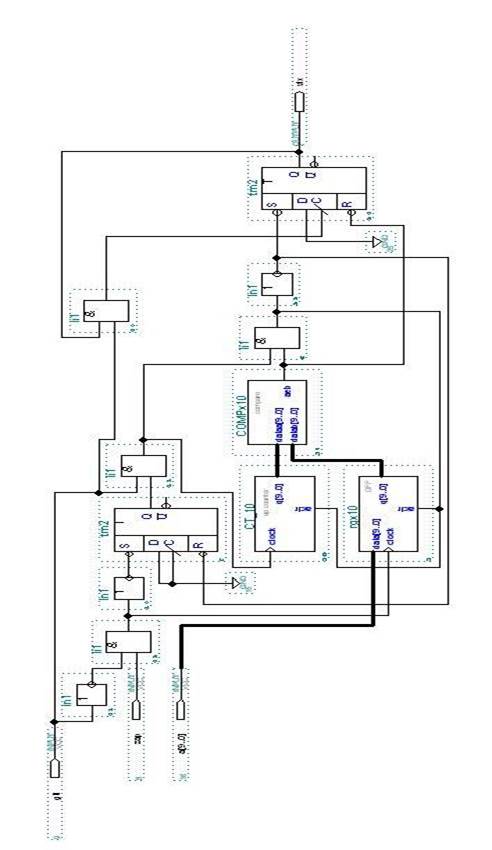

На рис. 3 приведена внутренняя структура цифрового таймера. В начале разработки схемы мы выбрали, как среду разработки MAX+PLUS II. Запустив пакет САПР Altera Max + PLUS II, в графическом редакторе Graphic Editor, мы создали новый файл(file, new…), выбрали из базы данных нужные нам элементы. С помощью редактора MegaWizard Plug-In Manager, встроенного в Max+ PLUS II, были сделаны десятиразрядные регистр, счётчик и компаратор.

После того, как схема была полностью спроектирована, мы проверили её на наличие ошибок с помощью компилятора системы (Compiler).

Работа схемы:

Наша схема тактируется ГТИ, который на схеме изображен как вход «gti». На входы a[9..0] подается десятиразрядный двоичный код, управляющий временем задержки выходного импульса. Под действием импульса запуска, поступающего на вход «zap», управляющий код запишется в регистр. Этим же импульсом переведётся в единичное состояние первый триггер. Снятие импульса запуска блокирует запись в регистр до следующего сигнала записи, предотвращая случайную запись управляющего кода во время работы схемы, для избежания возникновения ошибок.

Каскад из двух инверторов и элемента «2И», стоящий перед триггером, необходим в схеме для предотвращения ошибки, возникающей, если фронт импульса запуска совпадёт с фронтом синхроимпульса, в результате которой на выходе схемы установилась бы логическая единица вне зависимости от кода управления.

Логическая единица, установившаяся на выходе первого триггера, откроет ключ, представленный элементом «2И», и даст возможность синхроимпульсам с входа «gti» поступать на счётчик. Число вошедших в счётчик импульсов будет постоянно сравниваться с числом, записанным в регистре, и при их совпадении компаратор выдаст импульс, которым на выходе второго триггера установится логическая единица. В то же время обнулятся регистр и счётчик, и сбросится первый триггер, в свою очередь закрывающий ключ «2И», прекращая трансляцию синхроимпульсов на вход таймера.

Чтобы задать необходимую длительность выходного импульса, схема устроена так, чтобы второй триггер изменил своё состояние (1 > 0) с помощью входа «/С» только с приходом синхроимпульса. Таким образом, логическая единица на выходе будет держаться один период синхроимпульса. Учитывая, что частота СИ =10МГц, т.е. его период =10-7с, длина выходного импульса будет соответствующей.

Рис. 3 Внутренняя структура цифрового таймера.

2020-01-14

2020-01-14 227

227