Подготовка алгоритмов управления к реализации на управляющем вычислителе

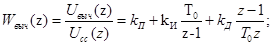

Данные на вычислитель поступают с двух источников. Первый,  , это задающее воздействие. Второй,

, это задающее воздействие. Второй,  , это анодное напряжение. В данной системе контроллер будет реализовывать ПИД- закон управления.

, это анодное напряжение. В данной системе контроллер будет реализовывать ПИД- закон управления.

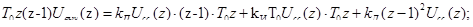

(3.1)

(3.1)

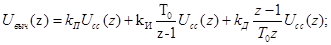

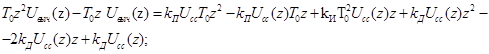

(3.2)

(3.2)

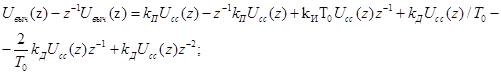

(3.3)

(3.3)

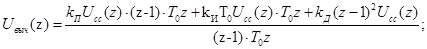

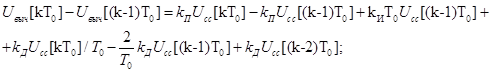

(3.4)

(3.4)

(3.5)

(3.5)

(3.6)

(3.6)

(3.7)

(3.7)

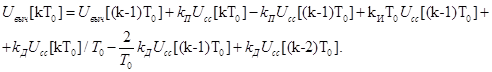

(3.8)

(3.8)

Все величины представляют собой напряжение в диапазоне от 0...+5В. Коды данных величин поступают на микроконтроллер. Затем в ЦАП, потом на усилитель мощности. Мы получили алгоритм управления вычислителем с точки зрения управленца, теперь надо осуществить его программно. Мы можем посчитать сколько ячеек памяти нам нужно, т.е. объем. Переменные составляющие, такие как  ,

,  , записываем в оперативную память, а коэффициенты(

, записываем в оперативную память, а коэффициенты( ,

,  ,

,  ,

,  ,

,  ) в постоянную память.

) в постоянную память.

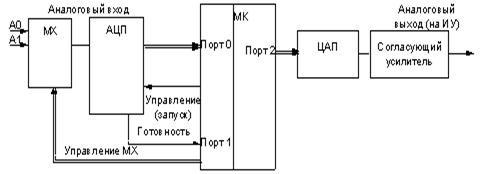

Функциональная схема вычислителя

Вычислитель предназначен для преобразования и обработки информации, задающего и анодного напряжения в обратной связи. На входе вычислителя аналоговый сигнал в диапазоне 0 … + 5V, и на выходе получен аналоговый сигнал в диапазоне 0 … + 10V. Функциональная схема вычислителя представлена на рис. 3.1. 4 – ех разрядный аналоговый переключатель с декодером, который переключает выход с 1 из 2 аналоговых входов применяется для реализации управляющего преобразования аналоговой информации в АЦП. Номер данного входа определяется двоичным числом поданным на управляющий вход. Информация относительно действий в двоичном коде непосредственно идет от микроконтроллера. Десяти разрядный ЦАП преобразует 8 –разрядный дискретный код в аналоговый, с этой целью на двух младших битах ЦАП мы представляем землю. Это подразумевает, что в вычислитель должены входить: микроконтроллер, ЦАП, АЦП, мультиплексор и согласующий усилитель.

Рисунок 3.1 - Функциональная схема вычислителя

2020-01-14

2020-01-14 139

139