Традиционная структура МОП-транзистора обеспечила снижение длины затвора от 10 мкм в 70-х годах до 0,06 мкм в настоящее время путём простого масштабирования, то есть уменьшением длины затвора, толщины диэлектрика и глубины залегания p-n-переходов. Однако переход проектных норм через границу 130 нм в рамках традиционной конструкции наталкивается на физические ограничения. Таким образом, транзисторы для технологий XXI века должны иметь иную структуру и использовать новые материалы для подзатворного диэлектрика.

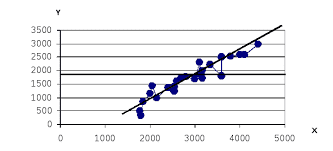

С уменьшением геометрических размеров транзисторов снижается площадь кристалла, уменьшаются паразитные ёмкости, улучшается быстродействие и снижается энергопотребление СБИС. За последние 30 лет длина затвора МОП-транзистора уменьшилась в 200 раз (с 10 мкм в начале 70-х годов до 60 нм в наши дни) [1]. В настоящее время коммерчески доступной является технология с минимальными горизонтальными размерами элементов 0,13 мкм, позволившая реализовать массовое производство микропроцессоров Intel Pentium 4 с тактовой частотой более 2,5 ГГц на МОП-транзисторах с длиной канала 60 нм и толщиной подзатворного окисла 1,5 нм [1]. В соответствии с прогнозами Ассоциации предприятий полупроводниковой индустрии NTRS, минимальные размеры элементов будут продолжать быстро уменьшаться и к 2012 году достигнут 50 нм.

Каждый технологический шаг в направлении уменьшения размеров сопряжён с ростом проблем конструирования и производства, которые приходится решать для обеспечения теоретически прогнозируемых характеристик транзистора. Любое улучшение одних параметров приводит к ухудшению других, причём с уменьшением размеров взаимное влияние параметров становится всё более сильным.

С ростом степени интеграции СБИС и систем на кристалле увеличивается доля чипов, содержащих аналоговые блоки, которые обеспечивают взаимодействие с окружающим миром, необходимое для крупных и функционально законченных систем. К транзисторам для аналоговых и цифровых применений предъявляются противоречивые требования. Для цифровых СБИС пороговое напряжение нельзя снижать неограниченно, поскольку при этом увеличивается подпороговый ток, который определяет потребление энергии СБИС в неактивном состоянии. Верхний предел порогового напряжения ограничивается четвертью от напряжения питания [2], которое стараются снизить для уменьшения потребляемой мощности. Однако для аналоговых схем идеальным является нулевое пороговое напряжение Vt = 0, что увеличивает динамический диапазон аналоговой схемы, определяемый разностью между напряжением на затворе и Vt, то есть (Vgs – Vt).

Особыми требованиями к "аналоговым" транзисторам являются также повышенная нагрузочная способность (ток стока в режиме насыщения), линейность и малые нелинейные искажения на малом сигнале. Для дифференциальных каскадов и токового зеркала важна согласованность характеристик транзисторов.

Основными проблемами микроминиатюризации МОП-транзисторов являются туннелирование через затвор, инжекция горячих носителей в окисел, прокол между истоком и стоком, утечки в подпороговой области, уменьшение подвижности носителей в канале, увеличение последовательного сопротивления между истоком и стоком, обеспечение запаса между пороговым напряжением и напряжением питания. Транзистор должен иметь слабую зависимость порогового напряжения от напряжения на стоке, от длины и ширины канала, а также большую передаточную проводимость, большое выходное сопротивление, малое сопротивления областей истока и стока и большую нагрузочную способность. Емкости затвора и p-n-переходов должны быть минимальны. Разброс параметров техпроцесса, который растёт с уменьшением размеров транзистора, не должен снижать процент выхода годных кристаллов.

2020-04-20

2020-04-20 135

135