Цель работы.

Исследовать способы передачи информации в последовательном коде посредством микропроцессора К1816ВЕ48, составить и отладить программу, реализующую передачу информации в последовательном коде удаленному получателю в асинхронном режиме, при отладке программы изучить использование контрольных точек.

Введение.

Последовательная связь – это передача или прием, при котором данные передаются последовательно бит за битом, в противоположность параллельной передаче, при которой данные передаются побайтно или пословно.

Передать данные от микропроцессора к какому-либо другому устройству системы можно параллельно или последовательно. При параллельной передаче микропроцессор передает к внешнему устройству одновременно 8 бит данных по 8 линиям. При последовательной (не одновременной) передаче данных для передачи 8 бит данных используется одна линия.

Скорость передачи данных. Для передачи данных по одной линии необходимо определить частоту или скорость передачи данных. Скорость передачи v определяется как число битов данных, передаваемых по линии в 1 секунду.

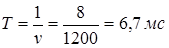

Обычно скорость передачи данных составляет 110 и 300 бит/с (бод) при передаче данных к телетайпу и 1200, 2400, 4800 и 9600 бод при передаче между контроллерами и ЭВМ и наоборот. Предположим, что скорость передачи данных 1200 бод. Длительность импульса, соответствующая передаче 1 бит данных, определяется по формуле:

.

.

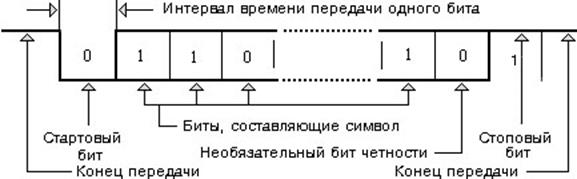

На рисунке 1 показано, что две логические «1», передаваемые последовательно, воспринимаются как логическая «1» длительностью, равной утроенной длительности передачи 1 бит данных.

Рисунок 1 – Формат последовательных данных

Длительность передачи 1 байта данных со скоростью 1200 бод составит

При параллельной передаче данных эта же информация передается за несколько микросекунд.

Параллельно-последовательное преобразование данных. Для последовательной передачи данных вырабатываемое микропроцессором 8-разрядное слово нужно преобразовать в последовательность из 8 бит, передаваемых, например, со скоростью 9600 бод. Для этого нужно: выработать 8-разрядное слово; записать его в сдвиговый регистр (параллельно 8 бит); сдвигая 8-разрядное слово с выбранной частотой, выдавать с выхода регистра последовательно по одному биту.

Вырабатываемое микропроцессором 8-разрядное слово вводится в сдвиговый регистр, а затем последовательно сдвигается. Биты данных выдаются по одному с тактовой частотой, начиная с D0 и кончая D7. Скорость передачи данных зависит от тактовой частоты сдвигового регистра. Используя микропроцессор, операцию преобразования параллельного кода в последовательный можно организовать, используя его средства.

Биты «старт», «стоп» и «паритет». Рассмотрим, как осуществляется прием и распознавание переданных данных. Предположим, что передается следующая кодовая комбинация:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

Первым к какому-либо приемнику передается бит D0. Приемные устройства должны определить начало передачи данных. Предположим, например, что прием первой логической «1» или «0» воспринимается приемным устройством как момент начала передачи данных. Однако при этом не учитываются некоторые условия.

Во-первых, нужно предположить, что линия последовательной передачи данных находится в состоянии логической «1» или «0» тогда, когда на шине данных нет информации. Предположим, что, когда нет передачи данных, эта линия находится в состоянии логической «1». Чтобы определить момент начала передачи, приемное устройство должно зафиксировать изменение состояния этой линии с логической «1» в логический «0» и наоборот.

Однако если первый передаваемый бит D0 равен логической «1», то момент начала передачи будет пропущен, поскольку состояние линии передачи данных, не изменится после передачи бита D0. В худшем случае передаваемая кодовая комбинация может состоять из одних единиц. Тогда ни один бит данных не будет принят приемным устройством.

Решить эту проблему можно, добавив к передаваемому цифровому слову дополнительные стартовые биты. Стартовые биты, вырабатываемые передающим устройством, информируют принимающее устройство о начале передачи новой кодовой последовательности.

Когда нет передачи данных, последовательная линия связи должна находиться в одном из двух логических состояний. Предположим, что это состояние логической «1». Состояние стартового бита должно быть противоположно состоянию линии в режиме ожидания передачи. Приемное устройство воспринимает стартовый бит и начинает прием данных.

Кроме стартового бита, к передаваемой кодовой комбинации добавляется еще один разряд – бит паритета. Этот бит вырабатывается передающим устройством и используется приемником для контроля правильности приема кодовой комбинации. Передаваемое 8-разрядное цифровое слово может иметь четное или нечетное число логических «1». Например, в слове 1Ah три логических «1», а в слове 3Fh шесть логических «1». Приемное устройство не только принимает данные, но и настроено на прием нечетного или четного числа логических «1».

Предположим, что приемник настроен на прием четного числа логических 1. Передающее устройство всегда должно передавать цифровые слова с четным числом логических «1». Не все 8-разрядные слова содержат четное число «1», поэтому при передаче цифрового слова передающее устройство должно вырабатывать дополнительный бит – бит паритета. Использование бита паритета для контроля правильности приема данных при последовательной передаче позволяет обнаруживать одиночные ошибки, т. е. такие ошибки, когда одна из переданных логических «1» была неверно принята как логический «0» или наоборот.

Бит паритета имеет такое логическое состояние, что передаваемое 8-разрядное слово всегда содержит четное число логических «1». Если передаваемое слово содержит нечетное число единиц, то бит паритета будет установлен в логическую «1», а если четное – в логический «0». Бит паритета дополняет число передаваемых «1» до четного или нечетного, в зависимости от типа контроля, реализованного в приемном устройстве.

Последний бит передаваемой кодовой комбинации называется стоповым битом. Стоповый бит используется для обозначения окончания передачи кодовой комбинации и вырабатывается передающим устройством. Приемное устройство ожидает прихода стопового бита в конце каждого передаваемого цифрового слова. Если этот бит не пришел, приемное устройство может выдать сигнал ошибки передачи данных. Стоповый бит, так же, как и бит паритета, служит для обнаружения ошибок передачи данных.

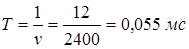

При различных типах последовательной передачи данных используется различное число стоповых битов: 1; 1,5 или 2. Полное цифровое слово, содержащее один стоповый бит, показано на рисунке 1. Общее число передаваемых битов данных равно 12. Длительность передачи этого слова со скоростью 2400 бод:

.

.

Поскольку передача битов в последовательном коде должна осуществляется с определенной длительностью, необходимо реализовать подпрограмму задержки времени. Для реализации временной задержки между двумя фрагментами программы можно использовать таймер микропроцессора, работающий в режиме таймера (временные интервалы пропорциональны длительности машинного цикла) или в режиме счетчика (временные интервалы пропорциональны периоду сигналов от внешнего генератора, подаваемым на входы T0 или T1).

Например, для того, чтобы организовать временную задержку длительностью T с использованием таймера, необходимо настроить его на работу в режиме таймера, загрузить байт константы пересчета (К) в таймер, запустить таймер, а затем перейти в режим ожидания (или холостого хода) до появления флажка переполнения таймера TF. Программа обработки прерывания от таймера должна прекращать работу таймера. Эта процедура реализуется следующей последовательностью команд:

ORG 100H ; Адрес программы задержки времени

DELAY: MOV A, # 156; Предустановка

MOV T, A ; таймера

STRT T ; Запуск таймера

WAIT: JTF ENDT ; Ожидание переполнения таймера

JMP WAIT ; таймера

ENDT: STOP TCNT ; Останов таймера

RETR ; Выход из программы

ORG 30H ; начальный адрес программы

ANL P1, #FEH; Установка P1.0 в 0

CALL DELAY; Вызов подпрограммы задержки

ORL P1, 01H ; Установка P1.0 в 1

Временная задержка определяется временем работы таймера до переполнения (256 – К) отсчетов, а также временем выполнения команд подготовки таймера к работе. Таймер увеличивает своё значение на 1 за 80 мкс. При достижении 255 увеличение значения таймера на 1 вызывает его переполнение и установку флага TF. Если мы записали в таймер число 156, то до его переполнения произойдет 100 отсчетов таймера. Тогда время передачи одного бита составит

T = 100 · 80 = 8000 мкс.

Из этого выражения можно определить значение скорости передачи:

125 (бод).

125 (бод).

Поскольку при разработке программы в данной работе будет присутствовать большое количество циклов, и поскольку эмулятор не позволяет исследовать состояние портов ввода-вывода в реальном времени, то необходимо воспользоваться точками прерываний. Процедура пошагового выполнения программы оказывается слишком медленной и бесполезной в случае, когда программа должна выполниться в рабочем режиме. Поэтому желательно иметь возможность безостановочного выполнения программы до тех пор, пока не встретится какая-то определенная команда. При выполнении команды останова программы в заданной точке управление будет передано управляющей программе отладчика, и пользователь сможет проанализировать состояние процессора, что позволит оценить правильность выполнения программы.

Средства обеспечения контрольных остановов в заданных точках программ очень полезны для организации их отладки, поскольку до момента останова участки программы любого размера могут прогоняться с максимальной скоростью. Например, некоторая подпрограмма может быть выполнена целиком, а затем в точке останова можно проанализировать состояние регистров процессора с целью установления правильности выполнения подпрограммы.

И в заключении, немного о согласовании уровня сигналов. Микропроцессор имеет ТТЛ уровни своих выходных сигналов. При необходимости, когда внешнее устройство – приемник сигналов требует более высоких уровней логических сигналов (например, уровней КМОП), то можно использовать стандартные схемы в зависимости от номинала питания КМОП-схем.

Чаще всего дополнительные схемы согласования уровней при построении систем сбора и обработки информации на основе микропроцессоров требуются как раз при обмене данными по последовательному каналу. Такой обмен требует соблюдения требований интерфейса RS-323. Последовательный порт микропроцессора имеет уровни ТТЛ: «1» – высокий уровень, «0» – низкий уровень. RS-232 требует для передачи «1» уровня – 12В, для передачи «0» – уровня +12В (см. рис. 2).

Рисунок 2 – ТТЛ и RS-323 сигналы.

Согласование сигналов может быть выполнено в соответствии со схемой на основе элементов из серии К170 (рисунок 3). В качестве передатчиков и приемников могут использоваться и другие схемы (например, передатчик – SN75150, приемник – SN75154, или схема MAX232A, содержащая и передатчик, и приемник).

Рисунок 3 – Согласование сигналов на основе элемента MAX232A

Если передача осуществляется на большое расстояние, то она должна выполняться в соответствии со стандартом «токовая петля». Для формирования токовых посылок может использоваться схема на основе транзистора и оптрона (рисунок 4).

Рисунок 4 – Согласование сигналов по стандарту «токовая петля»

Задание.

1. Разработать подпрограмму вычисление арифметического выражения:

DW = i + j · 8,

где i, j – последние цифры номера зачетной книжки.

2. Разработать подпрограмму, реализующую передачу результата удаленному получателю по двухпроводной линии передачи. Передачу информации осуществляется в последовательном коде, при асинхронном режиме обмена. Предполагается, что линия передачи информации подключена к четвертому разряду порта Р2, а оставшиеся разряды могут быть использованы для подключения датчиков и внешних исполнительных устройств.

3. Измерить действительную скорость передачи информации, определить относительную погрешность действительной скорости относительно теоретической.

Примечание к выполнению задания.

Скорость передачи информации по линии связи выбрать из таблицы в соответствии с последней цифрой номера зачетной книжки.

| Последняя цифра номера зачетки | |||||||||

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 0 |

| Скорость передачи, Бод | |||||||||

| 600 | 3200 | 300 | 2 400 | 800 | 1 200 | 400 | 1600 | 150 | 750 |

Содержание отчета.

1. Задание.

2. Текст программы на языке Ассемблер.

3. Временная диаграмма сигнала, поступающего в линию связи.

4. Расчет относительной погрешности скорости передачи.

5. Выводы по работе.

Контрольные вопросы.

1. Расскажите о формате кадра последовательного кода.

2. Каким образом можно реализовать умножение числа на 2 в микропроцессоре К1816ВЕ48?

3. Какова длительность периода увеличения содержимого таймера на единицу?

4. Каким образом можно осуществить преобразование параллельного кода в последовательный?

5. Какой способ останова программы в контрольных точках применяется в используемом эмуляторе?

6. Расскажите о порядке работы с точками прерываний.

7. За счет чего возникает погрешность скорости передачи?

2020-06-12

2020-06-12 94

94