По 04_04 Практические занятия Архитектура ВМиС, ИКБО-01-18; ИКБО-02-18; ИКБО-03-18; ИКБО-13-18; ИКБО-12-18; ИКБО-16-18; ИНБО-05-18; ИНБО-06-18; ИНБО-02-18; ИНБО-03-18; ИНБО-01-18; ИНБО-04-18

Контрольная работа №1

Управляющее слово ЦП

Цель контрольной работы

Целью работы является проверка усвоения материалов по архитектуре операционного устройства центрального процессора ВМ и взаимодействия входящих в нее элементов.

Управляющее слово ЦП составляется из разрядов управления устройств, входящих в ОУ ЦП.

Для выполнения контрольной работы необходимо уяснить порядок функционирования составляющих операционное устройство элементов вычислительной техники: мультиплексоров, дешифратора, арифметико-логического устройства (АЛУ), регистров и оперативного запоминающего устройства.

Мультиплексор

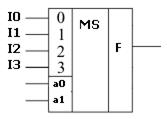

Из многих информационных входов I0…I3 мультиплексор подает на выход один, соответствующий коду, установленному на управляющих входах a1, a0. Структурная схема мультиплексора имеет вид:

Рис. 1. Схема мультиплексора.

Таблица соответствия

| a1 | a0 | F |

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

Дешифратор

Это устройство, которое имеет единицу только на одном из выходов, соответствующему коду входных информационных сигналов.

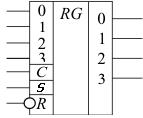

Дешифратор на схемах обозначается следующим образом:

Рис. 2. Схема дешифратора.

Таблица соответствия для двухвходового дешифратора имеет вид:

| Е | Х2 | Х1 | L0 | L1 | L2 | L3 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | X | X | 0 | 0 | 0 | 0 |

Вход Е означает разрешение работы дешифратора. Этот вход обычно делают инверсным. Если разрешение есть, то  =0, и один из выходов в соответствии с кодом входных информационных сигналов дешифратора равен 1. Если E=1, то независимо от состояния входных сигналов все выходы дешифратора равны 0.

=0, и один из выходов в соответствии с кодом входных информационных сигналов дешифратора равен 1. Если E=1, то независимо от состояния входных сигналов все выходы дешифратора равны 0.

Регистр

Регистры обычно строятся на D триггерах. Обозначение регистра на схемах может иметь вид:

Рис. 3. Схема регистра.

На вход С подается синхросигнал. Регистр может срабатывать по переднему или по заднему фронту синхроимпульса. Вход S – управляющий. При S=0 регистр осуществляет хранение информации. При S=1 регистр переписывает свое состояние по синхросигналу в соответствии с состоянием входных информационных сигналов.

Арифметико-логическое устройство

АЛУ выполнено на основе комбинационных схем, выходные состояния которых полностью определяются входными информационными и управляющими сигналами.

Таблица микроопераций АЛУ

| M | S1 | S0 | C | Микрооперации | Наименование |

| 0 | 0 | 0 | 0 | A | Передача А |

| 0 | 0 | 0 | 1 | A+1 | Инкремент А |

| 0 | 0 | 1 | 0 | A+B | Сумма |

| 0 | 0 | 1 | 1 | A+B+1 | Сумма с инкрементом |

| 0 | 1 | 0 | 0 | A-B-1 | Разность с декрементом |

| 0 | 1 | 0 | 1 | A-B | Разность |

| 0 | 1 | 1 | 0 | A-1 | Декремент А |

| 0 | 1 | 1 | 1 | A | Передача А |

| 1 | 0 | 0 | Х | A۷B | ИЛИ |

| 1 | 0 | 1 | Х | A  B B | Искл. ИЛИ |

| 1 | 1 | 0 | Х | A۸B | И |

| 1 | 1 | 1 | Х |  | Не А |

Операционное устройство

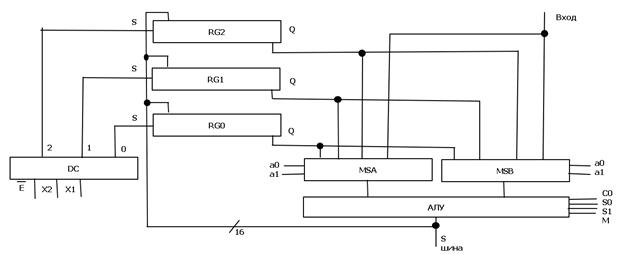

Операционное устройство (ОУ) осуществляет операции (арифметические и логические) над входными информационными сигналами. Характер операций, входные и выходные сигналы (регистры, вход, выход и оперативное запоминающее устройство) определяются управляющими сигналами устройств, входящих в состав ОУ.

Управляющее слово ВМ составляется из управляющих разрядов MSA, MSB, АЛУ, DS, MSM, WR.

| MSA | MSB | АЛУ | DC | MSM | WR | |||||||||||||||||||

| a0 | a1 | а2 | a0 | a1 | а2 | M | S1 | S0 | C0 | E | X3 | X2 | X1 | a0 | WR | |||||||||

Задача устройства управления – обеспечить выдачу управляющего слова ЦП. Иначе он называется микрокод, который управляет работой аппаратуры ЦП. Обычно он записывается в постоянное запоминающее устройство (ПЗУ) центрального процессора (прошивается).

Рис. 4. Схема операционного устройства.

Задача контрольной работы состоит в том, чтобы расписать управляющее слово ЦП для различных микроопераций.

Задание

| № №варианта | Записать управляющее слово |

| 1 | Sß INPR  IR IR |

| 2 | INPRß IR  MAR MAR |

| 3 | IRß MAR  OUTR OUTR |

| 4 | MARß OUTR – AC |

| 5 | OUTRßAC – MDR – 1 |

| 6 | ACß MDR + PC + 1 |

| 7 | MDRß PC + INPR |

| 8 | OUTRß  |

| 9 | Sß INPR + 1 |

| 10 | INPRß IR + MAR |

| 11 | IRß MAR + OUTR + 1 |

| 12 | MARß OUTR – AC – 1 |

| 13 | OUTRß AC – MDR |

| 14 | ACß  |

| 15 | MDRß  |

| 16 | PCß  |

| 17 | OUTRß IR – 1 |

| 18 | IRß  |

| 19 | PCß  |

| 20 | Sß  |

| 21 | INPRß MAR + OUTR |

| 22 | MDRß OUTR + IR + 1 |

| 23 | ACß IR – PC – 1 |

| 24 | MARß INPR – AC |

| 25 | PCß  |

| 26 | IRß OUTR + PC |

| 27 | OUTRß MDR + INPR + 1 |

| 28 | Sß INPR – AC – 1 |

| 29 | MDRß AC – MAR |

| 30 | INPRß  |

| 31 | ACß  |

| 32 | MARß  |

| 33 | Sß OUTR |

| 34 | Sß AC+OUTR |

| 35 | Sß IR+INPR+1 |

| 36 | SßOUTR – MDR |

| 37 | SßINPR – MAR – 1 |

| 38 | SßIR+1 |

| 39 | SßOUTR – 1 |

| 40 | Sß AC  PC PC |

Выводы

Сделать выводы по проделанной работе.

ПАРА_АрхВМиС_Лекция_СМИРНОВ_Н_А_ИНБО-01,-02, -03,04,- 05, 06,18

1. Рассмотрим схему центрального процессора (операционное устройство) в 2 этапа. Сначала рассмотрим упрощенную схему. Затем усложним её.

Рис. 1 Схема вспомогательная

Подачей управляющих сигналов на дешифратор, мультиплексоры и АЛУ ведает устройство управления ЦП, которое выдает так называемое управляющее слово процессора. Оно состоит из разрядов управления этими устройствами. – по 2 разряда на мультиплексоры MSA и MSB, 3 разряда на дешифратор DС и 4 разряда на АЛУ.

| MSA | MSB | АЛУ | DC | |||||||||||

| a0 | a1 | a0 | a1 | M | S1 | S0 | C0 | E | X2 | X1 | ||||

Рассмотрим примеры.

1.Пусть надо в RG1 поместить сумму чисел из RG2 и RG0:

RG1 ← RG2 + RG0

| 10 | 00 | 0010 | 001 |

2. RG2 ←вход

| 11 | ХХ | 0000 | 010 |

3. RG0 ← RG2 ۸ вход

| 10 | 00 | 110Х | 000 |

4. S ← RG1

| 01 | ХХ | 1111 | 1ХХ |

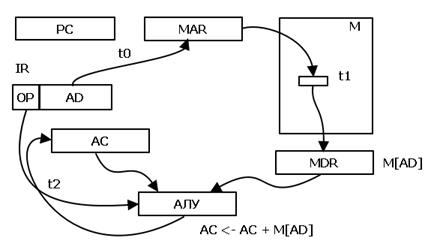

Рассмотрим более полный вариант схемы ЦП.

Рис. 2. Схема ОУ ЦП

Управляющее слово ВМ будет составлено из управляющих разрядов MSA, MSB, АЛУ, DS, MSM, WR.

| MSA | MSB | АЛУ | DC | MSM | WR | ||||||||||||||||||

| a0 | a1 | а2 | a0 | a1 | а2 | M | S1 | S0 | C0 | E | X2 | X1 | X0 | a0 | WR | ||||||||

Рассмотрим примеры управляющего слова ЦП для некоторых операций:

AC ←AC + MDR

| MSA | MSB | АЛУ | DC | MSM | WR |

| 001 | 100 | 0010 | 0001 | x | 0 |

MAR ← PC

| MSA | MSB | АЛУ | DC | MSM | WR |

| 000 | xxx | 0000 | 0011 | x | 0 |

MDR ← M[MAR]

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx | 0100 | 1 | 0 |

Пустой такт NOP

| MSA | MSB | АЛУ | DC | MSM | WR |

| xxx | xxx | xxxx | 1xxx | x | 0 |

Таким образом, мы спроектировали схему операционного устройства центрального процессора учебной ВМ.

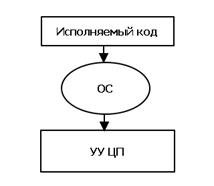

5.9. Устройство управления ЦП

Задача устройства управления – обеспечить выдачу управляющего слова ЦП. Иначе он называется микрокод, который управляет работой аппаратуры ЦП. Обычно он записывается в постоянное запоминающее устройство (ПЗУ) центрального процессора (прошивается).

Что должно делать УУ? У нас есть исполняемый код программы. Дальше в ходе выполнения исполняемого кода на ВМ им занимается операционная система – программа, которая выдаёт команды для УУ ЦП.

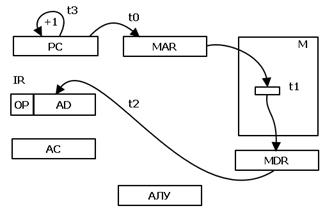

Рис. 3 Алгоритм управления в ВМ

Последовательность работы устройства управления задается циклами.

Для начала рассмотрим цикл выборки команды. Ведь прежде чем выполнить команду, надо выбрать её из памяти ВМ.

Рис. 4 Цикл выборки команды

Для выборки команды из памяти ВМ надо, во-первых, поместить адрес команды из регистра адреса команды в регистр адреса памяти, во-вторых, прочитать команду из ячейки памяти в регистр данных памяти, в-третьих. Переслать команду в регистр команды, в-четвертых, подготовить счетчик команд для выборки следующей команды – инкрементировать PC.

То есть, последовательно надо выполнить 4 действия, обозначенные на рис. 4 t0, t1, t2, t3. Следовательно, цикл выборки команды осуществляется за 4 такта.

Само выполнение команды происходит следующим образом:

Рис. 5 Цикл выполнения команды

Рассмотрим цикл выполнения команды на примере операции сложения.

Нулевой такт – пересылка адреса операнда из регистра команды в регистр адреса памяти. Первый такт – выборка из памяти операнда и размещение его в регистре данных памяти. Второй такт – собственно выполнение сложения в АЛУ с размещением результата в аккумуляторе.

Здесь мы рассматриваем выполнение команды с прямой адресацией, когда в адресном поле команды находится адрес операнда.

Машину Фон Неймана стали совершенствовать, поскольку для выполнения некоторых команд более удобными являются другие методы адресации операндов. Всего способов адресации насчитывается около 20. Из них в каждой конкретной ВМ используется только часть, по выбору конструкторов ВМ и в соответствии с назначением ВМ (ориентированием ВМ на обработку определённых видов информации).

Допустим, что у нас в памяти содержится такая информация:

| Адрес | Содержание |

| 30 | 40 |

| 40 | 50 |

| 50 | 60 |

Рассмотрим выполнение команды LDA (загрузку аккумулятора) с помощью различных методов адресации.

Прямая адресация: LDA 30 /загрузить в аккумулятор слово из ячейки с адресом 30. В результате выполнения команды АC ← 40.

Непосредственная адресация: LDA # 30. /загрузить в аккумулятор слово «30». В результате выполнения команды АC ← 30. То есть в команде содержится сам операнд, и загрузка его из памяти не требуется.

Косвенная адресация: LDA @ 30. /загрузить в аккумулятор слово из ячейки, адрес которой находится в ячейке 30. В результате выполнения команды АC ← 50. То есть в команде содержится не адрес операнда, а адрес адреса операнда. Соответственно, для подготовки операции требуется двойное обращение к памяти.

Существуют и другие способы адресации, которые здесь мы не будем рассматривать.

В общем случае для указания способа адресации в команде выделяется отдельное поле, содержащее необходимое количество разрядов. Для декодирования способа адресации при этом необходим ещё один цикл – цикл дешифрации команды.

Таким образом, мы получили наличие в УУ ЦП следующих циклов:

1) Цикл выборки команды – С0;

2) Цикл дешифрации команды – С1;

3) Цикл выполнения команды – С2;

4) Цикл обработки прерывания – С3.

Рис.6. Алгоритм работы устройства управления ЦП ВМ

Последний цикл необходим для обработки требований прерывания, вырабатываемых внешними устройствами ВМ (например, клавиатурой, устройством ввода/вывода и т.д.) или при появлении нештатных ситуаций при выполнении команд (деление на ноль, переполнение разрядов и др.). Как происходит цикл обработки прерывания мы рассмотрим позднее – при изучении операционных систем.

На основании изложенного алгоритм работы УУ ЦП имеет вид, представленный на рис. 6.

Как видите, ВМ реагирует на прерывание только после окончания выполнения очередной команды программы. В противном случае очень трудно запомнить текущее состояние ЦП для возврата в программу после обработки прерывания.

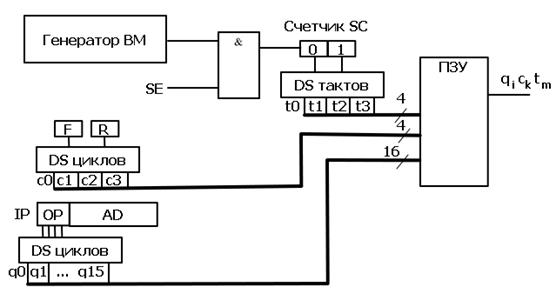

5.10. Структурная схема УУ ЦП

Структурная схема УУ ЦП изображена на рис. 7.

В основе УУ имеется ПЗУ; сигналы, вырабатываемые на его выходе, управляют работой ВМ. Генератор ВМ вырабатывает тактовую частоту. Сигнал SE представляет собой сигнал разрешения работы и останов. При SE=0 сигналы генератора ВМ не проходят через схему совпадения, и схема управления не работает – останов. При SE=1 сигналы генератора ВМ проходят через схему совпадения и поступают на вход двухразрядного счетчика, соединённого по выходу с дешифратором тактов. Логика работы последнего приведена на рис. 7.

Рис. 7. Структурная схема УУ ЦП

| ГИ | ||||||||||||||||||

| t0 | ||||||||||||||||||

| t1 | ||||||||||||||||||

| t2 | ||||||||||||||||||

| t3 | ||||||||||||||||||

Рис. 8. Временная диаграмма работы DС тактов

В ВМ такты не пересекаются по времени.

DС циклов работает по выходам двух триггеров F и R. В зависимости от состояния этих триггеров формируется сигнал на соответствующем его выходе.

| F | R | Цикл | Обозначение цикла |

| 0 | 0 | Выборки команды | С0 |

| 0 | 1 | Дешифрации команды | С1 |

| 1 | 0 | Выполнения команды | С2 |

| 1 | 1 | Прерывания | С3 |

DС команды работает по состоянию разрядов регистра команд, соответствующих полю кода операции. В нашем случае код имеет 4 разряда, что соответствует 16 выходам дешифратора команд.

Выходы всех трех дешифраторов составляют адрес ПЗУ, в котором записана (прошита) информация соответствующая содержимому управляющего слова процессора данного такта данного цикла данной команды.

Такова в общем виде структура УУ ЦП.

Таблица команд учебной ВМ представлена в таблице.

Обычно ВМ содержит команды различной длины – безадресные, одноадресные, двухадресные и др. В нашей учебной ВМ мы рассматриваем все команды единой длины равной 16 двоичным разрядам. Поэтому безадресные команды (с номерами от 12 до 15) содержат фиктивный адрес, равный FFF.

Рассмотрим для примера команду сложения ADD. Для неё в поле кода операции будет иметься значение 2 16-ричного кода. В адресном поле находится 12-разрядный адрес AD. Напишем микрокоманды циклов выборки и выполнения команды.

F=0, R=0, С0=1

С0t0: MAR← PC / подготовить выборку команды из памяти.

С0t1: MDR← M[MAR] / прочесть команду из памяти по адресу MAR.

С0t2: IR← MDR / поместить команду в регистр команды.

С0t3: PC← PC +1, F← 1/ подготовить адрес след. команды, перейти к циклу выполнения команды.

F=1, R=0, С2=1

С2t0: MAR← IR[AD] / передать адрес операнда в регистр адреса памяти MAR.

С2t1: MDR← M[MAR] / прочесть операнд из памяти по адресу MAR.

С2t2: AC← AC+MDR / выполнить сложение.

С2t3: F← 0/ перейти к циклу выборки команды.

Так выполняются микрокоманды ВМ в циклах выборки и выполнения команды сложения. Аналогичным образом можно описать порядок выполнения любой команды из перечня команд ВМ.

ВМ фон Неймана первоначально была рассчитана, как и наша учебная ВМ, только для одного типа адресации – прямой адресации. Для других типов адресации, что задаётся обычно в специальном поле команды, требуется наличие цикла дешифрации команды и осуществление выборки операндов соответствующим образом. Мы цикл дешифрации команды не рассматриваем, поскольку считаем, что используется только прямая адресация операндов.

Следующая контрольная работа состоит в том, чтобы вы научились строить команды из микрокоманд подобно рассмотренному примеру. Объем работы в контрольной работе велик. Для оформления работы надо использовать по крайней мере один лист формата А4.

Рассмотрим типовую задачу и приведём пример её решения.

Задача. По адресу 5А8 записана команда сложения ADD с адресом F12. По этому адресу записан операнд 731F. В регистре АС находится операнд 8721. Определить информацию, которая будет иметься в регистрах ВМ PC, MAR, MDR, IR, AC после выполнения данной команды.

Решение.

1. Определяем исходное состояние регистров.

2. Выписываем микрокоманды циклов выборки команды и выполнения команды.

3. Рассчитываем управляющие слова ВМ для каждой микрокоманды.

4. Определяем значения регистров после выполнения каждой микрокоманды.

5. Результаты оформляем в виде табл.2.2.

Таблица 2.2.

| Управл. сигналы, регистры | MSA | MSB | АЛУ | DС | MSM | WR | FR | PC | MAR | MDR | IR | AC |

| Исх. состояние регистров | 5А8 | 8721 | ||||||||||

| С0t0: MAR← PC | 000 | xxx | 0000 | 0011 | x | 0 | 00 | 5А8 | ||||

| С0t1: MDR← M[MAR] | xxx | xxx | xxxx | 0100 | 1 | 0 | 00 | 2F12 | ||||

| С0t2: IR← MDR | 100 | xxx | 0000 | 0010 | x | 0 | 00 | 2F12 | ||||

| С0t3: PC←PC+1, F←1 | 000 | xxx | 0001 | 0000 | x | 0 | 10 | 5А9 | ||||

| q2С2t0: MAR← IR[AD] | 010 | xxx | 0000 | 0011 | x | 0 | 10 | F12 | ||||

| q2С2t1: MDR← M[MAR] | xxx | xxx | xxxx | 0100 | 1 | 0 | 10 | 731F | ||||

| q2С2t2: AC← AC+MDR | 001 | 100 | 0010 | 0001 | x | 0 | 10 | FA40 | ||||

| q2С2t3: F← 0 | xxx | xxx | xxxx | 1xxx | x | 0 | 00 |

Таким образом, мы рассмотрели архитектуру устройства управления и операционного устройства учебной ВМ и принципы ее работы.

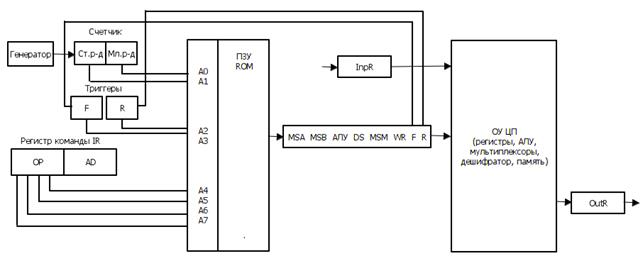

В результате мы получили следующую структурную схему ВМ:

Рис. 9. Структурная схема ЦП.

Как видно из схемы, ПЗУ может работать и без дешифраторов на входе, то есть к адресным входам ПЗУ подключены непосредственно выходы счетчика тактов, выходы регистров F, R и выходы поля кода операции регистра команды IR. Благодаря этому адрес ПЗУ состоит из 8 разрядов, и ёмкость ПЗУ существенно уменьшается без потери функциональности.

На выходе ПЗУ имеется управляющее слово ЦП, состоящее из 18 разрядов. Это слово поступает на соответствующие управляющие входы устройств операционного устройства ВМ. На схеме отдельно выделены регистры ввода-вывода, предназначенные для связи ВМ с внешним миром, а также показан регистр команды IR, который входит одновременно в состав УУ и ОУ ЦП ВМ.

2020-09-24

2020-09-24 2332

2332