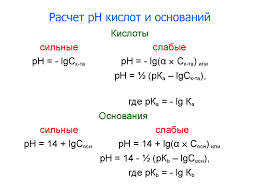

В противоположность динамическим статические запоминающие элементы способны помнить неограниченно долго, до тех пор, пока не будет отключен источник питания. Основу статического запоминающего элемента составляет триггер. Существует множество различных схем триггеров. Мы ограничимся одной, на наш взгляд, наиболее прогрессивной. Это схема триггера на так называемых комплементарных транзисторных парах.

Структура, показанная на рис. 3, называется комплементарной транзисторной парой.

+9В

|

V2

V2

| ||||

| ||||

| ||||

Вход Выход

Вход Выход

|

V1

V1

|

Рис.3

Рис.3

Между стоком транзистора V2 и истоком транзистора VI включен источник питания. Напряжение источника обычно выбирают около 9 В, хотя оно может быть и значительно меньше, скажем 1,5 В. Когда напряжение на объединенных затворах транзисторов равно нулю, V1 закрыт, а V2 – открыт и выход можно считать соединенной с источником питания и напряжение в ней, очевидно, равным напряжению источника питания. Когда на объединенных затворах действует положительное напряжение, транзистор VI, проводит, а транзистор V2 не проводит и на выходе схемы нулевое напряжение.

+9B

+9B

V2 V4

|

V1 V3

Рис.4.

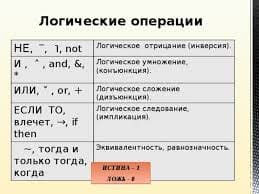

На рис. 4 изображены две комплементарные пары. Предположим, на затворах транзисторов VI и V2 установилось нулевое напряжение. Тогда вход находится под напряжением источника питания и под этим же напряжением находятся затворы транзисторов V3 и V4. Выход находится под нулевым напряжением, и под этим же напряжением находятся затворы транзисторов VI я V2. Состояние первой комплементарной пары (VI, V2) как бы поддерживает такое состояние второй (V3, V4), которое в свою очередь поддерживает исходное состояние первой пары.

Если принудительным образом задать положительное напряжение на затворах транзисторов VI и V2, то структура перейдет в противоположное состояние. Итак, структура, показанная на рис. 4, может находиться в одном из двух симметричных состояний. Она получила название триггера.

Триггер, показанный на рис. 4, обладает уникальным свойством: его электрическая цепь между источником питания и землей всегда разомкнута. Действительно, в одном состоянии не проводят транзисторы V2 и V3, а в другом VI и V4. Значит, когда триггер находится в одном из состояний, ток в цепи источника питания не течет и энергия в цепи источника питания не потребляется. Потребляется энергия только в моменты переключения. Пусть, к примеру, транзистор VI проводит, а транзистор V3 не проводит. Тогда процесс переключения состоит в том, что емкость затвора транзистора V3 заряжается от источника питания через промежуток исток-сток транзистора V2, который открывается в процессе переключения. Наоборот, емкость затвора транзистора VI разряжается через промежуток исток-сток транзистора V3, который также открывается в процессе переключения.

Процессы разрядки и зарядки конденсаторов приводят, в частности, к тому, что на переключение триггеров требуется, вообще говоря, некоторое время. У статических запоминающих элементов на комплементарных МДП-парах время переключения составляет несколько десятков наносекунд. То обстоятельство, что статические запоминающие элементы на комплементарных транзисторных парах не потребляют энергии в промежутках между переключениями, позволяет строить устройства, способные помнить неограниченно долго. Для этого нужно лишь обеспечить независимое питание подобных устройств от небольших батареек или аккумуляторов.

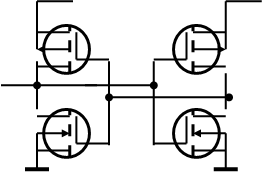

Полная схема статического запоминающего элемента на основе триггеров с комплементарными транзисторными парами показана на рис. 5.

Здесь транзисторы VI — V4 составляют уже знакомую схему триггера. Любой из транзисторов: либо VI, либо V3 — можно считать запоминающим, т. е. выполняющим те же функции, что и транзистор VI на рис. 2. Пусть, например, на рис. 4 роль запоминающего отводится транзистору VI. Остальные V2 — V4 служат для поддержания транзистора VI в одном из двух возможных состояний: проводящем (помнится 1) и непроводящем (помнится 0). Транзисторы V5 — V6 выполняют ту же функцию, что и транзистор V2 на рис. 2. Когда на затворы обоих транзисторов поданы положительные напряжения, точка а2триггера соединяется с проводом записи. При наличии на этом проводе положительного напряжения триггер запоминает 1, а при наличии нулевого напряжения — 0.

Транзисторы V7 и V8 играют ту же роль, что и транзистор V3 на рис. 3.

При наличии положительных напряжений на затворах обоих этих транзисторов точка а1 триггера соединяется с проводом чтения. Если триггер помнит 1, провод чтения оказывается замкнутым на землю, а если триггер помнит 0, провод чтения оказывается замкнутым на положительный полюс источника питания. Таким образом, в схеме на рис. 5 реализуются функции запоминания и выборки те же, что и в схеме, показанной на рис. 3.

Х

Х

У

Запись

Запись

Чтение

Чтение

|

Рис. 5. Статический запоминающий элемент.

Х

Чтение

Чтение

У

Запись

Запись

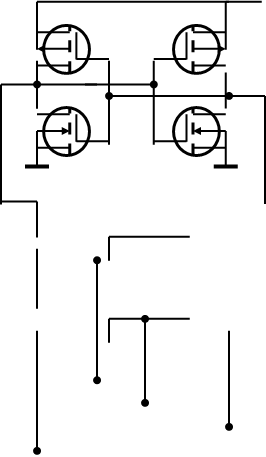

Рис.6. Условное обозначение статического запоминающего элемента

ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА.

Пусть имеется кристалл, содержащий 1000 ЭЗЭ. Провода «Чтение» и «Запись» можно соединить с каждым из них, однако этого нельзя делать с проводами Х и У, т.к. в этом случае запись и чтение будет осуществляться во все элементы одновременно. Делать для каждого ЭЗЭ свои выводы для управляющих проводов Х,У нереально (потребуется 20000 выводов).

Требуется какое-то иное решение. Оно состоит в использовании дешифраторов.

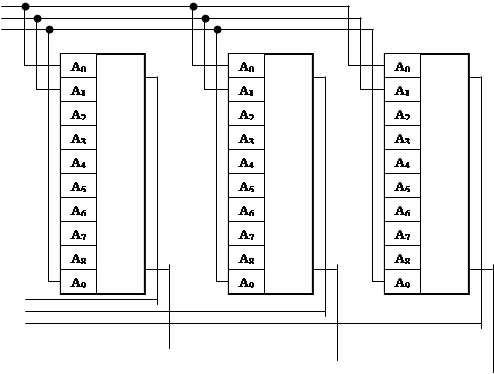

Обратимся к рис. 7. Здесь приведена функциональная схема модуля

оперативного запоминающего устройства (ОЗУ). Она содержит 1024 статических запоминающих элемента ЗЭ0—ЗЭ1023 (для простоты показаны только девять из них), расположенных в виде матрицы, состоящей из 32 строк по 32 элемента в каждой. Выводы «Чтение» и «Запись» всех элементов соединены между собой и подключены соответственно к двум выводам. Иначе обстоит дело с выводами X и Y. Выводы Y объединяются для каждого столбца и подсоединяются к соответствующим выводам дешифратора D2, как показано на рисунке. Выводы X объединяются в пределах каждой строки и подсоединяются к выводам дешифратора D1 опять-таки как показано на рисунке.

Предположим, что на входах А5—А9 дешифратора D2 действует некоторая

комбинация нулей и единиц: 01010. Положительное напряжение будет действовать на входах У всех запоминающих элементов 11-го слева столбца матрицы. Обратившись теперь к рис. 5, можно убедиться, что при этом окажутся открытыми транзисторы V5 и V7 всех запоминающих элементов десятого столбца. Однако открывания одного только

транзистора V5 или V7 недостаточно для того, чтобы элемент оказался подключенным к внешней цепи. Предположим далее, что на входах А0— А4 дешифратора di действует комбинация, например 01101. Ясно, что при этом положительное напряжение появится на 14 сверху выходе дешифратора и это напряжение

ЧтениеЗапись

Рис. 7. Функциональная схема модуля ОЗУ К537РУ1

будет действовать на всех входах X 14-й сверху строки матрицы запоминающих элементов. Таким образом, среди всех элементов матрицы окажется один, а именно тот, который расположен на пересечении 11-го слева столбца и 14-й сверху строки, имеющий положительные напряжения на обоих входах X и У. Причем оба внешних вывода этого элемента оказываются подключенными к триггеру. Манипулируя выходами «Чтение» и «Запись», можно либо запомнить 0 или 1, либо прочесть то, что было запомнено раньше. Для выбора одного из 1024 элементов нужно задать комбинацию положительных и нулевых напряжений на десяти входах: А0—А9. Все сказанное представляет собой несколько упрощенное описание выпус-

каемой промышленностью микросхемы 537РУ1. Микросхема позволяет выбрать один из 1024 статических запоминающих элементов, записать в него 0 или 1 и в дальнейшем прочесть эти данные.

Выпускают также микросхемы у которых запоминающие элементы объединены в группы и каждой комбинации на входах А соответствует выборка сразу целой группы, состоящей из 4, 8 и т.д. ЗЭ.

Оперативное ЗУ обладает определенной структурой, повторяющей структуру данных.

В качестве примера на рис. 8 показана структура ОЗУ, состоящая из 10

микросхем, входы которых соединены параллельно. Задавая на входах А0-А9 комбинацию нулей и единиц (адрес) можно в каждой микросхеме выбрать определенную ячейку, а на выходах получить сразу 10 бит.

|

Чтение слова

Чтение слова

Запись слова

Рис. 8.

Совокупность из N (в нашем случае 10) запоминающих элементов, доступ к которым открывается при задании одной комбинации, называют адресуемой запоминающей ячейкой или просто ячейкой. Комбинацию из 0 или 1 на входах А называют физическим адресом.

Т.о. ОЗУ представляет собой совокупность запоминающих ячеек, каждая из которых характеризуется своим адресом. Обычно для того, чтобы запомнить логическое слово или извлечь это слово из памяти, задают адрес ячейки, которая считается начальной,, и некоторое правило (алгоритм), по которому формируются последующие адреса.

При желании комбинацию нулей и единиц на адресных входах памяти можно рассматривать как число в двоичной системе счисления, что никак не меняет сути дела. Тогда один из возможных алгоритмов формирования слова переменной длины может быть увеличение всякий раз адреса очередной ячейки на единицу до тех пор, пока не будет просмотрено нужное число ячеек. Это простейший случай. Фрагменты слова переменной длины совсем не обязательно должны просматриваться подряд один за другим.

У хорошо организованной памяти порядок расположения слов в ячейках должен достаточно близко соответствовать порядку их просмотра в процессе реализации алгоритма. Как этого достигают? Один из методов — организация стеков. Стеком называется совокупность запоминающих ячеек, снабженная специальным устройством — указателем стека, задающим порядок просмотра ячеек. В стеке доступ разрешен всегда к одной и той же ячейке. При записи в стек очередного машинного слова все ранее находившиеся там слова смещаются вниз на одну позицию (т. е. адреса их уменьшаются на единицу). Самая верхняя ячейка освобождается, и в нее записывается очередное слово. Наоборот, при чтении слова (оно может быть только на самой верхней ячейке) все остальные слова поднимаются по одну позицию. Возможны еще более сложные методы организации памяти.

Современные ОЗУ обладают, как правило, иерархической структурой. Таким образом разрешается противоречие между требованиями большой емкости и большого быстродействия.

При правильно организованном алгоритме в течение достаточно долго времени можно ограничиваться просмотром относительно небольшого числа ячеек. Эти ячейки выделяют в виде отдельной группы, называемой сверхоперативной памятью (СОП). Принимают все меры к тому, чтобы обращение к ячейкам СОП занимало минимальное время. В частности, при конструировании СОП можно использовать быстродействующие транзисторы и обращаться ним по сокращенным адресам, имеющим смысл только для СОП. После получения информации, содержащейся в СОП, производится обмен данными меж ду СОП и ОЗУ, причем заменяется сразу содержимое всей группы ячеек. Число уровней иерархии может быть и больше двух.

2014-02-04

2014-02-04 663

663