Таблица 5.7

Таблица 5.6

Таблица 5.5

Таблица 5.4

Таблица 5.3

Таблица 5.2

Рисунок 5.7 - Регистр А управления Таймером-счетчиком 1 (TCCR1A)

Таблица 5.1

Выбор коэффициента предварительного деления ТС0

| CS02 | CS01 | CS00 | Описание |

| Таймер/счетчик остановлен | |||

| CK | |||

| CK/8 | |||

| CK/64 | |||

| CK/256 | |||

| CK/1024 | |||

| Внешний вывод T0, нарастающий фронт | |||

| Внешний вывод T0, спадающий фронт |

Условие в первой строке таблицы запрещает функционирование таймера/счетчика. В режимах деления частота берется непосредственно от тактовых импульсов (СК). При использовании режима работы с подсчетом внешних импульсов, вывод должен быть установлен на ввод информации (в соответствующий бит регистра направления данных DDRn необходимо записать «0»).

5.1.2 Timer/Counter0 (TCNT0)

| Бит $32($52) R/W Нач.знач. | TCNT0 | ||||||||

| MSB | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 5.4 - Таймер/счетчик 0 (TCNT0)

Таймер/счетчик реализован как инкрементирующий счетчик с возможностью чтения и записи. При записи числа в регистр TCNT0, если присутствуют тактовые импульсы, таймер/счетчик продолжает счет в следующем за операцией записи тактовом цикле таймера.

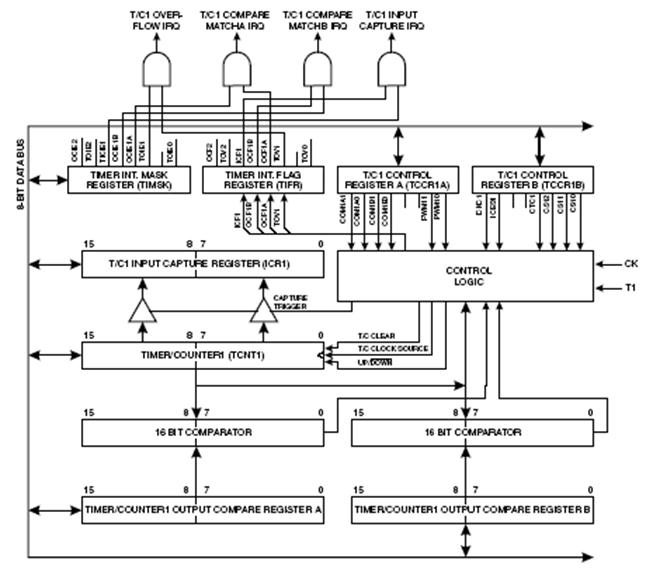

5.2 16- разрядный таймер/счетчик 1

16-разрядный таймер/счетчик может получать импульсы тактовой частоты - CK, импульсы с предварительного делителя (CK/8, CK/64, CK/256 или CK/1024), импульсы с внешнего вывода или быть остановлен соответствующими установками регистра TCCR1A. Флаги состояния таймера (переполнения, совпадения и захвата) и управляющие сигналы находится в регистре TIFR. Разрешение и запрещение прерываний от таймера 1 управляется регистром TIMSK (рис.5.5).

При работе таймера/счетчика 1 от внешнего сигнала, внешний сигнал синхронизируется с тактовым генератором ЦПУ. Для правильной обработки внешнего сигнала, минимальное время между соседними импульсами должно превышать период тактовой частоты процессора. Сигнал внешнего источника обрабатывается по спадающему фронту тактовой частоты процессора.

16-разрядный таймер/счетчик 1 можно использовать как счетчик с высоким разрешением, так и для точных применений с низким коэффициентом деления тактовой частоты. Более высокие коэффициенты деления можно использовать для медленных функций или измерения временных интервалов между редкими событиями.

Таймер/счетчик 1 поддерживает две функции совпадения. При этом используются регистры совпадения OCR1A и OCR1В в качестве источника для сравнения с содержимым счетчика. При совпадении содержимого регистров TCNT1 и OCR1A (или OCR1В) может происходить обнуление Таймера/счетчика 1 или переключение выхода OC1A (OC1B), в зависимости от того, что запрограммировано.

Рисунок 5.5 – Функциональная схема таймера-счетчика ТС1

Таймер/счетчик 1 можно использовать как 8-, 9- или 10-разрядный широтно-импульсный модулятор (ШИМ). В этом режиме счетчик и регистры OCR1А/ OCR1А работают как защищенный от дребезга независимый ШИМ с отцентрованными импульсами. Подробно эта функция будет описана ниже.

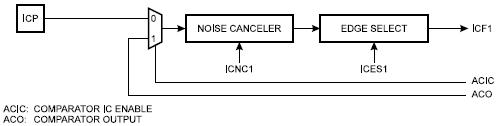

Функция захвата по входу предусматривает захват содержимого Таймера/счетчика1 в регистр захвата ICR1 и управляется внешним сигналом на входе захвата – ICP (рис.5.6). Работа режима захвата определяется управляющим регистром TCCR1. Кроме того, захват может осуществляться и по управлению от аналогового компаратора. Более подробно – см. аналоговый компаратор.

Рисунок 5.6 – Схема подключения вывода ICP

При работе захвата по входу, может быть включена схема подавления шума. При этом сигнал захвата возникает только в том случае, если событие, управляющее захватом, наблюдается на протяжении 4-х машинных циклов.

5.2.1 Timer/Counter1 Control Register A (TCCR1A)

| Бит $2F($4F) R/W Нач.знач. | TCCR1A | ||||||||

| COM1A1 | COM1A0 | COM1В1 | COM1В0 | - | - | PWM11 | PWM10 | ||

| R/W | R/W | R/W | R/W | R | R | R/W | R/W | ||

Биты 7,6 - COM1A1, COM1A0 (Compare Output Mode1A, Bits 1 and 0). Режим выхода совпадения, биты 1 и 0. Эти управляющие биты задают отклик вывода OC1A (Output CompareA pin 1) процессора на совпадение содержимого регистров сравнения OCR1A и таймера/счетчика 1 TCNT1. Поскольку это альтернативная функция порта, соответствующая линия порта должна быть сконфигурирована на выход (бит направления регистра DDRn должен быть нулевым). Конфигурация управляющих битов показана в табл.5.2.

Биты 5,4 - COM1В1, COM1В0 (Compare Output Mode1В, Bits 1 and 0). Режим выхода совпадения, биты 1 и 0. Эти управляющие биты задают отклик вывода OC1В (Output CompareВ pin 1) процессора на совпадение содержимого регистров сравнения OCR1В и таймера/счетчика 1 TCNT1. Поскольку это альтернативная функция порта, соответствующая линия порта должна быть сконфигурирована на выход (бит направления регистра DDRn должен быть нулевым). Конфигурация управляющих битов – аналогична битам COM1A1, COM1A0.

Установка режима совпадения.

| COM1A1 | COM1A1 | Описание |

| Таймер/счетчик 1 отключен от вывода OC1Х | ||

| Переключение выхода OC1Х | ||

| Сброс (0) вывода OC1Х | ||

| Установка (1) вывода OC1Х |

Примечание: Х=А или В.

В режиме ШИМ эти биты имеют другие функции, которые указаны в таблице 11. При изменении битов COM1x1/COM1x0, прерывание по совпадению должно быть запрещено очисткой соответствующего бита в регистре TIMSK. В противном случае прерывание может произойти во время изменения битов.

Биты 5..2 - зарезервированы. В AT90S8535 эти биты зарезервированы и всегда читаются как 0.

Биты 1,0 - PWM11, PWM10 (Pulse Width Modulator Select Bits). Биты установки ШИМ: Эти биты устанавливают режим работы таймера/счетчика 1 в качестве ШИМ (табл.5.3). Подробнее этот режим будет рассмотрен ниже.

Установка режима работы ШИМ.

| PWM11 | PWM10 | Описание |

| Работа ШИМ запрещена | ||

| 8-разрядный ШИМ | ||

| 9-разрядный ШИМ | ||

| 10-разрядный ШИМ |

5.2.2 Timer/Counter1 Control Register B (TCCR1B)

| Бит $2E ($4E) R/W Нач.знач. | TCCR1B | ||||||||

| ICNC1 | ICES1 | - | - | CTC1 | CS12 | CS11 | CS10 | ||

| R/W | R/W | R | R | R/W | R/W | R/W | R/W | ||

Рисунок 5.8 - Регистр B управления Таймером/Счетчиком 1 (TCCR1B)

Бит 7 - ICNC1 (Input Capture1 Noise Canceler (4 CKs)). Подавитель входного шума входа захвата. Если этот бит сброшен (0), подавление входного шума входа захвата запрещено. При этом захват срабатывает по первому заданному (нарастающему или спадающему) фронту сигнала на выводе ICP (Input Capture Pin). При установке бита ICNC1 обрабатываются четыре последовательные выборки сигнала на выводе ICP. Для срабатывания захвата все выборки должны соответствовать уровню, заданному битом ICES1. Частота выборок равна тактовой частоте процессора.

Бит 6 - ICES1 (Input Capture1 Edge Select). Выбор фронта сигнала захвата. Если бит ICES1 сброшен (0) содержимое таймера/счетчика 1 переписывается в регистр захвата по спадающему фронту сигнала на выводе ICP. Если бит установлен - по нарастающему фронту сигнала.

Биты 5,4 - зарезервированы. В AT90S8535 эти биты зарезервированы и всегда читаются как 0.

Бит 3 - CTC1 (Clear Timer/Counter1 on Compare Match). Очистка таймера счетчика 1 по совпадению. Если бит установлен (1), таймер/счетчик 1 устанавливается в $0000 в такте, следующем за событием совпадения. Если бит сброшен, таймер/счетчик 1 продолжает считать, пока не будет остановлен, сброшен, произойдет его переполнение или изменение направления счета. В режиме ШИМ этот бит не работает.

Биты 2,1,0 - CS12, CS11, CS10 (Clock Select1, Bits 2, 1 and 0). Выбор способа тактирования (см.табл.5.4). Эти биты определяют источник счетных импульсов для таймера/счетчика 1.

Выбор источника счетных импульсов.

| CS12 | CS11 | CS10 | Описание |

| Таймер/счетчик остановлен | |||

| CK | |||

| CK/8 | |||

| CK/64 | |||

| CK/256 | |||

| CK/1024 | |||

| Внешний вывод T1, нарастающий фронт | |||

| Внешний вывод T1, спадающий фронт |

5.2.3 Timer/Counter1 (TCNT1H, TCNT1L)

| Бит $2D($4D) R/W Нач.знач. | |||||||||

| MSB | - | - | - | - | - | - | - | TCNT1H | |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

| Бит $2C($4C) R/W Нач.знач. | |||||||||

| - | - | - | - | - | - | - | LSB | TCNT1L | |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 5.9 - Таймер/счетчик 1 (TCNT1H и TCNT1L)

Это 16-разрядный регистр, содержащий текущее значение таймера/счетчика 1. Чтобы чтение и запись двух байт счетчика происходило синхронно, для работы с ним иcпользуется временный регистр (TEMP).

Запись в таймер счетчик 1: При записи старшего байта в TCNT1H, записываемые данные помещаются в регистр TEMP. Затем, при записи младшего байта, он вместе с данными из TEMP переписывается в таймер/счетчик 1. Таким образом, при записи 16-разрядного значения первым должен записываться байт в TCNT1H.

Чтение таймера/счетчика 1: При чтении младшего байта из TCNT1L, он посылается в процессор, а данные из TCNT1H переписываются в регистр TEMP, то есть одновременно читаются все 16-разрядов. При последующем чтении регистра TCNT1H, данные берутся из регистра TEMP.

Таймер/счетчик 1 организован как суммирующий счетчик (в режиме ШИМ - суммирующий/вычитающий) с возможностью чтения и записи. Если выбран источник тактовых импульсов для таймера/счетчика 1, после записи в него нового значения, он продолжает счет в следующем после записи периоде тактовой частоты.

5.2.4 T/C1 Output Compare Register (OCR1AH, OCR1AL)

| Бит $2B ($4B) R/W Нач.знач. | OCR1AH | ||||||||

| MSB | - | - | - | - | - | - | - | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

| Бит $2A ($4A) R/W Нач.знач. | OCR1AL | ||||||||

| - | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 5.10 – Регистры совпадения А ТС1 (OCR1AH и OCR1AL)

5.2.5 T/C1 Output Compare Register (OCR1BH, OCR1BL)

| Бит $29 ($49) R/W Нач.знач. | OCR1BH | ||||||||

| MSB | - | - | - | - | - | - | - | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

| Бит $28 ($48) R/W Нач.знач. | OCR1BL | ||||||||

| - | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 5.11 – Регистры совпадения В ТС1 (OCR1ВH и OCR1ВL)

Регистры совпадения - 16-разрядные регистры, доступные для чтения и записи. В этих регистрах хранятся данные, которые непрерывно сравниваются с текущим значением таймера/счетчика 1. Действие по совпадению задается регистрами управления таймером/счетчиком 1 и регистром состояния.

Поскольку регистры OCR1A и OCR1В являются 16-разрядными, при записи нового значения в регистр, для того чтобы оба байта регистра записывались одновременно, используется временный регистр. При записи старшего байта, данные помещаются во временный регистр, который переписывается в OCR1AH или OCR1ВH при записи младшего байта в OCR1AL или OCR1ВL. Таким образом, для записи в регистр первым должен записываться старший байт.

5.2.6 Timer/Counter1 Input Capture Register (ICR1H, ICR1L)

| Бит $25 ($45) R/W Нач.знач. | |||||||||

| MSB | - | - | - | - | - | - | - | ICR1H | |

| R | R | R | R | R | R | R | R | ||

| Бит $24 ($44) R/W Нач.знач. | |||||||||

| - | - | - | - | - | - | - | LSB | ICR1L | |

| R | R | R | R | R | R | R | R | ||

Рисунок 5.12 – Регистры захвата ТС1 (ICR1H и ICR1L)

Регистр захвата (ICR1H, ICR1L) - 16-разрядный регистр, доступный только для чтения.

По нарастающему или спадающему фронту (в соответствии с выбором фронта импульса захвата ICES1) сигнала на выводе ICP, текущее значение таймера/счетчика 1 переписывается в регистр захвата ICR1. В это же время устанавливается флаг захвата ICF1.

Поскольку регистр захвата (ICR1х) является 16-разрядным, для чтения его значения, чтобы оба байта прочитались одновременно, используется временный регистр. При чтении младшего байта ICR1L, он посылается в ЦПУ, а старший байт регистра ICR1H переписывается во временный регистр. При чтении старшего байта, он принимается из временного регистра. Таким образом, для чтения 16-разрядного регистра первым должен читаться младший байт.

Регистр TEMP также используется при доступе к регистрам TCNT1, OCR1A и OCR1B. Если основная программа и подпрограммы обработки прерывания также обращаются к этому регистру, то прерывания должны быть запрещены до тех пор, пока содержимое указанных трех регистров не будет полностью прочитано.

5.2.7 Таймер/счетчик 1 в режимеШИМ

При выборе режима широтно-импульсной модуляции (ШИМ), таймер/счетчик 1 и регистры совпадения OCR1A и OCR1В формируют 8, 9 или 10-разрядный непрерывный свободный от "дрожания" и правильный по фазе сигнал, выводимый на выводы PD5 (OC1A) и PD4 (OC1В). Таймер/счетчик 1 работает как реверсивный счетчик, считающий от $0000 до конечного значения (табл.5.5). При достижении конечного значения счетчик начинает считать в обратную сторону до нуля, после чего рабочий цикл повторяется. Когда значение счетчика совпадает с 8, 9 или 10-ю младшими битами регистра OCR1A или OCR1В, выводы PD5 (OC1A) / PD4 (OC1В) устанавливаются или сбрасываются в соответствии с установками бит COM1A1 / COM1A0 или COM1B1 / COM1B0 в регистре TCCR1A (табл.5.6).

Конечное значение таймера и частота ШИМ

| Разрешение ШИМ | Конечное значение таймера (TOP) | Частота ШИМ |

| 8 бит | $00FF (255) | fTCK1/510 |

| 9 бит | $01FF (511) | fTCK1/1022 |

| 10 бит | $03FF (1023) | fTCK1/2046 |

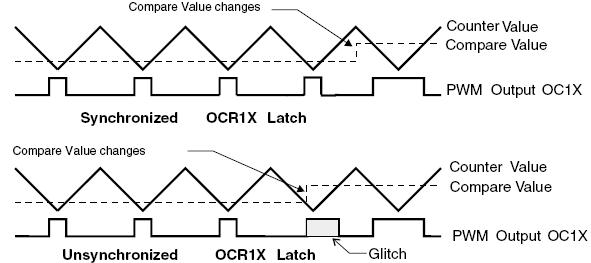

В режиме ШИМ, при записи в регистр OCR1A, 10 младших бит передаются во временный регистр и переписываются только при достижении таймером/счетчиком конечного значения (рис.5.13). При этом устраняется появление несимметричных импульсов (дрожания), которые неизбежны при асинхронной записи OCR1A.

Рисунок 5.13 – Эффект асинхронной записи содержимого OCR1х

При работе таймера/счетчика 1 в режиме ШИМ состояние счетного регистра изменяется от $0000 до конечного значения таймера (TOP) (см. табл.5.5), а затем снова до $0000, после чего цикл повторяется. Когда число, содержащееся в регистре счетчика TCNT1, совпадает с содержимым регистра совпадения OCR1A (или OCR1В), происходит изменение состояния соответствующего вывода микроконтроллера (OC1A или OC1B), в соответствии с табл.5.6. Таким образом, длительность импульса равна удвоенному значению содержимого регистра сравнения.

Установка режима совпадения при работе ШИМ

| COM1х1 | COM1х0 | Влияние на вывод OC1 |

| Не подключен | ||

| Не подключен | ||

| При совпадении, сбрасывается в «0» при прямом счете и устанавливается в «1» при обратном счете (неинвертированный ШИМ-сигнал) | ||

| При совпадении, устанавливается в «1» при прямом счете и сбрасывается в «0» при обратном счете (инвертированный ШИМ-сигнал) |

Если в регистр совпадения OCR1A (или OCR1В) записать значение $0000 или конечное значение (TOP), то при следующем совпадении вывод сравнения (OC1A или OC1B) переключится в устойчивое состояние, определяемое битами COM1х1 и COM1х0. Это показано в табл.5.7.

Выход ШИМ для OCR=$0000 или TOP

| COM1х1 | COM1х0 | OCR1х | вывод OC1х |

| $0000 | «0» | ||

| TOP | «1» | ||

| $0000 | «1» | ||

| TOP | «0» |

Особенностью работы таймера/счетчика Т1 в режиме ШИМ является то, что при записи в регистр сравнения младшие 10 разрядов записываемого числа на самом деле сохраняются в специальном временном регистре (не путать с регистром TEMP). А изменение содержимого регистра сравнения происходит только в момент достижения счетчиком максимального значения (ТОР). Благодаря такому решению исключается появление несимметричных выбросов сигнала на выходе модулятора (помех), которые были бы неизбежны при непосредственной записи в регистр сравнения (см.рис.5.13).

Соответственно, при чтении регистра сравнения в промежутке между записью в него и его действительным изменением возвращается содержимое временного регистра. То есть, всегда возвращается значение, записанное последним.

И несколько слов о прерываниях. При работе таймера/счетчика Т1 в режиме ШИМ может генерироваться прерывание по переполнению счетного регистра таймера/счетчика, а также прерывания от схемы сравнения.

В режиме ШИМ флаг переполнения таймера 1 (TOV1) устанавливается, когда счетчик изменяет направление счета в точке $0000. Прерывание по переполнению таймера 1 работает как при нормальном режиме работы таймера/счетчика, т.е. оно выполняется, если установлен флаг TOV1 и разрешены соответствующие прерывания. То же самое касается флага совпадения и прерывания по совпадению.

5.3 8- разрядный таймер/счетчик 2

Таймер-счетчик ТС2 может работать в двух режимах:

- режима таймера. В этом режиме ТС2 может использоваться для формирования временных интервалов, а также выполнять определенные действия при равенстве содержимого счетного регистра заданному значению;

- режим ШИМ. В этом режиме ТС2 работает как ШИМ-модулятор.

Основным режимом ТС2 от рассмотренных ранее является его возможность работать в асинхронном режиме (от дополнительного кварцевого резонатора).

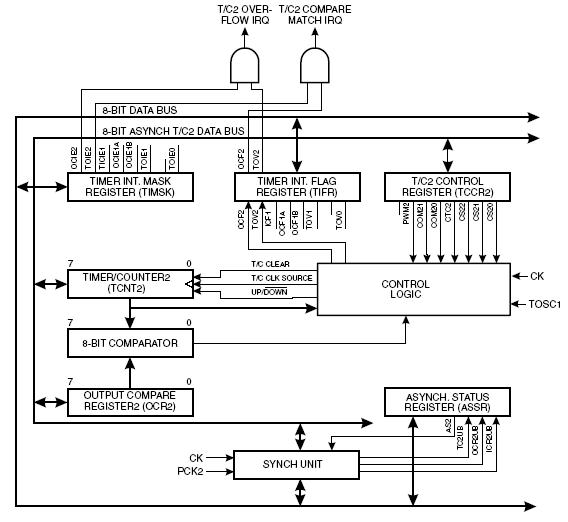

Структурная схема ТС2 приведена на рис.5.14.

Рисунок 5.14 – Структурная схема таймера/счетчика 2

Как видно из рисунка, в состав ТС2 входят два рабочих регистра (счетный регистр TCNT2 и регистр сравнения OCR2), 8-разрядный компаратор, регистр управления TCCR2, регистр состояния для асинхронного режима ASSR, а также блоки управления таймером и синхронизации.

Все флаги состояния таймера/счетчика (переполнения, совпадения и захвата) находятся в регистре флагов прерываний от таймеров TIFR, а разрешение/запрещение прерываний от таймера осуществляется установкой/сбросом соответствующих флагов регистра TIMSK.

Счетный регистр таймера/счетчика Т2 реализован как суммирующий (в режиме ШИМ — как суммирующий/вычитающий) счетчик и доступен в любой момент времени как для чтения, так и для записи. Расположен он по адресу $24 ($44). При записи в регистр TCNT2 во время работы таймера счет будет продолжен по следующему за операцией записи импульсу тактового сигнала таймера/счетчика. После подачи напряжения питания в регистре TCNT2 находится нулевое значение.

5.3.1 Timer/Counter2 Control Register (TCCR2)

| Бит $25($45) R/W Нач.знач. | TCCR2 | ||||||||

| - | PWM2 | COM21 | COM20 | CTC2 | CS22 | CS21 | CS20 | ||

| R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 5.15 - Регистр управления таймером/счетчиком 2 (TCCR2)

Для управления таймером/счетчиком Т2 предназначен регистр управ-ления TCCR2, расположенный по адресу $25 ($45). Формат этого регистра приведен на Рис. 6.11. Значение отдельных разрядов этих регистров будет чшсано далее. Неиспользуемые разряды регистров доступны только для пения и содержат «0».

Таймер/счетчик работает от тактового сигнала, который поступает на вход счетчика с предделителя, входящего в состав блока управления. А на предделитель, в свою очередь, может подаваться либо тактовый сигнал микроконтроллера, либо сигнал от дополнительного кварцевого резонатора (асинхронный режим работы).

Выбор коэффициента деления предделителя, а также запуск и остановка таймера/счетчика осуществляются с помощью разрядов CS22...CS20 регистра управления таймером TCCR2. Соответствие между состоянием этих разрядов и режимом работы таймера/счетчика приведено в табл.5.8.

2014-02-24

2014-02-24 758

758