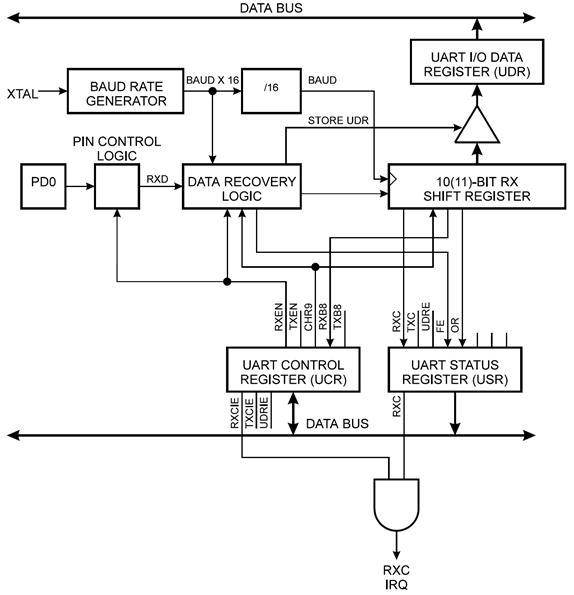

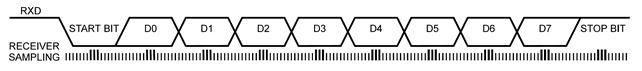

Структурная схема передатчика модуля UART приведена на рис.9.2. Логическая схема приемника обрабатывает сигнал на выводе RXD с частотой в 16 больше скорости передачи (для обработки одного бита принимаемой последовательности, производится 16 выборок входного сигнала). В состоянии ожидания одна выборка логического нуля интерпретируется как спадающий фронт стартового бита, после чего запускается последовательность обнаружения стартового бита. Если в первой выборке сигнала обнаружен нулевой отсчет, приемник обрабатывает 8, 9 и 10-ю выборки сигнала на выводе RXD. Эти выборки показаны жирными штрихами на рис.9.3. Если хотя бы две из трех выборок равны логической единице, стартовый бит считается шумом и приемник ждет следующего перехода из 1 в 0.

Рисунок 9.2 – Структурная схема приемника UART

Если обнаружен стартовый бит, начинается обработка бит данных. Решение об уровне данных также производится по 8, 9 и 10-й выборке входного сигнала, уровень входного сигнала определяется по равенству двух выборок. После того как уровень данных определен, данные вдвигаются в сдвиговый регистр приемника.

Рисунок 9.3 – Обработка принимаемых данных в UART

Для определения стопового бита хотя бы две из трех выборок входного сигнала должны быть равны 1. Если это условие не выполняется, в регистре USR устанавливается флаг ошибки кадра FE. Перед чтением данных из регистра UDR пользователь должен проверять бит FE для обнаружения ошибок кадра.

Независимо от принятия правильного стопового бита по окончанию приема символа принятые данные переписываются в UDR и устанавливается флаг RXC в регистре USR. Физически регистр UDR состоит из двух отдельных регистров, один используется для передачи данных, другой - для приема. При чтении UDR происходит доступ к регистру приемника, при записи - к регистру передатчика. При обмене 9-битовыми данными 9-й бит принятых данных записывается в бит RXB8 регистра UCR.

Если при приеме символа из регистра UDR не был прочитан предыдущий символ, в регистре UCR устанавливается флаг переполнения - OR. Установка этого бита означает, что последний принятый байт данных не переписывается из сдвигового регистра в регистр UDR и будет потерян. Бит OR буферирован и обновляется при чтении правильных данных из UDR. Таким образом, пользователь всегда может проверить состояние OR после чтения UDR и обнаружить происшедшее переполнение.

При сбросе бита RXEN в регистре UCR прием данных запрещается. При этом вывод PD0 можно использовать для ввода/вывода общего назначения. При установке RXEN, приемник подключен к выводу PD0 независимо от состояния бита DDRD0 в регистре DDRD.

2014-02-24

2014-02-24 545

545