Физическая и функциональная структура микропроцессора

Физическая структура микропроцессора достаточно сложна. Ядро процессора содержит главный управляющий модуль и исполняющие модули — блоки выполнения операций над целочисленными данными. К локальным управляющим схемам относятся: блок плавающей запятой, модуль предсказания ветвлений, модуль преобразования CISC-инструкций во внутренний RISC-микрокод, регистры микропроцессорной памяти (в МП типа VLIW до 256 регистров), регистры кэш-памяти 1-го уровня (отдельно для данных и инструкций), шинный интерфейс и многое другое.

В состав микропроцессора Pentium обычно входят следующие физические компоненты:

□ Core — ядро МП;

□ Execution Unit — исполняющий модуль;

□ Integer ALU — АЛУ для операций с целыми числами (с фиксированной запятой);

□ Registers — регистры;

Глава 5. Микропроцессоры и системные платы

□ Floating Point Unit — блок для работы с числами с плавающей запятой;

□ Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache);

□ Instruction Decode and Prefetch Unit и Branch Predictor — блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений;

□ Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая шины, и выход на системную шину к оперативной памяти (То RAM).

Функционально МП можно разделить на две части:

□ операционную, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров);

□ интерфейсную, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами.

Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) происходит во рремя выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

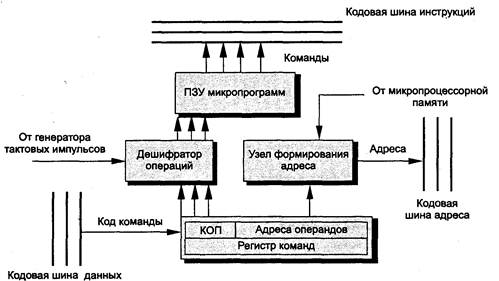

Устройство управления (УУ) является функционально наиболее сложным устройством ПК — оно вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций (КШИ) во все блоки машины. Упрощенная функциональная схема У У показана на рис. 5.1.

На рисунке представлены:

□ регистр команд — запоминающий регистр, в котором хранится код команды — код выполняемой операции (КОП) и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд;

□ дешифратор операций — логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов;

□ постоянное запоминающее устройство (ПЗУ) микропрограмм хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК процедур обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции проводу считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов;

Физическая и функциональная структура микропроцессора

Рис. 5.1. Укрупненная функциональная схема УУ

□ узел формирования адреса (находится в интерфейсной части МП) — устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП;

□ кодовые шины данных, адреса и инструкций — часть внутренней интерфейсной шины микропроцессора.

В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур:

□ выборка из регистра-счетчика адреса команды МПП адреса ячейки ОЗУ, где хранится очередная команда программы;

□ выборка из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

□ расшифровка кода операции и признаков выбранной команды;

□ считывание из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылка управляющих сигналов в эти блоки;

□ считывание из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов;

□ выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов;

□ запись результатов операции в память;

□ формирование адреса следующей команды программы.

Глава 5. Микропроцессоры и системные платы

2014-02-24

2014-02-24 1067

1067