В импульсном сигнале есть два стационарных состояния – наибольший сигнал, которому можно присвоить логическое значение 1, и наименьший сигнал - 0. Два синхронных импульсных сигнала способны описать информацию в 4 логических уровня сигнала. Восемь сигналов дают 256 сочетаний. Таким образом можно представить информации параллельным кодом.

В цифровых устройствах широко используются двоичные числа:

,

,

здесь ak = 0 или 1.

K = 0,1…. номер бита (двоичного разряда)

В этой системе десятичные числа можно, например, представить набором битов, как для двух битов в таблице 1.1:

| Число десятичное | Первый бит | Нулевой бит |

Объем информации оценивается следующим образом:

4 бита- тетрада,

8 бит – байт,

(16 бит – машинное слово),

210 байт = 1024 байт = 1 килобайт,

210 килобайт = 1024 килобайт = 1 мегабайт = 1048576 байт,

210 мегабайт = 1024 мегабайт = 1 гигабайт = 1048576 килобайт,

210 гигабайт = 1024 гигабайт = 1терабайт.

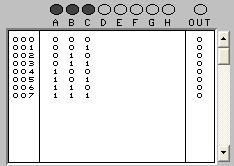

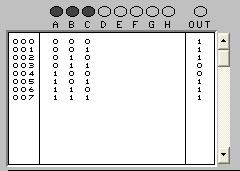

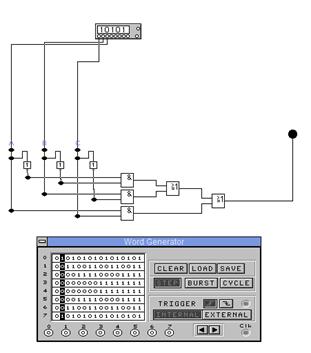

На рис. 6.2 (log_1.cd3) представлена таблица генератора части машинного слова для трех битов (С- младший бит) в программе для моделирования логических устройств.

Рис. 11.5. Таблица состояний для трех битов (С - младший бит).

В современных цифровых устройствах используют также шестнадцатиричную систему счислений.

В двоичной системе арифметические операции с числами выполняются с помощью устройств с логическими элементами. Набор логических элементов будет полным, если они реализуют все аксиомы алгебры логики:

1. X=0, если X≠1 и X=1, если X≠0 (“не дано третьего”)

2.  и

и  (отрицание)

(отрицание)

3.  ,

, ,

,  (конъюнкиция –«И»)

(конъюнкиция –«И»)

4.  ,

, ,

,  (дизъюнкция-«ИЛИ»)

(дизъюнкция-«ИЛИ»)

Логические элементы цифровой электроники.

1. Элемент «НЕ».

Рис. 11.6. УГО элемента «НЕ»

Этот элемент для логического отрицания (инверсии). Кружочек на выходном полюсе – признак инверсии.

Таблица 11.2.

| X | Y |

В алгебре Буля этой операции соответствует выражение

.

.

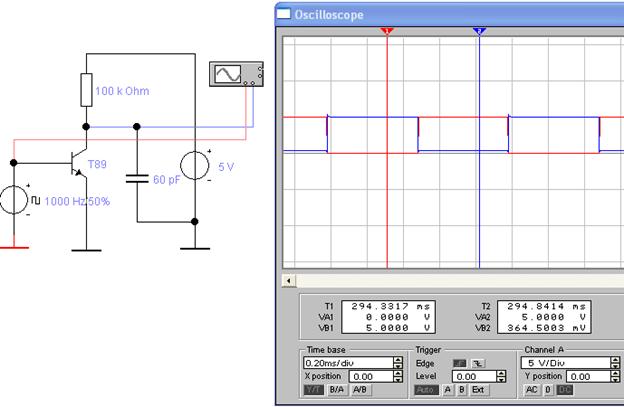

Пример аппаратной реализации функции приведен на рис.11.7.

Рис.11.7а. demo11_1а. Схема элемента «НЕ» и последовательности импульсов входного (красная) и выходного (синяя) напряжений.

Инверсия сигнала достигается с помощью усилителя напряжения на биполярном транзисторе.

2. Элемент «И».

Рис. 11.8. Условное обозначение логического элемента «И».

Этот элемент логического умножения (конъюнкции) имеет состояние на выходе Y, которое зависит от состояний на входах X 1 и X 2 в соответствие с таблицей 11.3.

Таблица 11.3.

| X 1 | X 2 | Y |

Булево выражение (логическое умножение):

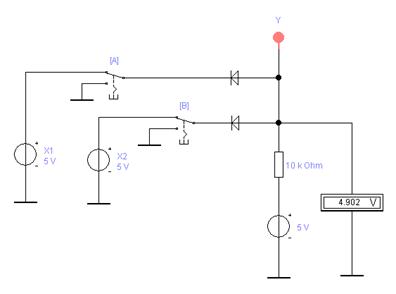

Пример схемы элемента приведен на рис.11.9.

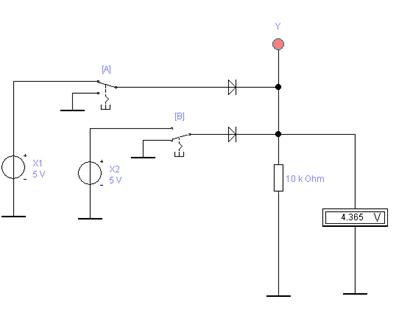

Рис.11.9. demo11_2. Схема, реализующая элемент «&».

В этой схеме логические значения 0 и 1 входных сигналов элемента & создаются источниками X1 и X2 (5В) с помощью переключателей A и B. Верхнему положению переключателя соответствует логическое значение 1. Логическое значение выходного сигнала регистрируется индикатором Y (красный, когда 1 при 1 на обоих входах). Напряжение выходного сигнала измерено вольтметром.

Напряжение на резисторе будет высоким (логическая 1) в том случае, когда оба диода будут заперты обратным напряжением источников X1 и X2. Если хотя бы один диод открыт, то потенциал выходного полюса будет небольшим из-за его заземления через малое сопротивление диода.

3. Элемент «ИЛИ» (дизъюнкция).

Рис. 11.10. Условное обозначение логического элемента «ИЛИ».

Таблица 11.4.

| X 1 | X 2 | Y |

Булево выражение (логическое суммирование):

Пример схемы элемента приведен на рис.11.11.

Рис.11.11. demo11_3. Схема, реализующая элемент «1».

В этой схеме при «1» на любом входе (или на обоих входах) открывается диод (или оба диода) и создается напряжение (логическая «1») на выходе.

4. Элемент «И-НЕ».

Рис. 11.12. Условное обозначение логического элемента «И-НЕ».

Таблица 11.5.

| X 1 | X 2 | Y |

Схема, реализующая эту операцию содержит каскадное включение элементов «&» и «НЕ»

5. Элемент «ИЛИ-НЕ».

Рис. 11.13. Условное обозначение логического элемента «ИЛИ-НЕ».

Таблица 11.4.

| X 1 | X 2 | Y |

Схема, реализующая эту операцию содержит каскадное включение элементов «1» и «НЕ».

Использование логических элементов.

Рассмотренные логические элементы применяются в различных цифровых устройствах. В качестве примера приведена схема, которая обеспечивает 1 на выходе (OUT) в соответствие с таблицей на рис.11.14 (demo11_4).

Рис. 11.14. demo11_4. Таблица состояний в примере.

Для этой таблицы можно составить булево выражение в совершенной дизъюнктивной нормальной форме в виде функции:

.

.

В этой форме для каждого набора аргументов, где функция равна 1 записывают их произведение, если значение аргумента равно 1. Если же значение аргумента равно нулю, то аргумент записывают с инверсией.

Так как в 6-ти строках функция имеет значение 1, то получилось 6 конъюнкций (произведений), которые включены в одну дизъюнкцию.

После упрощений с использованием специальных программ логических вычислений (или минимизацией по правилам булевой алгебры) получим:

.

.

Возможна запись той же функции в совершенной конъюнктивной нормальной форме. В этой форме составляют логическое произведение сумм. Записывают элементарные суммы для строк, где функция равна 0. Аргумент записывают с отрицанием, если его значение равно 1.

В нашем примере получим:

Выражению по первому варианту записи соответствует схема из логических элементов, реализующих три операции «И» и две операции «ИЛИ».

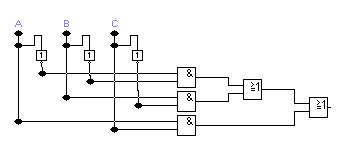

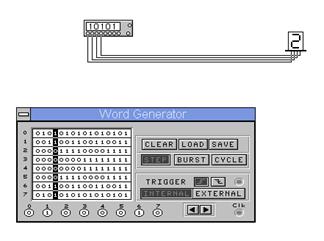

Рис. 11.15. demo11_4. Схема, реализующая заданную функцию.

Для испытания полученной схемы подадим последовательность слов, содержащих набор битов на входе по таблице рис.11.14 и на выход включим индикатор сигналов (рис. 11.16). На рисунке изображено состояние, которое установилось конкретно после задания на все входы логического 0.

Рис. 11.16. demo11_5. Пример использования логических элементов.

В примере видно, что на выходе индикатор светится (состояние 1 на выходе схемы) после задания на входы слов, соответствующих 0..2,5..7, и не светится при состояниях входов 3 и 4.

Рассмотренное устройство называется дешифратором. Они широко применяются в схемах управления всевозможными индикаторами.

На рис.11.17 приведен пример demo11_6, в котором показаны результаты вывода в шестнадцатиричной форме двоичных чисел с 4-мя битами.

Рис.11.17. demo11_6. Семисегментный индикатор с дешифратором.

Триггеры.

Важными элементами цифровой электроники являются триггеры – элементы, которые имеют два устойчивых состояния выходного сигнала 0 и 1.

В зависимости от возможностей управления, которые определяются устройством триггера, существует большое количество разных триггеров.

Наиболее распространены RS-триггеры, JK -(cчетные) триггеры, D –триггеры. Подробную справку о разных триггерах можно найти, например, в Википедии.

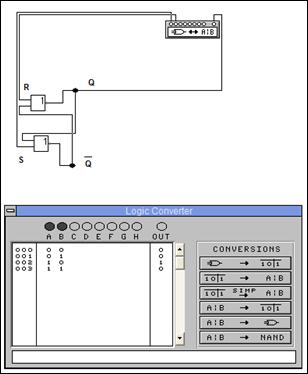

Простейшая схема RS-триггера и его таблица состояний при последовательном нарастании аргументов приведена на рис. 11.18.

Рис. 11.18. Схема RS –триггера и состояния при разных состояниях входов. Вход S –(set) установка по каналу A, вход R –(reset) сброс по каналу B, выход Q, инвертированный выход Q`.

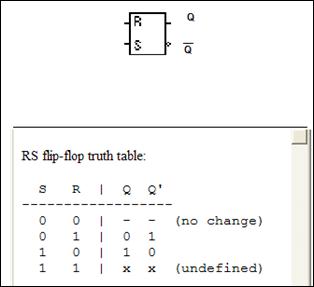

Значения аргументов могут изменяться произвольным образом. В общем случае в зависимости от предыстории состояние RS –триггера определяется таблицей на рис.11.19. Первая строка означает, что состояние выхода не изменяется в любом случае, если на оба входа установить 0. Последняя строка запрещает установку обоих входов в 1.

Рис. 11.19. Условное графическое обозначение RS –триггера и таблица состояний при разных состояниях входов.

Существуют так же синхронные триггеры, которые имеют еще входы – тактовый вход (счетный) и запрещающий входы, сигналы на которых разрешают или запрещают изменения состояния триггера.

RS - триггерыиспользуются составной частью в других триггерах.

.

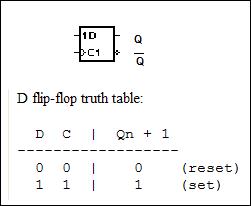

D- триггер имеет один информационный вход D и один тактовый вход C и имеет таблицу состояний, приведенную на рис.11.20.

Рис. 11.20. Условное графическое обозначение D –триггера и таблица состояний.

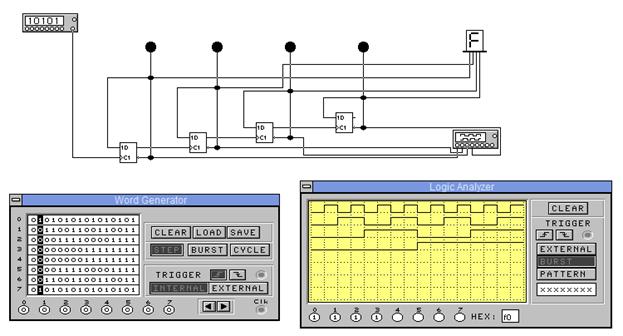

D –триггер имеет два выхода и он используется в счетчиках импульсов (см. рис.11.21.). Подача неинвертированного выходного сигнала на вход задержки D позволяет удваивать период выходных импульсов (т.е. уменьшать их частоту в два раза). В демонстрационном примере подсчитывается количество импульсов от генератора. На осциллограммах выходных сигналов видно, что состояние первого от входа счетчика триггера меняется от каждого импульса, второго – от каждого второго импульса, третьего – от каждого четвертого, третьего – от каждого восьмого. На рис. 6.21. зафиксировано состояние наибольшего числа в F (на восьми сегментном дисплее) в шестнадцатиричной системе счисления – 1 во всех четырех разрядах.

Рис. 11.21. demo11_7. Демонстрация последовательного счетчика импульсов на D-триггере.

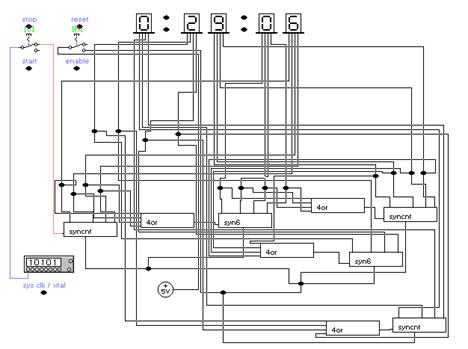

Счетчики импульсов используются в электронных часах. На рис.11.22 приведена схема таймера на 1 час.

Рис. 11.22. demo11_8. Таймер.

В таймере используются интегральные микросхемы счетчиков импульсов на JK- триггерах.

В этой демонстрации видно, что при отключении последовательности импульсов от тактового генератора кнопкой S состояние триггеров остается неизменным (если питание триггеров сохраняется). Это позволяет строить на основе триггеров устройства оперативной памяти – регистры.

В настоящее время существует много интегральных микросхем специального назначения, которые реализуют операции хранения (ЗУ – запоминающие устройства, памяти) и обработки цифровой информации (АЛУ-арифметико-логические устройства для операций с числами).

2014-02-09

2014-02-09 1481

1481