Рис. 18.4

импульса С = 1 на интервале  вход J = 1. Поэтому в момент среза импульса С триггер переходит в состояние Q = 1. На интервале

вход J = 1. Поэтому в момент среза импульса С триггер переходит в состояние Q = 1. На интервале  С = 0. Триггер не воспринимает входную информацию. На интервале второго тактового импульса

С = 0. Триггер не воспринимает входную информацию. На интервале второго тактового импульса  вход К = 1. Поэтому в момент t 4 триггер переключается: Q = 0. Во время действия третьего синхроимпульса J = 0; K = 0. Поэтому он не меняет своего состояния.

вход К = 1. Поэтому в момент t 4 триггер переключается: Q = 0. Во время действия третьего синхроимпульса J = 0; K = 0. Поэтому он не меняет своего состояния.

Обычно JK -триггеры снабжаются установочными входами R и S. Эти входы асинхронные. При S = 1 триггер устанавливается в состояние  . При R = 1 –

. При R = 1 –  .

.

Схема JK -триггеров достаточно сложна и в лекции не рассматривается. Схемное усложнение позволило ликвидировать состояние неопределенности и увеличить число входов J и K (обычно по 3).

|

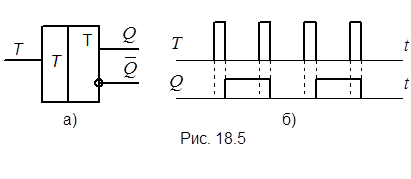

Счетный Т -триггер реализует только четвертую строку таблицы рис.18.4а. Таким свойством обладает JK -триггер, когда его входы J = K = 1. При таком включении входов триггер переключается в момент среза каждого тактового импульса. Отсюда следует, что счетный триггер имеет один тактовый вход, который обозначают символом «Т». Обозначение Т -триггера приведено на рис. 18.5а. На рис.18.5б приведены временные диаграммы, поясняющие его работу. Из диаграмм видно, что частота повторения импульсов на выходе триггера Q в два раза меньше частоты повторения импульсов на входе Т, т. е. Т -триггер делит частоту входных импульсов на 2. Счетные триггеры широко применяются в счетчиках, распределителях и делителях частоты.

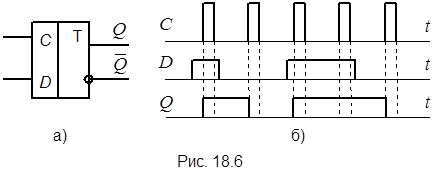

D -триггер запоминает входную информацию в момент фронта синхроимпульса и хранит ее до следующего тактового импульса. D -триггер может быть выполнен на основе JK -триггера, при включении на входе элемента "НЕ", обеспечивающего условие  . Отсюда следует, что D -триггер имеет тактовый вход С и вход D. Его работа описывается второй и третьей строкой таблицы рис. 18.4а, т. е.

. Отсюда следует, что D -триггер имеет тактовый вход С и вход D. Его работа описывается второй и третьей строкой таблицы рис. 18.4а, т. е.  . Поэтому D -триггер является элементом памяти и находит широкое применение, в том числе в регистрах. Условное обозначение D -триггера и временные диаграммы, поясняющие его работу, приведены на рис. 18.6.

. Поэтому D -триггер является элементом памяти и находит широкое применение, в том числе в регистрах. Условное обозначение D -триггера и временные диаграммы, поясняющие его работу, приведены на рис. 18.6.

|

В микросхемном исполнении триггеры выпускаются в составе многих серий цифровых интегральных микросхем. Для условного обозначения им присвоены следующие индексы:

RS -триггеры – ТР;

JK -триггеры – ТВ;

D -триггеры – ТМ.

Например, микросхема К555 ТР2 содержит 4 RS -триггера.

Микросхемы К555 ТВ6 и К555 ТВ9 включают в свой состав по два IK триггера каждая. Микросхемы позволяют путем внешних коммутационных изменений получить схемы, выполняющие функции RS, D и Т -триггеров.

Одной из наиболее распространенных операций в устройствах дискретной обработки информации является счет импульсов (таймеры ЭСЧ, цифровые измерительные приборы, АЦП и т. п.). Эту операцию выполняют счетчики, которые по назначению делятся на простые (выполняющие операцию суммирования и вычитания) и реверсивные.

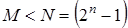

Простые счетчики осуществляют переходы от предыдущего состояния к последующему только в одном направлении, т. е. могут или суммировать или вычитать импульсы. Реверсивные счетчики имеют переходы в двух направлениях – прямом и обратном. В зависимости от системы счисления счетчики делятся на двоичные и десятичные. Синхронизация счета бывает двух типов – синхронная (по фронту импульса) и асинхронная (по импульсу). В основу построения счетчиков положено применение Т- триггеров. Максимальное число, которое может быть записано в счетчике равно  , где n – число разрядов счетчика. Каждый разряд двоичного счетчика представляет собой триггер.

, где n – число разрядов счетчика. Каждый разряд двоичного счетчика представляет собой триггер.

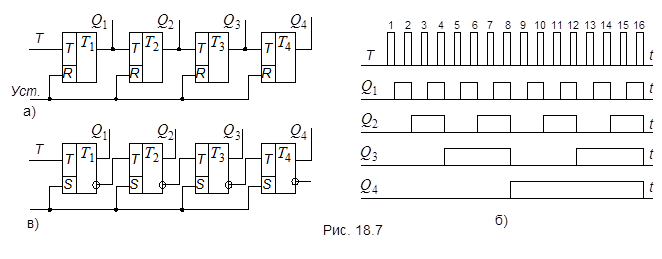

Схема четырехразрядного счетчика на сумму приведена на рис. 18.7а. На рис. 18.7б приведены эпюры, поясняющие принцип его работы. На схеме " Т" – счетный вход счетчика,  - выходы разрядов, "УСТ" – установка состояния. Связь между триггерами – по прямым входам. Перед началом счета все триггеры устанавливаются в нулевое состояние -

- выходы разрядов, "УСТ" – установка состояния. Связь между триггерами – по прямым входам. Перед началом счета все триггеры устанавливаются в нулевое состояние -  . Для этого достаточно подать единичный потенциал по шине "УСТ". Счетные импульсы поступают на вход " Т " первого триггера и переключаю его срезом каждого импульса (диаграмма Q 1). Срезом импульсов выхода Q 1 переключается триггер Т 2 (диаграмма Q 2). Триггеры Т 3 и Т 4 переключаются по аналогичному алгоритму.

. Для этого достаточно подать единичный потенциал по шине "УСТ". Счетные импульсы поступают на вход " Т " первого триггера и переключаю его срезом каждого импульса (диаграмма Q 1). Срезом импульсов выхода Q 1 переключается триггер Т 2 (диаграмма Q 2). Триггеры Т 3 и Т 4 переключаются по аналогичному алгоритму.

Все состояния триггеров счетчика отражаются таблицей состояний 18.1. Нетрудно видеть, что состояние разрядов счетчика представляет собой запись числа поступивших на данный момент импульсов в двоичном коде. После записи максимального числа  счетчик автоматически обнуляется, т. е. устанавливается исходное состояние

счетчик автоматически обнуляется, т. е. устанавливается исходное состояние  . Далее начинается новый цикл счета. При необходимости увеличить число N достаточно подключить к выходу счетчика дополнительные разряды (триггеры).

. Далее начинается новый цикл счета. При необходимости увеличить число N достаточно подключить к выходу счетчика дополнительные разряды (триггеры).

Аналогично суммирующему счетчику строится счетчик на вычитание. Схема такого счетчика приведена на рис. 18.7в. В этой схеме связь между триггерами выполнена по инверсным выходам, а шина "УСТ" объединяет установочные входы триггеров " S ".

Перед началом счета все триггеры устанавливаются в состояние  . С поступлением на вход Т счетных импульсов происходит изменение состояний триггеров на вычитание. Все состояния триггеров приведены в таблице 18.2. Таблица представляет собой двоичную запись линейно убывающих чисел.

. С поступлением на вход Т счетных импульсов происходит изменение состояний триггеров на вычитание. Все состояния триггеров приведены в таблице 18.2. Таблица представляет собой двоичную запись линейно убывающих чисел.

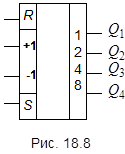

Часто возникает необходимость в счетчиках, которые могли бы поочередно выполнять сложение и вычитание поступающих импульсов. Такие счетчики называются реверсивными. Реверсивные счетчики снабжаются системой коммутации связей между триггерами (с прямых на инверсные и обратно) и двумя счетными входами. При подаче импульса на вход "+1" между триггерами устанавливается связь по прямым выходам, при этом код, записанный в счетчике, устанавливается на единицу. При поступлении импульса на вход "-1" происходит обратная коммутация триггеров и код, записанный в счетчике, уменьшается на единицу. Условное обозначение реверсивного счетчика показано на рис. 18.8.

Таблица 18.1 Таблица 18.2

| № импульса |  |  |  |  | № импульса |  |  |  |  | |

3 3 | ||||||||||

В ряде случаев возникает необходимость вернуть счетчик в исходное состояние  после записи некоторого числа

после записи некоторого числа  . Для создания такого счетчика достаточно ввести в него цепь ОС. Например, декадные счетчики выполняются на основе четырехразрядных двоичных счетчиков. Но счет необходимо выполнять от 0 до 9, т. е. после записи цифры 9 необходимо возвратить триггеры в исходное состояние. Значит, цепь ОС должна выделить двоичную комбинацию числа 10. Наиболее просто она может быть образована с использованием логического элемента "И" (рис. 18.9).

. Для создания такого счетчика достаточно ввести в него цепь ОС. Например, декадные счетчики выполняются на основе четырехразрядных двоичных счетчиков. Но счет необходимо выполнять от 0 до 9, т. е. после записи цифры 9 необходимо возвратить триггеры в исходное состояние. Значит, цепь ОС должна выделить двоичную комбинацию числа 10. Наиболее просто она может быть образована с использованием логического элемента "И" (рис. 18.9).

Промышленность выпускает счетчики в виде интегральных микросхем, в том числе двоичные (на сложение и вычитание), двоично-десятичные (декады), реверсивные, с программируемым коэффициентом счета. Например:

К555 ИЕ10 – синхронный, четырехразрядный двоичный счетчик;

К555 ИЕ9 – четырехразрядный двоично-десятичный счетчик;

К555 ИЕ6; ИЕ7 – двоично-десятичный и двоичный реверсивные

четырехразрядные счетчики;

К555 ИЕ14 – асинхронный счетчик-делитель с программируемым

коэффициентом деления.

2014-02-12

2014-02-12 921

921