ADSP-21160 – первый процессор второго поколения SHARC DSP. Процессоры этого семейства разрабатывались для решения задачи повышения производительности вычислений с возможностью сохранения максимальной совместимости кода с процессорами первого поколения SHARC DSP. Выигрыш в производительности достигается за счет 2 - 2,5-кратного повышения частоты процессорного ядра (с 40 до 80 или 100 МГц) и использованием SIMD-архитектуры процессорного ядра.

Повышение тактовой частоты достигается за счет использования внутреннего тактирования с частотой, являющейся множителем (>1) частоты входного тактового сигнала CLKIN.

Изменения, коснувшиеся также организации внутренней памяти, шин данных, архитектуры процессора ввода/вывода (DMA-контроллера и линк-портов), а также управляющих и статусных регистров, тем не менее в общем случае требуют некоторых дополнительных затрат, связанных с переносом и модификацией программ (porting), написанных, например, для ADSP-2106x на платформу ADSP-2116x.

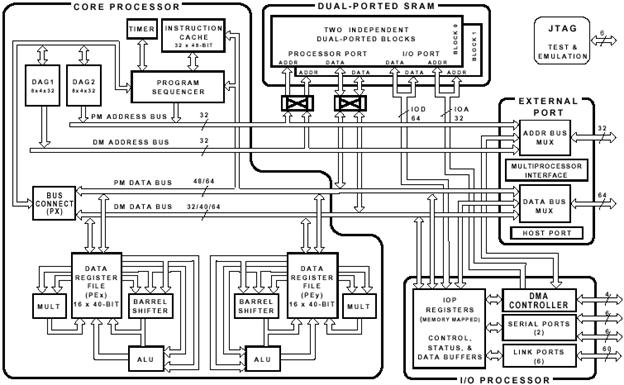

Архитектура процессора ADSP-21160 приведена на рис.1.

Рис.1

2015-01-30

2015-01-30 492

492