Главные изменения связаны с появлением в ядре двух одинаковых по своим возможностям процессорных элементов PEx и PEy, каждый из которых содержит свой регистровый файл и свои вычислительные устройства: ALU, MAC и SHIFTER. Форматы данных, поддерживаемые процессорными элементами, полностью совпадают с форматами данных вычислительных устройства ADSP-2106x.

Использование двух процессорных элементов требует использования и двух независимых регистров арифметического статуса. Поэтому вместо регистра ADSTAT введены два регистра ASTATx (соответствует регистру ASTAT) и ASTATy. Аналогичные изменения коснулись регистра STKY (появились STKYx и STKYy).

Процессорный элемент PEx обрабатывает все вычислительные инструкции в SISD-режиме, использует те же названия регистров, что и ADSP-2106x (Rx, Fx) и поэтому может выполнять программы ADSP-2106x без каких-либо модификаций.

Процессорный элемент PEy может синхронно выполнять только те же вычислительные операции, что и процессорный элемент PEx, но над своими регистрами (Sx) при включенном режиме параллельной обработки данных SIMD (бит PEYEN в регистре MODE1).

Если при выполнении вычислений происходит исключительная ситуация, то для принятия решения о генерации соответствующего прерывания программный секвенсор "складывает" биты регистров STKYx и STKYy по логическому ИЛИ (т.е. если исключительная ситуация произошла хотя бы в одном процессорном элементе, то прерывание генерируется).

Следует более подробно остановиться на работе с регистровым файлом. Поскольку процессор поддерживает доступ к регистрам двух процессорных элементов, то следует иметь в виду следующие правила:

- регистры R0-R15, F0-F15 всегда относятся в PEx для всех вычислительных операций и операций пересылки данных, независимо от того, в каком режиме работает процессор (SISD или SIMD);

- регистры R0-R15 и F0-F15 относятся к обоим процессорным элементам PEx и PEy для всех вычислительных инструкций в режиме SIMD;

- регистры S0-S15 всегда относятся к процессорному элементу PEy и могут использоваться только в инструкциях пересылки данных в режимах SISD и SIMD.

Введена инструкция обмена содержимого двух регистров из разных процессорных элементов:

S1 <-> R1;

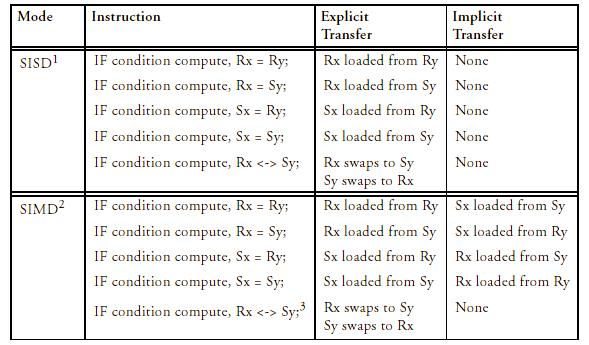

Процессор поддерживает однонаправленные (unidirectional) и двунаправленные (bidirectional) пересылки данных между регистрами двух процессорных элементов в обоих режимах (т.е. регистры PEy можно использовать и в SISD режиме, но только для хранения данных – они не могут являться операндами или приемниками результата для вычислительных инструкций).

В SISD-режиме пересылки между регистрами одного процессорного элемента и между регистрами разных процессорных элементов всегда однонаправленные. Если инструкция пересылки условная, то условие ее выполнения проверяется всегда в процессорном элементе PEx.

В SIMD-режиме пересылки между регистрами двунаправленные и состоят из явной и неявной пересылок. Источником и приемником всегда являются два регистра. Если пересылка условная, то для выполнения явной пересылки проверяется условие в PEx, я для выполнения неявной – аналогичное условие в PEy, например:

{ установлен режим SIMD (бит PEYEN в MODE1 равен 1) }

If EQ r4=r3; {проверка бита EQ в PEx и PEy}

{если в ASTATx EQ=1, то переслать r3 в r4}

{если в ASTATy EQ=1, то переслать s3 в s4}

Источниками и приемниками данных при пересылках, естественно, могут быть и регистры DAG, системные регистры и регистры управления. В режиме SIMD следует учитывать некоторые тонкости при обмене данными между такими регистрами и регистрами регистрового файла. Если приемником является регистр данных, то в оба процессорных элементов копируется одно и то же значение. Если же регистр данных является источником, то в одних случаях выполняется и явная и неявная пересылки (когда у приемника есть "регистр-дополнение", например, ASTATx-ASTATy), а в других – только явная пересылка (когда регистра-дополнения нет).

2015-01-30

2015-01-30 597

597