Задача центрального процессора — выполнять программы (программный код), находящиеся в основной памяти (кэш-памяти). Он вызывает команды из памяти (кэш-памяти), определяет их тип, а затем выполняет их одну за другой. Компоненты соединены шиной, представляющей собой набор параллельно связанных проводов, по которым передаются адреса, данные и сигналы управления.

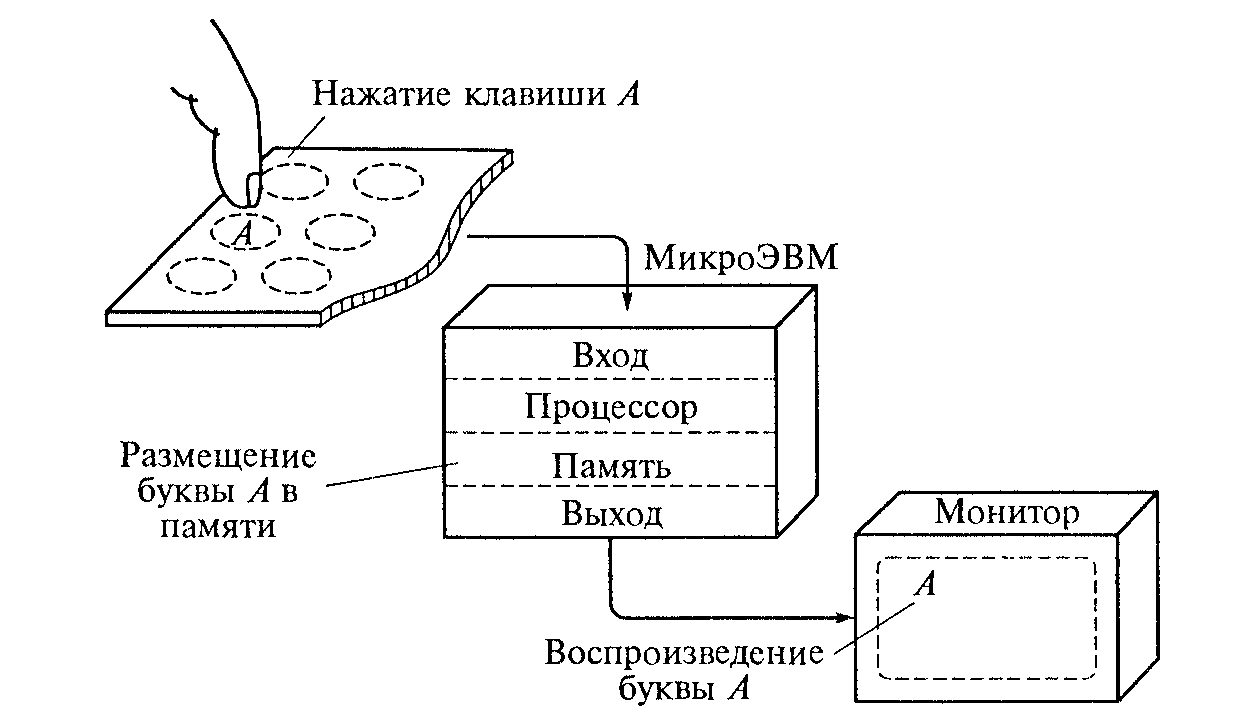

Рис.26 Действие при работе с МП

Когда команды извлекаются из кэша (или основной памяти), их необходимо декодировать и отправить на исполнение.

Как видно, весь процесс обработки команды состоит из четырех шагов, что и определяет так называемый 4 – ступенчатый процесс (конвейер).

1. Извлечение из кэша (оперативной памяти).

2. Декодирование (разборка команды).

3. Исполнение команды (применение действий).

4. Запись в кэш (оперативную память).

Каждую из этих ступеней команда должна проходить ровно за один такт. Поэтому чем быстрее каждая из ступеней выполняет свои функции, тем быстрее работает весь процессор и тем выше его тактовая частота. Выполнение всех этих четырех команд определяет цикл. Большинство процессоров действительно исполняют команды за один цикл, но существуют сложные команды, для которых требуется несколько циклов. При исполнении сложных команд различные устройства задействуют собственные исполнительные конвейеры, тем самым, добавляя еще несколько ступеней к основному конвейеру процессора. Количество ступеней определяет глубину конвейера.

Программный код — это последовательность команд, или инструкций, каждая из которых определенным образом закодирована и расположена в целом числе смежных байтов памяти. Каждая инструкция обязательно имеет операционную часть, несущую процессору информацию о требуемых действиях. Операндная часть, указывающая процессору, где находится его «предмет труда» — операнды, — может присутствовать в явном или неявном виде и даже отсутствовать. Операндная часть может описывать от нуля до двух операндов, участвующих в выполнении данной инструкции (есть инструкции, в которых, помимо двух операндов, задается еще и параметр инструкции). Здесь могут быть сами значения операндов (непосредственные операнды); явные или неявные указания на регистры процессора, в которых находятся операнды; адрес (или его составная часть) ячейки памяти или порта ввода-вывода; регистры процессора, участвующие в формировании адреса, и разные комбинации этих компонентов. Длина инструкции 32-битного процессора семейства х86 может быть от 1 до 12 байтов (а с префиксами — и до 17 байтов) и определяется типом инструкции. Исторически сложившийся формат инструкций х86 довольно сложен, и «понять», сколько байтов занимает конкретная инструкция, процессор может, лишь декодировав ее первые 1-3 байта. Инструкции могут предшествовать префиксы (к счастью, всегда однобайтные, но их может быть несколько), указывающие на изменение способа адресации, размера операнда или/и необходимость многократного (по счетчику и условию) повторения для данной инструкции. Адрес (логический) текущей исполняемой инструкции хранится в специальном регистре — указателе инструкций (InstructionPointer, IP), который соответствует счетчику команд фон-неймановской машины. После исполнения так называемой линейной инструкции этот указатель увеличивает свое значение на ее длину, то есть указывает на начало следующей инструкции. Линейная инструкция не нарушает порядок выполнения инструкций, определяемый последовательностью их расположения в памяти (по нарастанию адреса). Помимо линейных инструкций существуют инструкции передачи управления, среди которых различают инструкции переходов и вызовов процедур. Эти инструкции в явном или неявном виде содержат информацию об адресе следующей выполняемой инструкции, который может указывать на относительно произвольную ячейку памяти.

Инструкции переходов и вызовов могут быть безусловными (ни от чего не зависящими) и условными. Произойдет ли условный переход (вызов) или нет, зависит от состояния флагов (признаков) на момент исполнения данной инструкции. Если переход (вызов) не состоится, то исполняется инструкция, расположенная в памяти вслед за текущей. Вызов процедуры характерен тем, что перед ним процессор сохраняет в стеке (стек — это область ОЗУ) адрес следующей инструкции, и на этот адрес передается управление после завершения исполнения процедуры (этот адрес извлекается из стека при выполнении инструкции возврата). Переход выполняется безвозвратно.

Последовательность исполнения инструкций, предписанная программным кодом, может быть нарушена под воздействием внутренних или внешних (относительно процессора) причин. К внутренним причинам относятся исключения (exceptions) — особые ситуации, возникающие при выполнении инструкций. Наглядным примером исключения является попытка деления на ноль. При возникновении условия исключения процессор автоматически выполняет вызов процедуры обработки исключения, после которой он может вернуться к повторному исполнению инструкции, породившей исключение, или следующей за ней. Вариант поведения зависит от типа произошедшего исключения. Исключения широко используются современными операционными системами. На основе обработки исключений строится система виртуальной памяти и реализуются многие функции многозадачных операционных систем.

Внешними причинами изменения нормальной последовательности инструкций являются аппаратные прерывания — вызовы процедур под воздействием электрических сигналов на специальные выводы процессора или по получении сообщения по специальному интерфейсу контроллера прерываний. Эти сигналы могут подаваться совершенно неожиданно для исполняемой программы; правда, у программиста есть возможность заставить процессор (компьютер) игнорировать все прерывания или их часть.

Исполнение программного кода

2014-09-02

2014-09-02 2344

2344