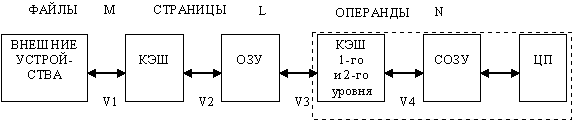

Наиболее распространенной для однопроцессорных систем является схема линейной иерархии памяти.

Рис.1. Схема иерархии памяти однопроцессорных систем

Каждый уровень служит для согласования менее быстродействующих устройств памяти с более быстродействующими

КЭШ первого и второго уровней входит в структуру центрального процессора. Обмен данными между процессором и сверхоперативным запоминающим устройством СОЗУ осуществляется словами.

На каждом уровне иерархии необходимо так организовать передачу данных, чтобы общий объем передаваемых в единицу времени данных был равен или превышал запросы процессора.

Пусть M - количество обращений в единицу времени к одному файлу

L - количество обращений в единицу времени к одной странице

N - количество обращений в единицу времени к одному операнду

V1, V2, V3, V4 -- соответственно

скорости передачи данных на разных уровнях иерархии памяти.

Значения M, N, L определяются программным обеспечением вычислительной системы и алгоритмом работы программы.

Для согласования скоростей передачи данных необходимо выполнить соотношение:

V4 / V1  N / M,

N / M,

соответственное согласование должно происходить на каждой ступени иерархии.

Аппаратная сложность определяется общим количеством программ и общим количеством страниц которое может обслуживать система. С развитием архитектуры компьютера и ростом сложности выполняемых программ возрастает требуемый объем памяти.

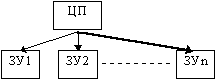

Центральная схема иерархии памяти:

Рис.2. Центральная схема иерархии памяти

Центральная схема иерархии памяти используется, если к процессору подключается несколько внешних запоминающих устройств, требующих автономной работы.

2014-09-02

2014-09-02 1411

1411