С развитием вычислительной техники и ростом разрядности системной шины изменялась система адресации и доступное процессору адресное пространство.

Логическая структура памяти персонального компьютера обусловлена особенностями системы адресации процессоров семейства Ix86. Процессоры 8086/88 имели доступное адресное пространство 1 Мбайт (20- битная шина адреса). Эти процессоры использовали сегментную модель памяти, унаследованную и следующими моделями в реальном режиме.

Согласно этой модели исполнительный (линейный) адрес вычисляется по формуле Addr = Seg + Offset, где Seg и Offset - содержимое сегментного и адресного регистров. Таким образом, обеспечивался доступ к адресному пространству Addr = 00000 - FFFFFh при помощи пары 16-битных регистров.

Заметим, что при Seg = FFFFh и Offset = FFFFh данная формула дает адрес 10FFEFh, но ввиду 20-битного ограничения на шину адреса эта комбинация в физической памяти указывает на 0FFEFh. Таким образом, адресное пространство как бы сворачивается в кольцо с небольшим "нахлестом".

Начиная с процессора 80286, шина адреса была расширена до 24 бит, а впоследствии (386DX, 486 и выше) до 32 и 36 (у процессоров P6), 64 разряда имеет шина адреса у современных процессоров.

В реальном режиме процессора, применяется сегментная модель памяти и формально доступен лишь 1 Мбайт памяти. Однако выяснилось, что в работе процессоров 80286 в реальном режиме (режим эмуляции работы процессора 8086) была обнаружена ошибка. Единица в бите A20, которая отбрасывалась в процессорах 8086/88, теперь попадала на шину адреса, и в результате максимально доступный линейный адрес в реальном режиме достиг 10FFEFh. Появилась возможность использовать в реальном режиме дополнительные 64 К байт оперативной памяти. В эту область (100000h - 10FFEFh), названную "высокой памятью" - High Memory Area (HMA), стали помещать часть операционной системы. Для обеспечения полной совместимости с процессором 8086/88 в схему персонального компьютера ввели вентиль линии A20 шины адреса - GateA20, который либо пропускает сигнал от процессора, либо принудительно обнуляет линию A20 системной шины адреса. Более старшие биты такой "заботы" не требуют, поскольку переполнение при суммировании 16-битных компонентов адреса по данной схеме до них не распространяется.

Управление этим вентилем подключили к свободному программно-управляемому выходному биту 1 контроллера клавиатуры 8042, ставшего стандартным элементом архитектуры персонального компьютера. Предполагалось, что этим вентилем часто пользоваться не придется, но оказалось, что переключение вентиля в многозадачных ОС, часто переключающих процессор между защищенным режимом и реальным режимом контроллером клавиатуры выполняется слишком медленно.

Появились методы быстрого переключения вентиля, специфичные для различных реализаций системных плат (например, через порт 92h). Кроме того, иногда использовали и аппаратную логику быстрого декодирования команды на переключение бита, поступающую к контроллеру клавиатуры.

Для определения способа переключения в утилиту CMOS Setup ввели соответствующие параметры, позволяющие выбрать между стандартным, но медленным способом и менее стандартизованным, но быстрым, в зависимости от используемого программного обеспечения.

Для упрощения внешних схем в процессоры, начиная с 486, ввели и вентиль GateA20 с соответствующим внешним управляющим выводом.

32-разрядные процессоры позволили организовать режим, называемый "большим реальным", в котором инструкции выполняются как в реальном, но доступны все 4 гигабайта памяти (для 32- разрядного адреса). Этот режим стали использовать в игровых программах, целиком захватывающих все ресурсы компьютера.

Основную часть адресного пространства занимает оперативная память. Объем установленной оперативной памяти определяется тестом POST при начальном включении компьютера, начиная с младших адресов. Натолкнувшись на отсутствие памяти (ошибку), тест останавливается на достигнутом и сообщает системе объем реально работающей памяти.

Распределение памяти персонального компьютера, непосредственно адресуемой процессором

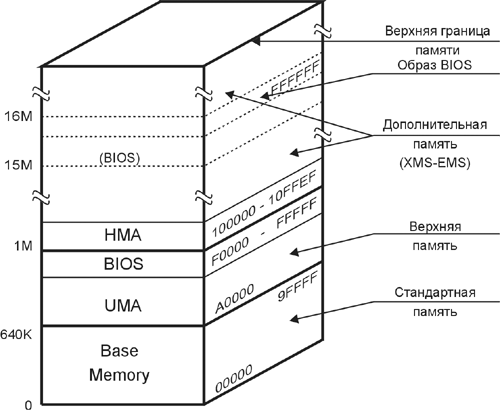

Распределение памяти персонального компьютера, непосредственно адресуемой процессором (рис.1), представляется следующим образом.

- 00000h-9FFFFh - Conventional (Base) Memory, 640 Кбайт - стандартная (базовая) память, доступная DOS и программам реального режима.

- A0000h-FFFFFh - Upper Memory Area (UMA), 384 Кбайт - верхняя память, зарезервированная для системных нужд. В ней размещаются области буферной памяти адаптеров (например, видеопамять) и постоянная память (BIOS с расширениями).

- Память выше 100000h - Extended Memory - дополнительная (расширенная) память, непосредственно доступная только в защищенном (и в "большом реальном") режиме для компьютеров с процессорами 286 и выше. В ней выделяется область 100000h-10FFEFh - высокая память, HMA, - единственная область расширенной памяти, доступная 286+ в реальном режиме при открытом вентиле Gate A20.

Область памяти выше первого мегабайта будем называть дополнительной памятью. Ее объем у современных компьютеров указывается строкой Extended Memory xxxxx Kbyte в таблице, выводимой после прохождения теста POST, и в меню стандартной конфигурации CMOS Setup.

Вышеприведенное разделение памяти актуально только для приложений и операционных систем реального режима типа MS-DOS. Для ОС защищенного режима доступна вся оперативная память.

Рис.1. Распределение памяти PC

Для компьютеров класса AT-286 с 24-битной шиной адреса верхняя граница оперативной памяти определялась- FDFFFFh (максимальный размер 15,9 Мбайт). Область FE0000h-FFFFFFh - область ПЗУ BIOS (ROM BIOS Area), обращение к этой области эквивалентно обращению к ROM BIOS по адресам 0E0000h-0FFFFFh.

Для 386+ процессоров и 32-битной шины адреса теоретическая верхняя граница - 4 Гбайт, а для P6 - 64 Гбайт (36-битная шина адреса), для современных процессоров верхней границы практически не существует. В компьютерах с 32-разрядной шиной адреса образ BIOS дополнительно проецируется в адреса FFFE0000h-FFFFFFFFh.

Реально современные системные платы позволяют установить до 512-2048 Мбайт ОЗУ, для серверных платформ это не предел. Обращение по адресам, превышающим границу установленной оперативной памяти (или максимально возможного объема), транслируется на шину PCI, которая имела 32-битную адресацию (теперь 64- битную).

Компьютеры, использующие режим системного управления SMM (System Management Mode), имеющийся у большинства процессоров последних поколений, имеют еще одно адресное пространство памяти - SMRAM. Это адресное пространство доступно процессору только в режиме обработки прерывания от системы управления SMI. Память SMRAM может представлять собой часть физической оперативной памяти, или может быть реализована и специальной микросхемой энергонезависимой памяти. Ее размер может варьироваться в диапазоне от 32 Кбайт (минимальные потребности SMM) до 4 Гбайт. SMRAM располагается, начиная с адреса SMIBASE (по умолчанию 30000h), и распределяется относительно адреса SMIBASE следующим образом.

- FE00h-FFFFh (3FE00h-3FFFFh) - область сохранения контекста (распределяется, начиная со старших адресов по направлению к младшим). По прерыванию SMI сохраняются почти все регистры процессора, но сохранение регистров FPU (АЛУ с плавающей точкой) не производится.

- 8000h (38000h) - точка входа в обработчик (SMI Handler).

- 0-7FFFh (30000h-37FFFh) - свободная область.

2014-09-02

2014-09-02 2555

2555